人工智能技術日漸普及,廣泛運用于解決當今的各種復雜問題,尤其是那些涉及海量數(shù)據的分析和相應決策等單靠人力難以應對的棘手難題。換句話說,在應對半導體設計、測試和制造過程中的復雜挑戰(zhàn)時,AI堪稱理想助手。

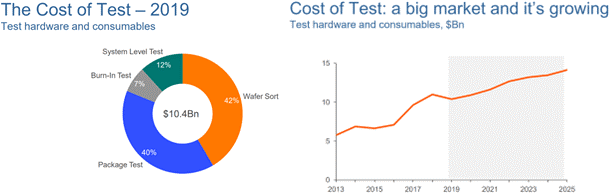

在消費、高性能計算(HPC)和汽車等多個領域,為確保篩選出可靠的器件,需要對所采用的先進節(jié)點技術和異構集成展開測試,而這會導致制造測試成本大大飆升。相關測試成本中包含不同階段的生產測試成本,其中包括晶圓分選測試、封裝測試(ATE)、老化測試和系統(tǒng)級測試(SLT)。如圖1所示,半導體行業(yè)的測試支出高達數(shù)十億美元。2019年的測試總成本為104億美元,預計到2025年將增至近150億美元。

制造測試成本與每個階段花費的測試時間成正比,而其中掃描(ATPG)測試向量等結構測試占用了大部分測試時間。為了進一步降低百萬分比缺陷率(DPPM),測試向量的數(shù)量和測試向量所占機臺內存的大小都呈指數(shù)級增長。傳統(tǒng)的固定型故障模型 (Stuck at fault model)和跳變延時故障模型(transition delay fault model)已經無法滿足期望達到的DPPM目標。為此芯片測試需要更多的測試向量并使用更先進的故障模型(Cell-aware, Power-aware, Slack-based fault mode)來檢測更多的制造缺陷。對于大批量制造(HVM)的測試成本來說,省下的每一秒鐘都至關重要。同時,可測性設計/診斷/良率團隊以及產品和測試開發(fā)團隊正不斷尋找創(chuàng)新型方案來進一步降低測試成本。

▲圖1VLSI Research對測試成本的預測。(資料來源:VLSI PP Master (swtest.org))

如何以更少的測試向量實現(xiàn)所需的測試覆蓋率和測試質量,這是DFT團隊持續(xù)面臨的挑戰(zhàn),通常不僅需要專家級用戶參與,還離不開漫長而繁瑣的迭代過程,以微調不同參數(shù),生成更優(yōu)ATPG向量集。此外,為進一步優(yōu)化測試向量數(shù)量并減少測試總量,還需要優(yōu)化測試構架配置,也就是調整掃描輸入、掃描輸出、掃描鏈的數(shù)量。為每個設計核心找到合適的測試配置是一項耗時費力且充滿挑戰(zhàn)的任務。

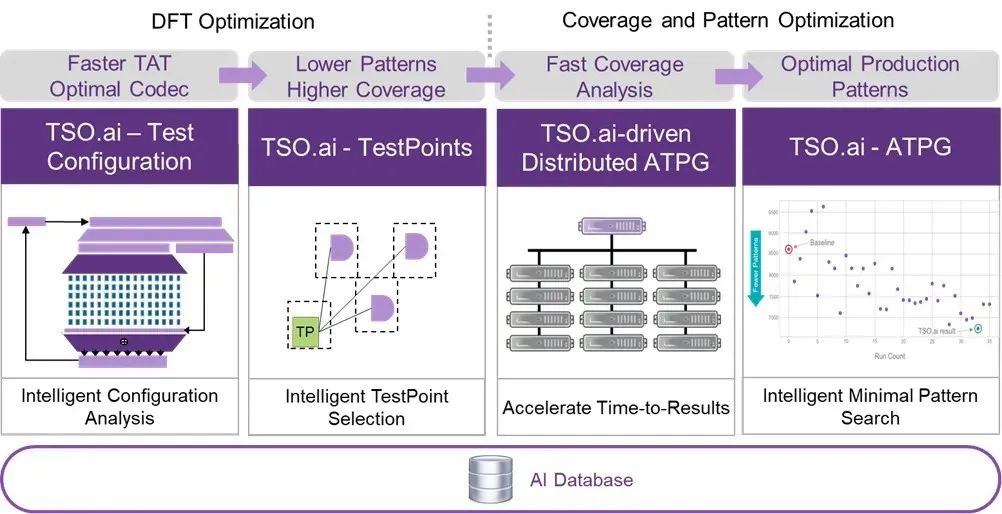

▲圖2 新思科技TSO.ai利用AI/ML實現(xiàn)先進的DFT和ATPG。

新思科技TSO.ai是一款AI驅動型測試空間優(yōu)化解決方案,它利用了AI來優(yōu)化門級網表上的ATPG向量生成,從而減少生產測試向量,進而降低測試成本。得益于此,在很多客戶的設計中,測試向量平均減少了25%。最近,新思科技增強了這個功能,讓開發(fā)者能夠通過集成新思科技TestMAX分布式ATPG功能,將測試運行分配到多臺機器和線程并加以管理,從而加速生成測試向量。然而,由于ATPG功能針對的是門級網表,其中的DFT測試構架配置在RTL階段已經確定,因此只能通過在DFT規(guī)劃階段優(yōu)化測試構架配置來進一步減少向量數(shù)量。

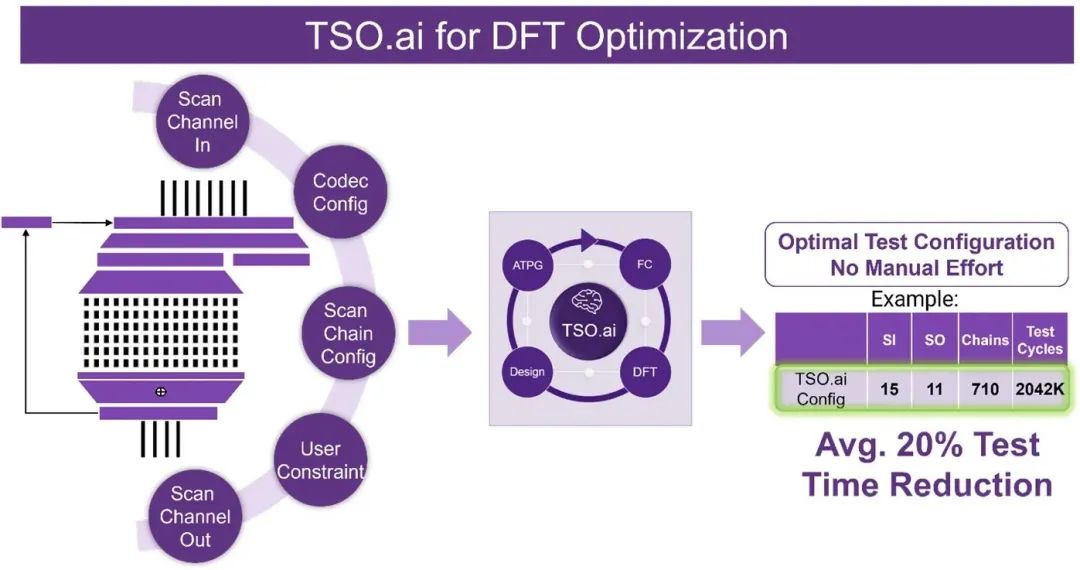

▲圖3 新思科技TSO.ai用于DFT規(guī)劃和優(yōu)化。

目前,新思科技TSO.ai在早期DFT規(guī)劃階段提供了增強功能,能夠優(yōu)化涵蓋掃描鏈數(shù)量、掃描輸入、掃描輸出在內的多個不同參數(shù)的測試配置。用戶可以在RTL階段早期快速進行假設分析,以滿足其測試覆蓋率和測試時間目標,并為綜合運行生成更優(yōu)測試配置,從而在單次綜合流程中實現(xiàn)門級網表。在傳統(tǒng)流程中,用戶必須等待綜合后的門級網表,才能評估所選測試配置的覆蓋率;然后,為了優(yōu)化測試配置,用戶必須重復掃描拼接和綜合流程,以評估其對測試覆蓋率和測試向量的影響。這是一個非常漫長的迭代過程。此外,一套測試構架配置不能適用所有設計模塊,因為優(yōu)化方案與模塊的功能設計息息相關。而對所有設計模塊重復進行試驗又非常耗費人力,可能會導致設計進度延誤數(shù)周乃至數(shù)月。

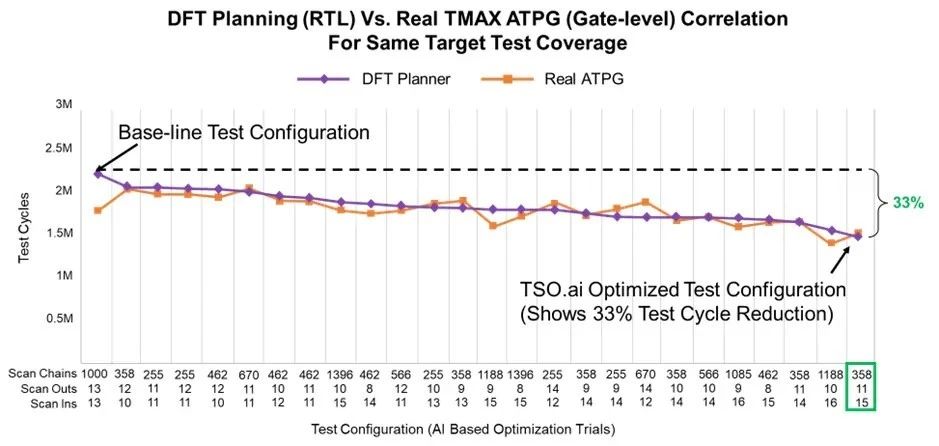

▲圖4 TSO.ai基準結果 – DFT規(guī)劃算法和門級ATPG之間的相關性。

圖4著重強調了Tso.ai在一個基準設計上的評估結果,與根據傳統(tǒng)經驗規(guī)劃的基準測試構架配置相比,基于Tso.ai規(guī)劃的DFT構架可以減少33%的測試向量數(shù)量。在相同的測試構架配置和測試覆蓋率下,新思科技TSO.ai在RTL階段評估的ATPG測試向量數(shù)量,與綜合后門級網表上實際運行的新思科技TestMAX ATPG測試數(shù)量有很好的一致性。

新思科技TSO.ai的DFT構架規(guī)劃功能平均可以減少20%的測試向量;若輔以其ATPG參數(shù)優(yōu)化的功能,則平均可以再減少25%測試向量。由此可見,新思科技TSO.ai可以顯著縮短測試時間,進而降低測試成本。此外,新思科技TSO.ai的DFT功能可以在RTL階段優(yōu)化測試配置,助開發(fā)者達到測試覆蓋率和測試向量數(shù)量目標,因此用戶無需進行多次涉及門級綜合的長周期迭代,進而能將設計周期從數(shù)月大幅縮短為幾天。

新思科技始終致力于將AI/ML應用于半導體設計。Synopsys.ai是一個全棧式AI驅動型EDA整體解決方案,可用于優(yōu)化數(shù)字和模擬器件的設計、驗證、測試與制造過程。新思科技TSO.ai是Synopsys.ai解決方案的關鍵組成部分,能夠提供更優(yōu)測試配置和測試向量,幫助開發(fā)者應對日益緊迫的設計進度和不斷增長的測試成本挑戰(zhàn)。新思科技在測試領域的AI應用仍在不斷探索和創(chuàng)新,公司計劃繼續(xù)開發(fā)關鍵解決方案,以應對未來測試的挑戰(zhàn)。

-

芯片測試

+關注

關注

6文章

172瀏覽量

21152 -

AI

+關注

關注

91文章

39793瀏覽量

301408 -

人工智能

+關注

關注

1817文章

50098瀏覽量

265381 -

新思科技

+關注

關注

5文章

957瀏覽量

52900

原文標題:AI如何助力芯片測試突破成本和時間的雙重挑戰(zhàn)?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

加快MIMO測試速度和降低測試成本的方法

什么是測試成本?(如測試測量 設備、自動元器件處理設備等)

新思科技發(fā)布業(yè)界首款全棧式AI驅動型EDA解決方案Synopsys.ai

利用測試排序儀器降低測試成本

助力AI算法芯片化 新思科技推出ASIP Designer

使用校準降低衛(wèi)星設計和測試成本

是德科技推出光測試解決方案,助力收發(fā)信機制造商縮短測試時間、降低測試成本

TSO.ai芯片測試空間優(yōu)化方案:打通AI應用“最后一公里”

本周五|TSO.ai:打通AI應用“最后一公里”,降低芯片測試成本

新思科技探索AI+EDA的更多可能性

新思科技攜手微軟借助AI技術加速芯片設計

現(xiàn)代晶圓測試:飛針技術如何降低測試成本與時間

新思科技TSO.ai助力解決芯片測試成本和時間挑戰(zhàn)

新思科技TSO.ai助力解決芯片測試成本和時間挑戰(zhàn)

評論