主從觸發(fā)器,也被稱為主從同步觸發(fā)器或主從鎖存器觸發(fā)器,是一種在數字電路設計中廣泛使用的觸發(fā)器類型。它主要用于防止亞穩(wěn)態(tài)現象,提高電路的穩(wěn)定性和可靠性。

- 主從觸發(fā)器的工作原理

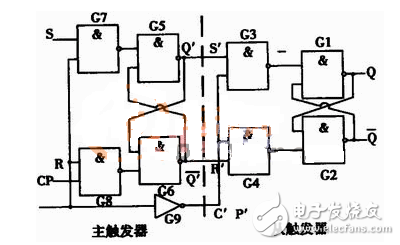

主從觸發(fā)器由兩個觸發(fā)器組成,一個是主觸發(fā)器,另一個是從觸發(fā)器。主觸發(fā)器負責接收輸入信號,從觸發(fā)器負責存儲輸出信號。在主觸發(fā)器接收到輸入信號后,它會將信號傳遞給從觸發(fā)器,從觸發(fā)器在接收到信號后,將信號存儲起來,并輸出給后續(xù)電路。

主從觸發(fā)器的工作原理可以分為以下幾個步驟:

1.1 輸入信號的接收:主觸發(fā)器接收輸入信號D。

1.2 信號的傳遞:主觸發(fā)器將輸入信號D傳遞給從觸發(fā)器。

1.3 信號的存儲:從觸發(fā)器接收到信號后,將其存儲起來。

1.4 信號的輸出:從觸發(fā)器將存儲的信號輸出給后續(xù)電路。

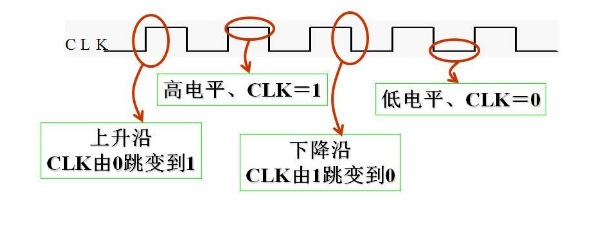

1.5 信號的同步:主觸發(fā)器和從觸發(fā)器之間通過同步機制保證信號的一致性。

- 主從觸發(fā)器的特點

2.1 防止亞穩(wěn)態(tài)現象:主從觸發(fā)器通過主從結構的設計,可以有效防止亞穩(wěn)態(tài)現象的發(fā)生。亞穩(wěn)態(tài)是指觸發(fā)器在接收到輸入信號后,輸出信號在一段時間內不穩(wěn)定,無法確定其狀態(tài)。主從觸發(fā)器通過主觸發(fā)器和從觸發(fā)器的同步機制,確保輸出信號的穩(wěn)定性。

2.2 提高電路的穩(wěn)定性:主從觸發(fā)器通過主從結構的設計,可以提高電路的穩(wěn)定性。在主觸發(fā)器接收到輸入信號后,從觸發(fā)器可以在短時間內完成信號的存儲和輸出,從而減少信號在電路中的傳播延遲,提高電路的穩(wěn)定性。

2.3 降低功耗:主從觸發(fā)器在設計時,可以采用低功耗技術,降低電路的功耗。例如,可以采用CMOS工藝設計主從觸發(fā)器,利用CMOS工藝的低功耗特性,降低電路的功耗。

2.4 提高電路的可靠性:主從觸發(fā)器通過主從結構的設計,可以提高電路的可靠性。在主觸發(fā)器接收到輸入信號后,從觸發(fā)器可以在短時間內完成信號的存儲和輸出,從而減少信號在電路中的傳播延遲,提高電路的可靠性。

- 主從觸發(fā)器的應用

主從觸發(fā)器在數字電路設計中有廣泛的應用,主要包括以下幾個方面:

3.1 存儲器設計:主從觸發(fā)器可以用于存儲器的設計,例如RAM、ROM等。在存儲器設計中,主從觸發(fā)器可以用于存儲數據,提高存儲器的穩(wěn)定性和可靠性。

3.2 寄存器設計:主從觸發(fā)器可以用于寄存器的設計,例如數據寄存器、地址寄存器等。在寄存器設計中,主從觸發(fā)器可以用于存儲數據,提高寄存器的穩(wěn)定性和可靠性。

3.3 時鐘電路設計:主從觸發(fā)器可以用于時鐘電路的設計,例如分頻器、相位鎖定環(huán)等。在時鐘電路設計中,主從觸發(fā)器可以用于同步信號,提高時鐘電路的穩(wěn)定性和可靠性。

3.4 異步電路設計:主從觸發(fā)器可以用于異步電路的設計,例如異步計數器、異步寄存器等。在異步電路設計中,主從觸發(fā)器可以用于同步信號,提高異步電路的穩(wěn)定性和可靠性。

- 主從觸發(fā)器的設計

4.1 選擇觸發(fā)器類型:在設計主從觸發(fā)器時,需要選擇合適的觸發(fā)器類型。常見的觸發(fā)器類型包括SR觸發(fā)器、D觸發(fā)器、JK觸發(fā)器等。根據電路的需求和性能要求,選擇合適的觸發(fā)器類型。

4.2 設計主觸發(fā)器:主觸發(fā)器負責接收輸入信號,并將信號傳遞給從觸發(fā)器。在設計主觸發(fā)器時,需要考慮信號的接收、傳遞和同步機制。

4.3 設計從觸發(fā)器:從觸發(fā)器負責存儲輸出信號,并將其輸出給后續(xù)電路。在設計從觸發(fā)器時,需要考慮信號的存儲、輸出和同步機制。

4.4 設計同步機制:主從觸發(fā)器的同步機制是保證信號一致性的關鍵。在設計同步機制時,需要考慮信號的同步方式、同步時間等。

4.5 優(yōu)化電路性能:在設計主從觸發(fā)器時,需要考慮電路的性能優(yōu)化。例如,可以采用低功耗技術、高速設計技術等,提高電路的性能。

-

鎖存器

+關注

關注

8文章

956瀏覽量

44915 -

主從觸發(fā)器

+關注

關注

0文章

13瀏覽量

6634 -

數字電路

+關注

關注

193文章

1651瀏覽量

83337 -

輸入信號

+關注

關注

0文章

559瀏覽量

13179

發(fā)布評論請先 登錄

JK觸發(fā)器,JK觸發(fā)器是什么意思

D觸發(fā)器,D觸發(fā)器是什么意思

主從觸發(fā)器,主從觸發(fā)器的原理和特點有哪些?

觸發(fā)器介紹及分類

邊沿觸發(fā)器波形圖

主從rs觸發(fā)器波形圖介紹

主從觸發(fā)器是一種能防止什么現象的觸發(fā)器

主從觸發(fā)器是一種能防止什么現象的觸發(fā)器

評論