一站式PCBA智造廠家今天為大家講講晶振在PCB板上如何布局?PCB板時(shí)鐘晶振及相關(guān)元件布線原則。晶振布局在PCB設(shè)計(jì)中非常關(guān)鍵,因?yàn)榫д袷请娮酉到y(tǒng)中用于提供時(shí)鐘信號(hào)的重要元件。以下是一些建議,幫助您在PCB電路板設(shè)計(jì)中有效布局晶振:

PCB板時(shí)鐘晶振及相關(guān)元件布線原則

1. 靠近芯片: 將晶振盡可能靠近需要時(shí)鐘信號(hào)的芯片。短的連線長(zhǎng)度可以減小時(shí)鐘信號(hào)的傳播延遲,降低干擾的可能性。

2. 保持清晰的時(shí)鐘路徑: 在設(shè)計(jì)時(shí)鐘路徑時(shí),確保路徑是短而直接的,減小信號(hào)傳播的延遲。避免路徑中有鋸齒狀或彎曲的部分,以減小信號(hào)傳播的不確定性。

3. 地平面和功耗平面: 確保在晶振周圍存在良好的地平面。通過在PCB的底層或者內(nèi)層添加地平面,可以有效減小信號(hào)引入和輻射噪聲。同時(shí),維持良好的功耗平面也是重要的。

4. 避免共享時(shí)鐘線: 盡量避免將時(shí)鐘線與其他高速信號(hào)線共享,以減小互相的干擾。如果共享是不可避免的,確保采取適當(dāng)?shù)钠帘未胧热缡褂玫貙踊蛘咝盘?hào)層之間的屏蔽。

5. 降低噪聲: 在晶振的輸入和輸出引腳周圍,使用適當(dāng)?shù)?a href="http://www.3532n.com/tags/電容/" target="_blank">電容進(jìn)行去耦,以降低電源噪聲。還可以考慮使用電源濾波器和隔離器。

6. 避免電磁干擾: 盡量避免將晶振布局在可能受到電磁干擾的區(qū)域,比如高功率驅(qū)動(dòng)的區(qū)域。

7. 考慮差分布局: 如果使用差分時(shí)鐘信號(hào),確保晶振與接收器之間的差分線長(zhǎng)度相等,以保持信號(hào)的相位一致性。

8. 阻抗匹配: 保持時(shí)鐘線的阻抗匹配,以避免信號(hào)反射和功耗。使用差分配線來提高抗干擾能力。

最終,在進(jìn)行PCB設(shè)計(jì)時(shí),最好的方法是結(jié)合理論知識(shí)和實(shí)際經(jīng)驗(yàn)。通過使用仿真工具和實(shí)際測(cè)量,可以驗(yàn)證設(shè)計(jì)是否滿足性能要求。

關(guān)于晶振在PCB板上如何布局?PCB板時(shí)鐘晶振及相關(guān)元件布線原則的知識(shí)點(diǎn),想要了解更多的,可關(guān)注領(lǐng)卓PCBA,如有需要了解更多PCB打樣、SMT貼片、PCBA加工的相關(guān)技術(shù)知識(shí),歡迎留言獲取!

審核編輯 黃宇

-

晶體振蕩器

+關(guān)注

關(guān)注

9文章

749瀏覽量

33238 -

PCB

+關(guān)注

關(guān)注

1文章

2307瀏覽量

13204

發(fā)布評(píng)論請(qǐng)先 登錄

晶體振蕩器與晶體諧振器有哪些關(guān)聯(lián)呢?

晶體振蕩器的主要作用及其在現(xiàn)代社會(huì)中的應(yīng)用

CS-23系列低相位噪聲恒溫晶體振蕩器

當(dāng)系統(tǒng)和用戶交換機(jī)沒有連接 HXT(高速晶體振蕩器)時(shí),應(yīng)該怎么做?

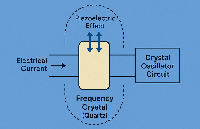

晶體振蕩器是如何工作的?——從物理到工程實(shí)踐

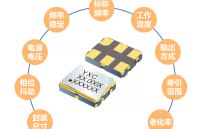

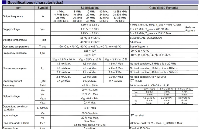

壓控晶體振蕩器參數(shù)及選型

XTAL晶體振蕩器是怎么工作的?一文看懂壓電原理與工程應(yīng)用

FX3晶體振蕩器上電后停止,怎么解決?

晶體振蕩器如何失效?

什么是壓控晶體振蕩器

低功耗石英晶體振蕩器的工作原理和應(yīng)用場(chǎng)景

27MHz HCSL晶體振蕩器選型與PHY對(duì)接設(shè)計(jì)指南

愛普生SG2016CAN晶體振蕩器在工業(yè)相機(jī)中的精準(zhǔn)時(shí)鐘之選

愛普生SG3225CAN有源石英晶體振蕩器的特點(diǎn)和多領(lǐng)域應(yīng)用

晶體振蕩器 PCB 布局設(shè)計(jì)指南

晶體振蕩器 PCB 布局設(shè)計(jì)指南

評(píng)論