共讀好書

隨著銅的有效性不斷降低,芯片制造商對新互連技術的關注度正在不斷提高,為未來節點和先進封裝的性能提升和減少熱量的重大轉變奠定了基礎。

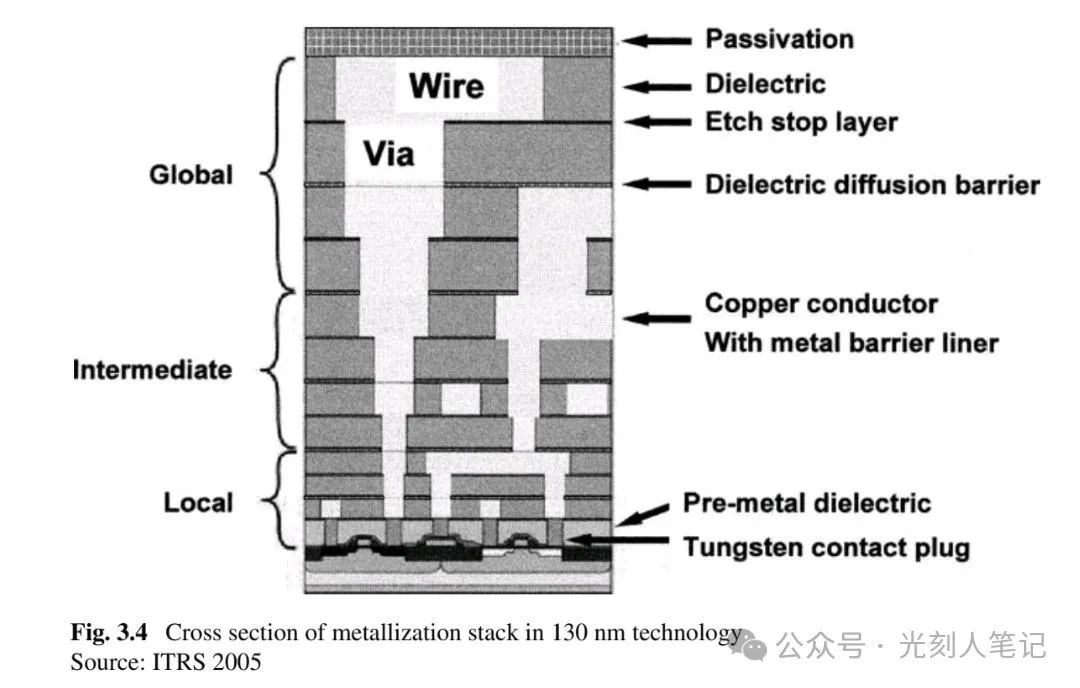

1997 年引入銅互連顛覆了當時標準的鎢通孔/鋁線金屬化方案。雙鑲嵌集成(Dual damascene integration schemes )方案用電鍍和 CMP 等“濕”工藝取代了等離子蝕刻和沉積等“干”步驟。當時,制造商正努力在更復雜的互連結構面前盡量減少 RC 延遲。

近三十年后,半導體行業也處在類似的十字路口。不斷縮小的線路尺寸正在接近銅的電子平均自由程(electron mean free path)。阻擋層(Barrier layers)正在消耗總可用線路寬度的更大份額。對銅替代品的需求正在增長。然而,與大多數根本性變化一樣,制造商希望盡可能推遲這一變化。

在最近的 IEEE 互連技術會議上公布的結果表明,銅的優化機會仍然存在。

銅互連的歷史

互連線,即在晶體管之間傳輸電流的導線,是一個特別令人擔憂的領域。隨著芯片變得越來越緊密,互連線在更小的尺寸下需要承擔更大的任務。在通線面世之前,鋁是互連線的理想材料,也是當時的行業標準,但它的導電能力正迅速接近極限。此外,鋁線更容易斷裂。

銅線恰逢其會面世了。

其實大家對鋁的局限在很早就知道,所有人也知道鋁的時代顯然已經屈指可數,但盡管經過了幾十年的研究,仍然沒有人找到如何安全地將銅融入芯片設計的方法。主要的障礙是克服銅與硅相互作用產生的令人不安的副產品。與鋁不同,銅會有效地泄漏原子并破壞硅的電性能,從而可能導致硅無法使用。“銅被認為是半導體器件的殺手,”IBM 院士兼銅應用專家 Lubomyr Romankiw 在IBM 研究雜志中說道。“傳統觀點是盡可能遠離銅。”

要使銅互連可行,需要解決三個問題:確定如何最好地將其化學沉積在晶圓上,如何保護硅免受毒害,以及如何在芯片上物理布置銅。

IBM 測試了幾種施加銅的方法,包括從氣體懸浮液中沉積固體銅,以及使用電荷將液體中的銅離子吸收到硅上,這一過程稱為化學鍍。雖然前一種方法(稱為濺射)最初看起來很有希望,但科學家們最終選擇了第三種選擇,即電解鍍,這是一種不切實際但很熟悉的方法——而且出人意料地成功了。

為了保護硅片,IBM 科學家采用了該公司在 20 世紀 80 年代中期研究的一種穩定金屬作為阻擋雜散銅離子的擴散屏障。該公司設計了一種將擴散屏障與銅一起沉積在晶圓上的方法。研究人員借用了 IBM 在 20 世紀 80 年代初為其DRAM項目發明的一種蝕刻技術。

這項技術以敘利亞大馬士革古冶金學家的名字命名,他們完善了金屬鑲嵌工藝,這種用于蝕刻銅互連線和通孔的所謂雙鑲嵌方法對該項目的成功至關重要。通過從典型制造工藝中去除沉積和拋光步驟,這種方法為尋求可行的銅解決方案創造了巨大的經濟激勵。

于是,到了1997 年,IBM 推出了一種由銅制成的新型半導體,震驚了世界。銅這種金屬在芯片制造領域的成功應用,是科學家們 30 多年來一直未能實現的。這一突破帶來了速度更快、成本更低的芯片,并為微處理器的發展開辟了新的路線圖。由于銅線的耐用性更強、可靠性高出 100 倍,而且可以縮小到更小的尺寸,因此,從智能手機到汽車,銅線的替代帶來了具有計算能力的設備爆炸式增長。

充分利用銅

不過,在面試近三十年后,問題凸顯。

隨著互連線縮小,接口及其特性與電氣性能的關系比本體材料特性更密切。三星半導體高級工程師 Jongmin Baek 和他的同事專門研究了如何優化銅所需的阻擋層和蝕刻停止層來提高整體性能。例如,在接觸金屬間隔測試工具中(contact metal-spacer test vehicle),該團隊使用側壁等離子預處理(sidewall plasma pre-treatment )將側壁阻擋層(sidewall barrier )厚度減少了三分之一,從而將接觸電阻提高了 2%。

三星研究人員特別關注了通孔底部屏障(via bottom barrier)。由于金屬通孔位于金屬線上,因此不需要該屏障作為電絕緣體(electrical insulator )或擴散屏障(diffusion barrier)。它僅作為側壁沉積的產物而存在,但它可以占通孔電阻的 60% 以上。選擇性沉積方法通常用于減少通孔底部沉積。在 Baek 的工作中,聚合物抑制劑相對于常用的自組裝單層提高了選擇性,使電阻降低了 20%。

現代互連方案依賴于各種摻碳氧化物來實現電路 RC 延遲的“C”部分。密度較低的材料具有較低的介電常數(k),因此具有吸引力。三星的 Kang Sub Yim 的其他工作考慮了等離子蝕刻導致電介質表面碳的消耗。低 k 電介質的蝕刻損傷會增加有效介電常數,從而增加電路的電容。密度較高的材料(通常 k 值高于 3.0)對等離子蝕刻損傷的抵抗力更強,這可能使它們在 30nm 以下特征中的有效 k 值更低。對于小于約 30nm 的特征,表面碳消耗的影響大于體積介電常數。

Yim 團隊還利用表面硅化來修復蝕刻損傷。然而,Baek 指出,對電介質側壁進行表面處理可能會污染通孔底部的裸露金屬。相反,Baek 團隊采用了專有化學方法的熱恢復工藝,將蝕刻后的 Si-OH 終止表面恢復為 Si-CH3終止表面。

銅線的完全封裝(Full encapsulation)包括一個金屬蓋層(通常是鈷)以減少電遷移,然后是絕緣蝕刻停止層和阻擋層。由于間距縮小,這些層占總線厚度的比例越來越大。為了改善與蓋層的界面,Baek 在蝕刻停止層沉積之前添加了等離子體預處理。結果,他們發現銅線中的應力減少了 30%,通孔電阻減少了 10%。另外,Yim 也取得了類似的結果。

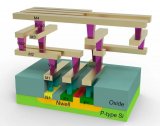

釕通孔,然后是線路

雖然所有這些發展都很有希望,但仍需要一種長期的銅后繼者。由于通孔尺寸小、數量多,它正在主導整體互連電阻。在前四五個互連層中,金屬線非常短,不會產生太大的電阻。因此,一種替代方案是使用過渡混合金屬化方案,將銅線與鎢、釕或鉬等材料結合起來用于通孔。

imec的模擬表明,在互連堆棧的前四層使用釕通孔可將總電阻降低多達 60%。為了將釕通孔與銅線集成,他們建議僅在介電側壁上沉積 TaN 阻擋層,將釕直接置于裸露的銅上。任何此類方案都需要良好的介電表面鈍化和對釕選擇性的良好控制。集群工具工藝是首選,因為從裸露的銅上去除原生氧化物會損壞介電鈍化。

由于釕可以通過多種方式沉積或蝕刻,并且不需要阻擋層,因此它為更靈活的集成方案打開了大門。例如,imec 研發工程師 Giulio Marti 和他的同事對三種不同的完全自對準通孔工藝進行了基準測試。

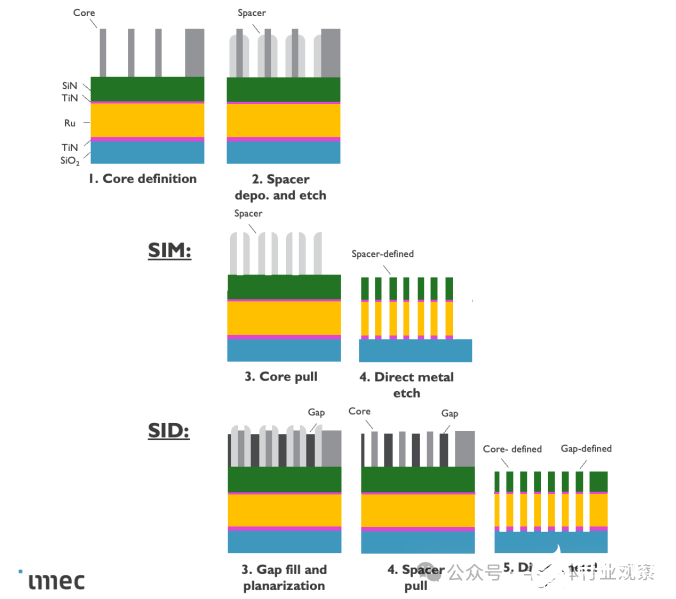

第一種也是最傳統的工藝使用 EUV 自對準雙重圖案化,該工藝創建的間隔線用于定義金屬線 (SADP-SIM)。將間隔圖案轉移到 SiN 硬掩模后,選擇性 RIE 蝕刻對釕金屬層進行圖案化,然后進行 SiO2沉積。高選擇性蝕刻將通孔開口與剩余的 SiN 特征對齊,然后進行 CVD 釕沉積以填充它們。

Marti 考慮的另外兩種方案均基于柱通孔(pillar vias),在第一層上方沉積了第二層釕層,并用蝕刻停止層將兩者隔開。在這些方案中,圖案轉移使用兩步釕蝕刻。首先,高縱橫比蝕刻在兩層中切割出所需的金屬線。然后,旋涂電介質填充這些溝槽,并在頂部放置硬掩模。色調反轉 EUV 對硬掩模進行圖案化以保護所需的通孔柱,而之前的蝕刻停止層則保護下面的金屬線。Marti 發現,兩個柱通孔方案增加了工藝步驟的數量,但增加了工藝窗口。特別是,這種方法可以防止通孔和相鄰線之間的橋接。

另一位 imec 研發工程師 Chen Wu 及其同事提出了另一種替代方案,他們使用 SADP 間隔物(而不是金屬)來定義介電特征。在這種 SADP-SID 方案中,在間隔柱之間沉積了硬掩模材料,然后將其移除。雖然這種方法增加了工藝復雜性,但這意味著金屬特征直接由掩模定義,從而為設計人員提供了更大的靈活性和對特征尺寸的控制。

但無論具體方法如何,Wu強調,優化釕蝕刻和沉積工藝至關重要。錐形釕輪廓、釕特征底部的底座以及 TiN 粘附層的不完全去除會減小相鄰線之間的間距,從而導致泄漏。

集成方案只是開始

成功的工藝集成方案需要仔細關注所有組件層。對于釕,優化過程才剛剛開始。杰克·羅杰斯 (Jack Rogers) 和 TEL 奧爾巴尼技術中心的同事研究了粘附層工藝條件對釕沉積行為的影響。PVD 和 ALD TiN 上的釕膜具有不同的晶粒取向、不同的晶粒取向分布和不同的電阻率。較大且更均勻的 Ru 晶粒似乎可以降低電阻率,至少當晶粒小于整體互連尺寸時是這樣。

盡管釕互連所需的輔助層比銅少(這是重點的一部分),但金屬蝕刻和電介質填充工藝的重新引入必將讓工藝工程師在未來幾年里忙碌不已。

審核編輯 黃宇

-

半導體

+關注

關注

339文章

31055瀏覽量

265647 -

封裝

+關注

關注

128文章

9302瀏覽量

148905

發布評論請先 登錄

數據中心互連技術演變:光進銅退的完整路徑

MACOM公司推出高密度銅互連解決方案

如何正確選用Finisar AOC/DAC提升光互連性能

從內存接口到PCIe/CXL、以太網及光互連,高速互連芯片市場分析

CMI500/CMI700系列銅厚測試儀的面銅探頭、孔銅探頭哪家好?

是德科技亮相448G全球高速銅纜創新技術與供應鏈大會

TSV工藝中的硅晶圓減薄與銅平坦化技術

立訊技術高速裸線技術如何搶占高速互連賽道

銅價瘋漲下的連接器革命:鋁代銅如何破局?

銅對芯片制造中的重要作用

從微米到納米,銅-銅混合鍵合重塑3D封裝技術格局

一文詳解銅互連工藝

XSR芯片間互連技術的定義和優勢

銅互連,尚能飯否?

銅互連,尚能飯否?

評論