格雷碼的事聊完了,后面順理成章的就是讀寫通路模塊的設計。不過在讀寫控制通路之前還要明確下另一個問題,就是空滿信號的產生位置的事情。

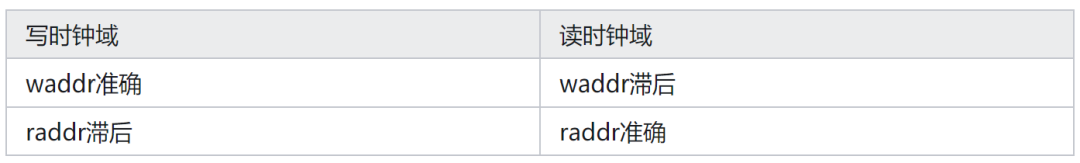

這個問題在面試時的問法是:空滿信號分別在哪個時鐘域產生?

眾所周知,信號跳變時打兩拍(或者三拍)能夠消除亞穩態,但是信號從亞穩態恢復的時候不一定恢復成0還是1。而因為格雷碼每次變化1比特的特性,可以保證即使恢復錯了也不過是錯成之前的值罷了。

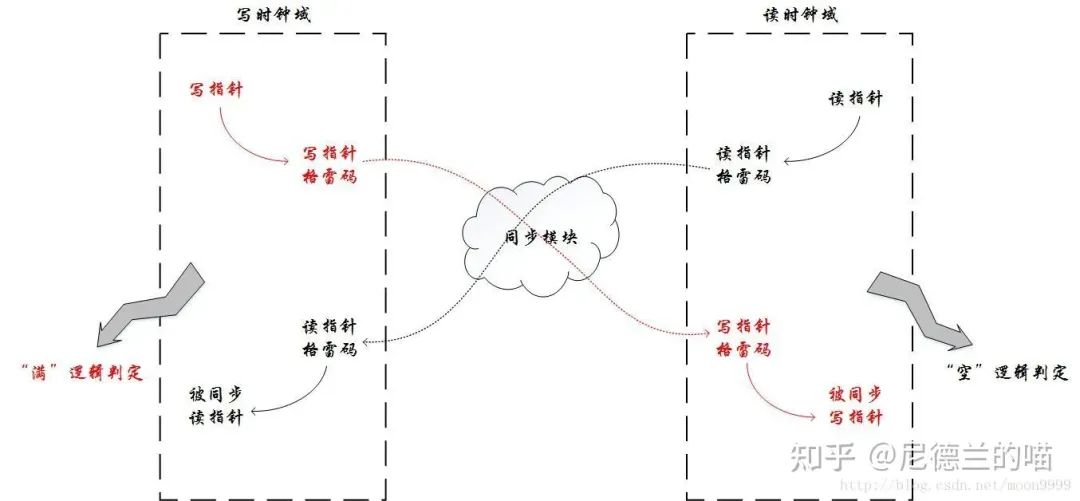

當然了即使沒有亞穩態誤恢復的問題,讀寫指針傳到對面的時鐘域去,總歸會延遲好幾拍的,所以在寫時鐘域看到的讀指針是落后于實時讀指針的,同理讀時鐘域看到的寫指針也是落后于真實的寫指針的。

那么來分析下滯后的影響,令fifo_cnt為fifo中已有的數據量計數值。

1.waddr準確,raddr滯后,那么計算得到fifo_cnt會偏大。如waddr=7,raddr=4,滯后的raddr=1,計算得到fifo_cnt為6,而實際上fifo_cnt為3;

2.waddr滯后,raddr準確,那么計算得到fifo_cnt會偏小。如waddr=7,raddr=4,滯后的waddr=5,計算得到fifo_cnt為1,而實際上fifo_cnt為3;

進一步的,如果fifo_cnt計算偏大了,對于讀和寫來說會有什么影響呢?讀可能發生功能問題,寫可能發生性能問題。讀可能發生功能問題在于,本來你里面沒數了,結果fifo_cnt算的偏大還以為有數,有數就能讀一讀就出錯了。寫可能發生性能問題在于,本來你里面沒滿呢,結果fifo_cnt算的偏大還以為滿了,滿了就不能寫本來能寫的寫不進去那性能不就降下來了么。

如果fifo_cnt計算偏小了,對于讀和寫來說會有什么影響呢?讀可能發生性能問題,寫可能發生功能問題。讀可能發生性能問題在于,本來你里面還有數,結果fifo_cnt算的偏小還以為沒數了,沒數了就不能讀了。寫可能發生功能問題在于,本來你已經滿了,結果fifo_cnt算的偏小還以為沒滿,沒滿就能寫一寫就出錯了。

所以,對于寫fifo而言,fifo_cnt計算偏小不可接收,fifo_cnt計算偏大可以接收,所以滿信號必須由準確的waddr和滯后的raddr產生,也就是在寫時鐘域產生。

對于讀fifo而言,fifo_cnt計算偏小可以接收,fifo_cnt計算偏大不可接收。所以空信號必須由滯后的waddr和準確的raddr產生,也就是在讀時鐘域產生。

審核編輯:劉清

-

fifo

+關注

關注

3文章

407瀏覽量

45872 -

格雷碼

+關注

關注

2文章

34瀏覽量

13553 -

時鐘域

+關注

關注

0文章

53瀏覽量

10057

原文標題:【芯片設計】FIFO漫談之異步FIFO空滿信號的產生位置

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

求助 FPGA 異步FIFO IP核

異步FIFO指針同步產生的問題

【鋯石A4 FPGA試用體驗】fifo實驗(2)-異步fifo

Camera Link接口的異步FIFO設計與實現

異步FIFO的設計分析及詳細代碼

基于FPGA的異步FIFO設計方法詳解

異步FIFO用格雷碼的原因有哪些

異步fifo詳解

FIFO相關信號及空滿狀態的原理說明

FIFO漫談之異步FIFO空滿信號的產生位置

FIFO漫談之異步FIFO空滿信號的產生位置

評論