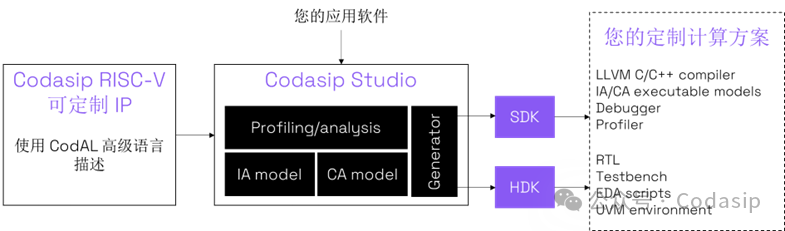

→ Codasip Studio and RISC-V 處理器核

從標準處理器核開始,無需“冷啟動”

? 基于已開發的嵌入式或應用處理器核 (如L31等)

? 高質量水準,達量產標準

? 完全符合RISC-V規范

通過Codasip Studio實現您需要的差異化

? 可配置/可定制

? 使用CodAL體系結構描述語言(類C高級語言)

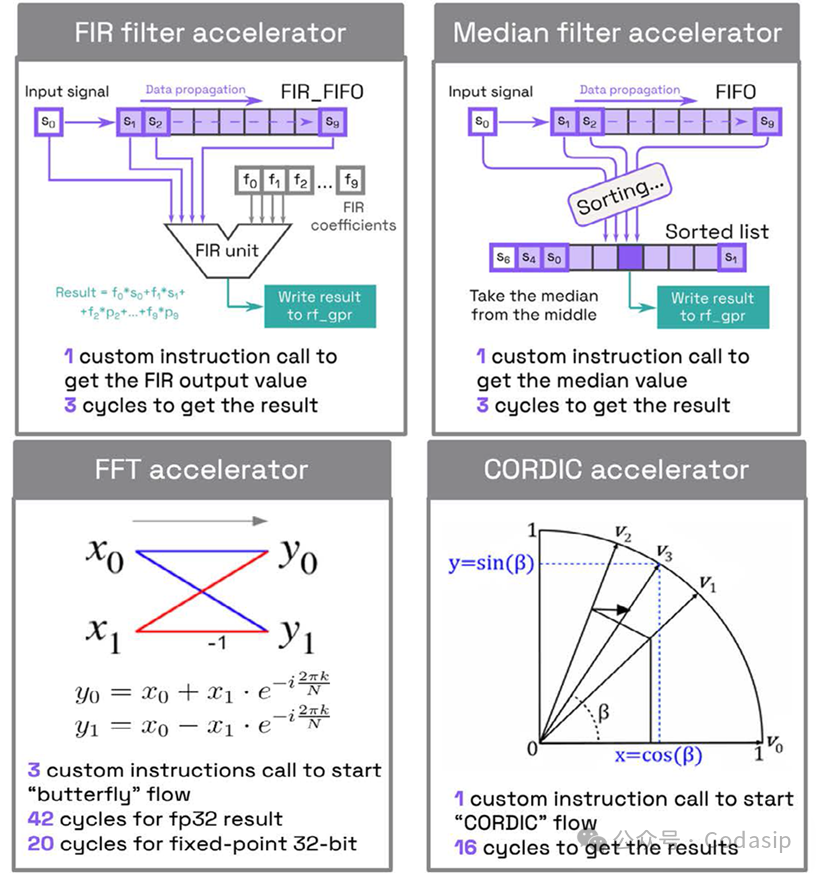

→ 用CodAL實現DSP加速器

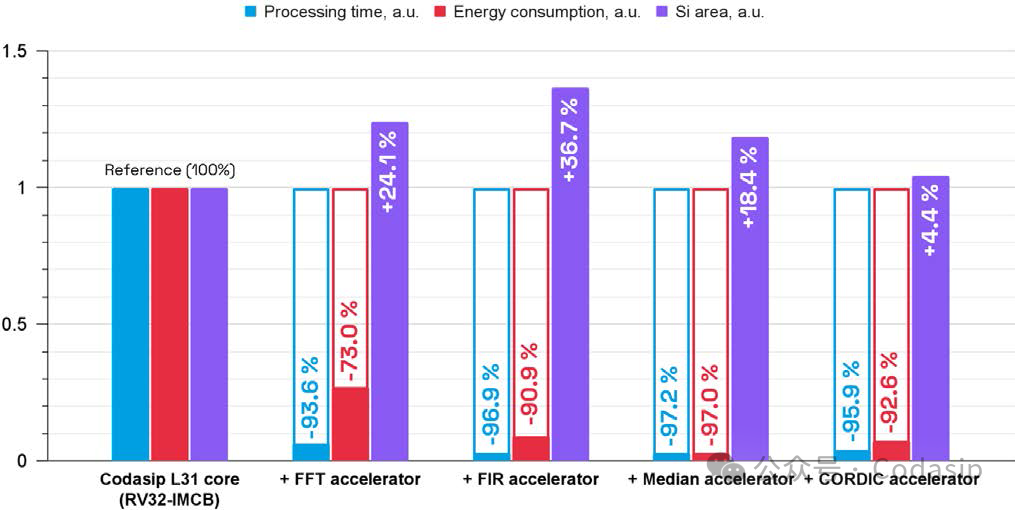

→ DSP定制如何影響PPA

基于嵌入式RISC-V核定制專用DSP,以處理如上四種代表性的DSP算法為例。性能和能耗分別提升和縮減為14.4倍和0.27倍(FFT),14.4倍和0.1倍(FIR)、30倍和0.03倍(Median filtering)和24.3倍和0.08倍(Cordic),通過增加有限的面積即得到了此效果。

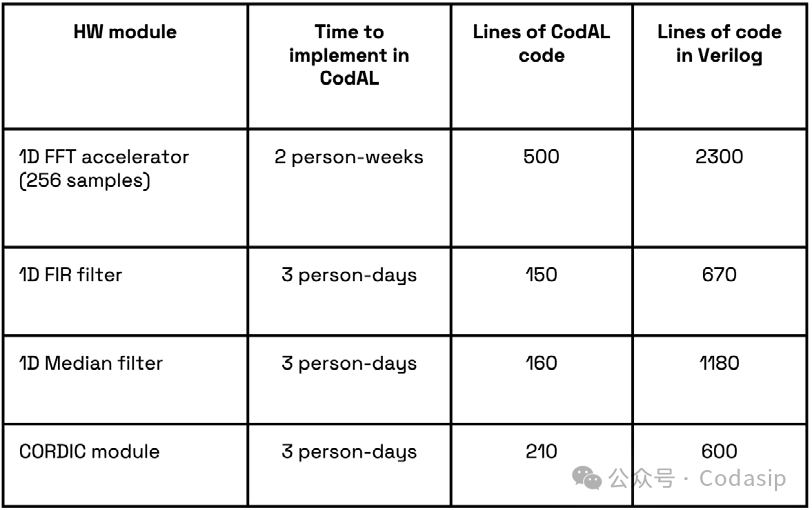

使用CodAL和Codasip Studio,通過“開箱即用”的SDK和HDK等自動生成工具,結合精練的內核描述,輕松實現RISC-V的定制,縮短產品開發周期。下表列出了實現上述的DSP定制的預估代碼量和工作量。

審核編輯:劉清

-

處理器

+關注

關注

68文章

20250瀏覽量

252213 -

dsp

+關注

關注

561文章

8244瀏覽量

366607 -

嵌入式

+關注

關注

5198文章

20442瀏覽量

333986 -

加速器

+關注

關注

2文章

839瀏覽量

40097 -

RISC-V

+關注

關注

48文章

2887瀏覽量

52988

原文標題:基于嵌入式RISC-V處理器核 輕松實現DSP擴展設計

文章出處:【微信號:Codasip 科達希普,微信公眾號:Codasip 科達希普】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

risc-v與esp32架構對比分析

重磅合作!Quintauris 聯手 SiFive,加速 RISC-V 在嵌入式與 AI 領域落地

學習RISC-V入門 基于RISC-V架構的開源處理器及SoC研究

如何入門RISC-V嵌入式

UltraSoC宣布提供業界首款RISC-V嵌入式處理器產品

專家力薦|《嵌入式系統原理與開發——基于RISC-V和Linux系統》新書發售

如何使用 RISC-V 進行嵌入式開發

PIC64GX1000 RISC-V MPU:一款面向嵌入式計算的高性能64位多核處理器

基于嵌入式RISC-V處理器核輕松實現DSP擴展設計

基于嵌入式RISC-V處理器核輕松實現DSP擴展設計

評論