今年的ISSCC會議在舊金山舉行,來自英特爾、AMD、臺積電,甚至人工智能初創(chuàng)公司的多場演講都在談論他們過去的所作所為。然而,關于他們未來的工作的演講總是吸引很多人參加。該展會還設有演示區(qū),擁有硅片可供演示的公司將在此展示他們的硬件。除了 IBM 的 NorthPole(可能會得到自己的報道)、Axelera 的新型 AI 芯片、Rebellion 的 Atomus AI 芯片等之外,英特爾還展示了其最新的 3nm 硅內(nèi)設計。

這不是 CPU 核心,而是SERDES連接。當芯片在封裝上相互通信或與外界通信時,會建立一些連接,為了使該連接快速,數(shù)據(jù)從數(shù)字轉換為模擬,然后串行化和反串行化。SER(序列化)和DES(反序列化)。PCIe 是使用 SERDES 連接的最常見接口,但 QPI 和網(wǎng)絡等其他芯片到芯片協(xié)議也需要它們。在某些計算機中,它是現(xiàn)有最快的信號 IP,旨在傳輸片外數(shù)據(jù)。在新一代基于小芯片的系統(tǒng)中,芯片之間的連接將定義可以實現(xiàn)的帶寬。因此,在過去 10 年中,我們看到了 SERDES 連接速度的增長——通道和絕對傳輸速度的增長。

例如,多年來使用 SERDES 的 PCIe 傳輸速率已從每秒 1 GB 提高到每秒 32 GB。然后,PCIe 利用多個 SERDES 鏈路(例如 x1、x2、x4、x8、x16)來倍增連接的整體帶寬。PCIe作為一種協(xié)議引入了編碼開銷,因此SERDES鏈路的傳輸速率實際上高于PCIe的報價帶寬,這對于SERDES鏈路類型來說是常見的。

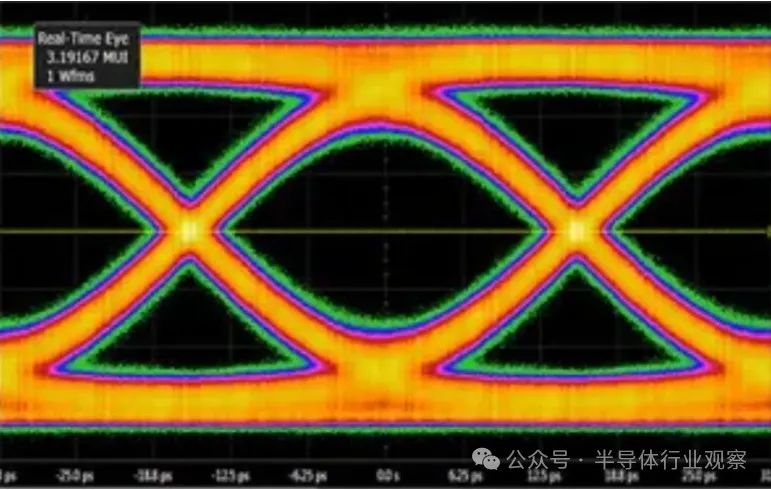

到目前為止,我一直在假設 SERDES 鏈接只是發(fā)送 1 和 0,例如傳統(tǒng)的二進制模式。在模擬世界中,這稱為NRZ,或不歸零。這意味著信號可以是 1 或 0,在開發(fā)高速鏈路時,確保能夠區(qū)分這兩者至關重要。該領域的工程師和公司通常喜歡展示“眼圖”,以表明其設計中 1 和 0 之間的差異。為了得到這個圖,他們疊加了數(shù)千甚至數(shù)百萬個連接周期,顯示 1 或 0 不會互相干擾。

增加鏈路帶寬(例如 8 GB 鏈路)的另一種方法是每次傳輸編碼更多位。我們現(xiàn)在不再關注 NRZ,而是關注脈沖幅度調(diào)制 (PAM)。展示這一點的最簡單方法是一個示例,其中信號中有四個級別,稱為 PAM-4:

該信號現(xiàn)在傳輸四個值之一:11、10、01 或 00。因此,我們不能使用 PAM-4 提交兩位信息,而不是使用 NRZ 傳輸一位信息。因此,PAM-4 處的 8 GT/s SERDES 鏈路的理論帶寬為 16 Gbps。

對于更高速的連接,我報告了隨著時間的推移,56 Gbps 和 112 Gbps 連接進入市場的情況。這些是多鏈路 SERDES 連接以及編碼方案的變化的混合。這些技術不僅適用于網(wǎng)絡或連接到 FPGA 的收發(fā)器,而且 GPU 到 GPU 連接也利用了這些高速連接。

隨著連接帶寬的增加,公差和制造精度也大幅提高。因此,由于成本原因,我們經(jīng)常看到這些高速連接首先在較舊的工藝節(jié)點(例如 28 納米或 16 納米)中展示,然后才進入可以提供更高效率的更密集的工藝節(jié)點。此外,根據(jù)應用的不同,如果可以應用更復雜的編碼方案,則可以更容易地以較低的比特率開始傳輸。

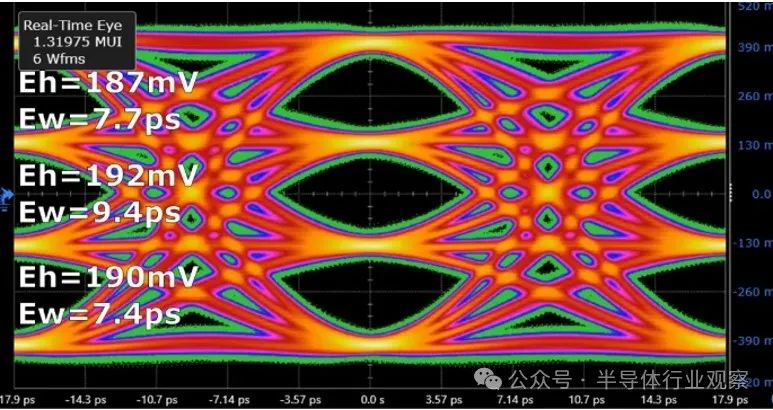

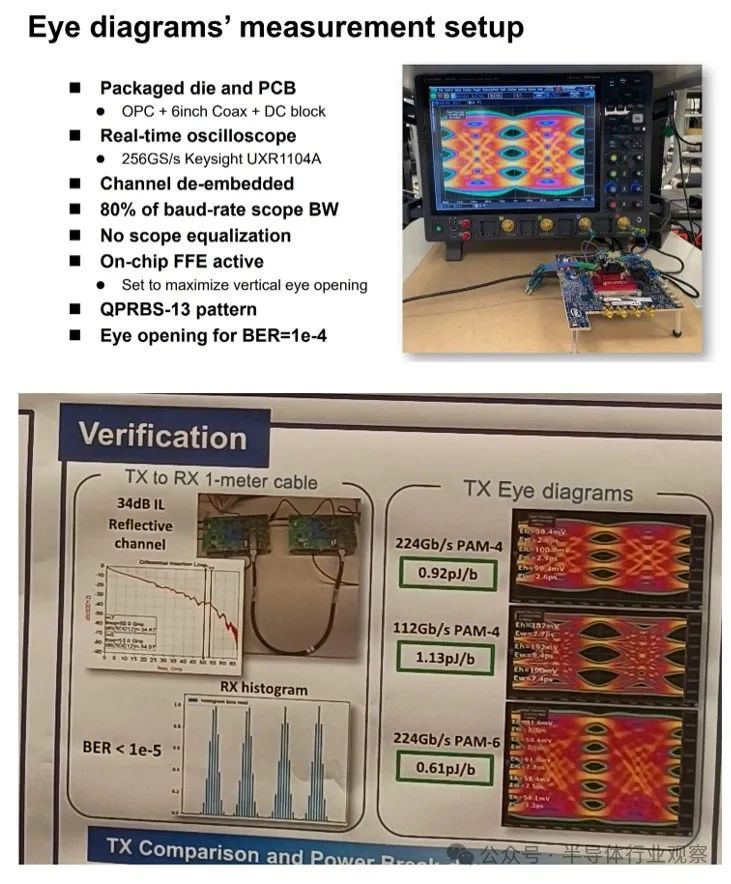

考慮到這一切,英特爾在 ISSCC 2024 上展示了一些令人印象深刻的芯片。它不僅適用于一些最快的 SERDES 連接帶寬數(shù)字,而且還采用 3nm 硅——一種尚未商用的工藝節(jié)點。最重要的是,他們集成了 PAM-6 編碼方案。該芯片名為 Bixby Creek。

PAM6 意味著每次傳輸編碼更多位,但區(qū)分這些位也變得更加困難。與常規(guī) NRZ 相比,如果 PAM4 提供 2 倍的帶寬,那么 PAM6 總體上應提供 2.58 倍左右的帶寬。不過,所有這些都具有相同的功率,因此在這種情況下它提供了令人難以置信的功率效率。

英特爾之前曾在 IEEE 活動中展示過 224 Gb/s,傳輸 (Tx) 為每比特 1.9 皮焦耳,接收 (Rx) 為每比特 1.4 皮焦耳(合計 3.3 pJ/位)。現(xiàn)在,當每秒傳輸 GB 字節(jié)時,該值可能很高 - 以 3.3 pJ/bit 的速度傳輸 1 Terabit 相當于 3.3 瓦。這一新演示將傳輸功率降低至每比特 0.92 pJ,將傳輸側的功率減半,并在英特爾即將推出的工藝節(jié)點之一上實現(xiàn)。所有這些都在 0.15mm2 的硅中實現(xiàn)。

這在宏偉的計劃中意味著什么?流程節(jié)點技術與任何流程節(jié)點非常相似,需要驗證各種 IP 塊,以便客戶能夠使用它們。對于任何構建新節(jié)點的代工廠來說,這意味著確保設計的數(shù)字邏輯和模擬部分協(xié)同工作。

對于英特爾來說,他們正在為其新節(jié)點實施一種滴答平臺 - 在intel 4 上,只有高速邏輯和一些 SERDES 將得到驗證,但對于intel 3 來說,將為客戶提供大量 IP,這就是為什么 Intel 3 是作為代工廠的一部分提供的。與intel 20A 類似,它專注于高速邏輯和一些 SERDES,但18A將為客戶準備好并經(jīng)過驗證的全套 IP。

即便如此,英特爾仍將在內(nèi)部和外部(臺積電、三星)的各種節(jié)點上創(chuàng)建IP以供使用。它是僅供內(nèi)部使用還是作為可許可的知識產(chǎn)權提供,取決于產(chǎn)品的性質(zhì)。本文和演示的主要作者之一確認,英特爾在臺積電和英特爾上提供了大量高速 SERDES 連接。

原文鏈接 https://morethanmoore.substack.com/p/intel-demonstrates-high-speed-3nm

審核編輯:劉清

-

英特爾

+關注

關注

61文章

10301瀏覽量

180437 -

二進制

+關注

關注

2文章

809瀏覽量

43029 -

intel

+關注

關注

19文章

3508瀏覽量

191271 -

SerDes

+關注

關注

8文章

234瀏覽量

36835 -

AI芯片

+關注

關注

17文章

2128瀏覽量

36773

原文標題:Intel展示3nm的Serdes芯片:PAM 6、224Gb/s

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

小米自研3nm旗艦SoC、4G基帶亮相!雷軍回顧11年造芯路

臺積電擬投資170億,在日本建設3nm芯片工廠

REDMI Turbo 5系列搭載MediaTek天璣9500s芯片

MediaTek發(fā)布天璣座艙S1 Ultra芯片

今日看點:我國科學家研制出高精度可擴展模擬矩陣計算芯片;Microchip 推出首款 3nm PCIe Gen 6 交換芯片

224Gb/s速率下的互聯(lián)抉擇:CPC與CPO技術深度對比與未來展望

448G的路徑 | Samtec與Cadence合作的224G測試平臺具備可擴展性、成本優(yōu)勢

PCIe 6.0 SSD主控芯片曝光!4nm制程,順序讀取高達28 GB/s

蘋果A20芯片的深度解讀

雷軍:小米自研芯片采用二代3nm工藝 雷軍分享小米芯片之路感慨

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規(guī)則

什么是SerDes?SerDes有哪些應用?

BK200-800S24GB1N6 BK200-800S24GB1N6

BK150-800S28GB1N6 BK150-800S28GB1N6

BK150-800S28GB1D6 BK150-800S28GB1D6

Intel展示3nm的Serdes芯片:PAM 6、224Gb/s

Intel展示3nm的Serdes芯片:PAM 6、224Gb/s

評論