在高級節點使用 SRAM 需要新的方法。

SRAM無法擴展,這給功耗和性能目標帶來了挑戰,迫使設計生態系統提出從硬件創新到重新思考設計布局的策略。與此同時,盡管 SRAM 的初始設計已經存在很長的歷史,并且目前還存在擴展限制,但它已成為人工智能的主力存儲器。

SRAM 配置有六個晶體管,這使其訪問時間比 DRAM 更快,但代價是在讀取和寫入時消耗更多能量。相比之下,DRAM 采用一個晶體管/一個電容器的設計,這使得它更便宜。但 DRAM 會影響性能,因為電容器因電荷泄漏而需要刷新。因此,自推出 60 多年以來,SRAM 一直是優先考慮較低延遲和可靠性的應用中的首選存儲器。

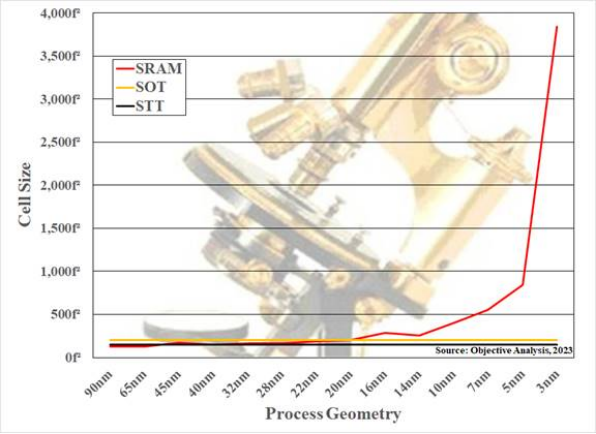

圖 1:SRAM 單元尺寸縮小得比進程更慢。來源:新興內存技術報告

事實上,對于 AI/ML 應用來說,SRAM 不僅僅具有其自身的優勢。“SRAM 對于 AI 至關重要,尤其是嵌入式 SRAM。它是性能最高的存儲器,您可以將其直接與高密度邏輯芯片集成。僅出于這些原因,這一點就很重要。”Alphawave Semi首席技術官托尼·陳·卡魯松 (Tony Chan Carusone) 說道。

功耗和性能挑戰

但是,在跟上 CMOS 縮放的步伐時,SRAM 卻表現不佳,這對功耗和性能產生了影響。“在傳統的平面器件縮放中,柵極長度和柵極氧化物厚度一起按比例縮小,以提高性能和對短溝道效應的控制。更薄的氧化物可以在更低的 VDD 電平下實現性能增益,這有利于 SRAM 減少泄漏和動態功耗。”西門子 EDA的存儲器技術專家 Jongsin Yun 說道。“然而,在最近的技術節點遷移中,我們幾乎沒有看到氧化層或 VDD 電平進一步縮小。此外,晶體管的幾何收縮導致金屬互連更薄,從而導致寄生電阻增加,這就導致更多的功率損耗和 RC 延遲。

隨著人工智能設計越來越需要更多的內部存儲器訪問,SRAM 在技術節點遷移中進一步擴大其功耗和性能優勢已成為一項重大挑戰。”

這些問題加上 SRAM 的高成本,不可避免地會導致性能下降。Rambus的杰出發明家 Steve Woo 表示:“如果無法獲得足夠的 SRAM 來滿足處理器內核的數據存儲需求,那么內核最終將不得不將數據移至更遠的地方。” “在 SRAM 和 DRAM 之間移動數據需要額外的電力,因此系統消耗更多的電力,從 DRAM 訪問數據需要更長的時間,因此性能會下降。”

imecDTCO 項目總監 Geert Hellings 表示:“展望納米片,SRAM 的尺寸縮放預計會非常小。” “可以說,如果所有其他工藝/布局裕度保持不變,用納米片(~15nm 寬)替換鰭片(約 15nm 寬)將使 SRAM 位單元高度增加 40nm(每個 4 個鰭片)。顯然,這不是一個很好的價值主張。因此,工藝/布局余量的改進有望抵消這一點。然而,將SRAM從finFET擴展到納米片是一場艱苦的戰斗。

Flex Logix曾在幾個最低節點工作過,包括臺積電的 N7 和 N5,最近還收到了英特爾 1.8A節點的 PDK。Flex Logix 首席執行官 Geoffrey Tate 表示:“我們使用先進節點的客戶都抱怨該邏輯的擴展性比 SRAM 更好、更快。” “這對于處理器來說是一個問題,因為擁有比整個處理器更大的緩存內存是不尋常的。但如果你把它放在芯片外,你的性能就會急劇下降。”

臺積電正在聘請更多內存設計師來提高 SRAM 密度,但他們是否能從 SRAM 中獲得更多收益還有待觀察。Tate說:“有時,你可以通過雇傭更多的人來讓事情變得更好,但僅限于一定程度。” “隨著時間的推移,客戶將需要考慮不再像現在那樣頻繁使用 SRAM 的架構。”

事實上,早在 20 納米時代,SRAM 就無法與邏輯相稱地擴展,這預示著當片上存儲器變得比芯片本身更大時,將會出現功耗和性能挑戰。針對這些問題,系統設計人員和硬件開發人員都在應用新的解決方案并開發新技術。

沿著這些思路,AMD采取了不同的方法。Rambus 的 Woo 表示:“他們推出了一種名為 3D V-Cache 的技術,該技術允許將單獨芯片上的附加 SRAM 高速緩存存儲器堆疊在處理器頂部,從而增加處理器內核可用的高速緩存量。” “額外的芯片增加了成本,但允許訪問額外的 SRAM。另一種策略是擁有多級緩存。處理器內核可以擁有只有它們才能訪問的私有(非共享)一級和二級緩存,以及在處理器內核之間共享的更大的末級緩存 (LLC)。由于處理器擁有如此多的內核,共享 LLC 允許某些內核使用更多容量,以便在所有處理器內核上更有效地使用總容量。”

糾錯

縮放也增加了可靠性問題。Flex Logix 首席技術官 Cheng Wang 表示:“SRAM 傳統上使用比邏輯單元更激進、更小的尺寸,但它與傳統邏輯門不同,傳統邏輯門永遠不會發生爭用,并且您總是在其中寫入新值。” 由于 SRAM 只有六個晶體管,因此您無法添加大量門來使其在寫入時變弱,在不寫入時放大。你也不能讓 SRAM 太小,因為這可能會因 α 粒子等問題導致單粒子擾動 (SEU),其中離子的能量壓倒 SRAM 單元中的能量,隨著 SRAM 縮小,這種情況更容易發生。

Wang 表示,糾錯可能會成為一項常見要求,特別是對于汽車設備。

權衡

這導致設計方面發生很多變化。“每個人都試圖在芯片上使用更少的 SRAM。”Wang 說。設計人員采取的另一種方法是盡可能只使用單核存儲器。“在較舊的工藝節點中,當我們編寫寄存器文件時,使用雙核內存的可能性要大得多,”他說。“但所有這些都增加了面積。因此,在較低的節點中,設計人員試圖讓所有東西都從內存中的單個端口運行,因為這些是可用的最小、最密集的全功率選項。他們不一定會放棄SRAM,但他們會盡可能地使用單核存儲器。他們試圖使用更小的內存,并選擇SRAM作為可用帶寬,而不是真正的大存儲。大型存儲要么轉移到 DRAM,如果你能承受延遲,要么轉移到 HBM,如果你能負擔得起成本。

替代方法:新架構

為了不斷提高 SRAM 的功耗性能,我們已經評估和應用了超出位單元設計的許多更新,包括 SRAM 外圍設計中的附加支持電路,Yun 表示。

“SRAM 和外圍設備不再共享電源。取而代之的是,采用雙電源軌來單獨利用最有效的電壓水平,”西門子的 Yun 說道。“在某些設計中,SRAM 可以進入休眠模式,施加保留數據所需的最低電壓,直到 CPU 下次訪問數據。這帶來了顯著的功耗優勢,因為漏電流與 VDD 呈指數關系。一些 SRAM 設計采用了額外的電路來解決操作弱點,旨在提高最低工作電壓。”

例如,高密度 (HD) SRAM 單元可以通過對 6 個晶體管使用單鰭晶體管來實現最小的幾何形狀。然而,由于相同尺寸的上拉 (PU) 和通柵極 (PG) 晶體管在寫入操作期間存在爭用問題,HD 單元在低電壓操作中面臨挑戰。

“在SRAM輔助電路中,如負位線,瞬態電壓崩潰技術被廣泛采用,以緩解這些問題并增強低電壓操作,”Yun說。“為了減輕寄生電阻效應,最新的位單元設計使用雙軌或三軌金屬線作為合并位線(BL)或字線(WL)。BL方法根據操作選擇性地連接金屬軌道,降低有效電阻并平衡陣列頂部和底部之間的放電率。在持續的開發中,正在探索埋地電源軌以進一步降低布線電阻。這涉及將所有電源軌放置在晶體管下方,從而緩解晶體管上方的信號路徑擁塞。”

其他存儲器、其他結構

新的嵌入式存儲器類型通常被提出作為 SRAM 的替代品,但每種類型都有自己的一系列問題。“主要的競爭者MRAM和ReRAM僅占用一個晶體管面積,”Yun 說。“雖然它比 SRAM 中的晶體管大,但它們的整體單元尺寸仍約為 SRAM 的三分之一,最終的宏觀尺寸目標(包括外圍電路)約為 SRAM 尺寸的一半。有明顯的尺寸優勢,但寫入速度的表現仍然遠慢于SRAM。實驗室在寫入速度和耐用性方面取得了一些成果,但在汽車用閃存替代 MRAM 生產之后,高速 MRAM 的開發計劃已經延長。L3 緩存替換的尺寸優勢當然值得考慮,但 eflash 類型 MRAM 的生產必須有一個提前的提升。”

如果物理學不允許使用更小的 SRAM,則替代方案將需要重新考慮架構并采用小芯片。“如果 SRAM 無法在 N3 或 N2 中擴展,那么可以將更先進的邏輯芯片與采用舊技術制造的 SRAM 芯片結合起來,”imec 的 Hellings 說。“這種方法將受益于邏輯 PPA 的改進,同時為 SRAM 使用經濟高效的(較舊的,可能更高的產量和更便宜的)技術節點。原則上,AMD 基于 V 緩存的系統可以進行擴展,僅將邏輯芯片移動到下一個節點,然后需要使用 3D 集成或小芯片方法 (2.5D) 組合兩個芯片。”

Ambiq 首席技術官 Scott Hanson 指出,chiplet 解決方案非常適合正在進行的集成革命。“模擬電路很久以前就停止了縮放,出于功耗、性能和成本方面的原因,從 DRAM 到 SRAM 到 NVM 的所有類型的存儲器都更喜歡在不同的節點上制造。邏輯芯片更喜歡在仍然滿足成本和泄漏要求的最小節點上制造。通過多芯片集成,可以將芯片組合到單個封裝中。許多人在移動和數據中心領域都聽說過這一點,但它也在人工智能和物聯網領域迅速發生。”

在有限的情況下,系統技術協同優化 (STCO) 也可以提供幫助。“對于某些應用,原則上不需要片上緩存,”Hellings 說。“例如,在人工智能訓練中,訓練數據僅使用一次,而模型參數應該可以在芯片上輕松訪問。軟件和芯片架構可以繞過緩存層次結構,促進這種一次性數據移動,具有很大的潛力。”

所有這些都激發了人們對新布局和互連協議(例如 UCIe 和 CXL)的興趣。“當你有更大的人工智能工作負載時,內存會隨著計算而擴展,但如果其中一個組件的擴展速度比另一個組件快一點,根據系統的設計方式,你會遇到不同的瓶頸,”新思科技的戰略營銷經理 Ron Lowman 說。“人工智能工作負載大大增加了所需處理器陣列的數量。他們甚至突破了芯片掩模版尺寸的限制,因此現在您需要用于芯片到芯片系統的高速互連(例如 UCIe),這意味著多芯片系統不可避免地要處理人工智能工作負載。”

解決問題的新堆棧

華邦電子通過其 CUBE 堆棧(定制超帶寬元素)重新思考了內存架構。“我們使用 DRAM 作為存儲單元,但也通過過孔進行 3D 堆疊,”華邦 DRAM 營銷經理 Omar Ma 解釋道。“您可以提供從底部基板一直到 SoC 芯片的連接。它更具成本效益,因為 DRAM 不使用 SRAM 的六個晶體管。”

CUBE 可以提供足夠高的密度來替代 SRAM 直至 3 級緩存。“為了達到一定的帶寬要求,只有兩個選擇——提高時鐘速度或增加 I/O 數量,”Omar Ma 解釋道。“使用 CUBE,您可以根據需要增加它們,同時減少時鐘。這在系統層面帶來了很多好處,包括減少對電力的需求。” CUBE 目前處于原型階段,但預計將于 2024 年第四季度或 2025 年初投入生產。

結論

SRAM 被完全取代,這似乎不太可能,至少在短期內是這樣。“幾年前,英特爾演示了使用鐵電存儲器作為緩存,”Objective Analysis 總經理吉姆·漢迪 (Jim Handy) 說。“他們說這是 DRAM,但說實話,這是 FRAM。他們表示,優勢在于他們能夠使用3D NAND技術使其變得非常緊密。換句話說,他們展示了一個擁有大量內存的微小空間。其中一種類型的研究工作(無論是像英特爾所展示的那樣還是 MRAM 等其他方法)很可能最終會取代 SRAM 的位置,但這可能不會很快發生。”

Handy 預計它會導致架構和操作系統軟件發生變化。“你不太可能看到同一個處理器同時具有 SRAM 緩存和鐵電緩存,因為軟件必須進行一些更改才能利用這一點,”他說。“此外,緩存的結構將略有不同。主緩存可能會稍微縮小,而輔助緩存可能會變得非常大。在某個時候,具有 SRAM 緩存的處理器將會問世。下一代處理器將具有鐵電或 MRAM 緩存或類似的東西,并對軟件進行重大更改以使該配置更好地工作。”

審核編輯:劉清

-

CMOS

+關注

關注

58文章

6222瀏覽量

243203 -

電容器

+關注

關注

64文章

6965瀏覽量

108217 -

存儲器

+關注

關注

39文章

7750瀏覽量

172079 -

sram

+關注

關注

6文章

824瀏覽量

117668 -

VDD

+關注

關注

1文章

318瀏覽量

37376

原文標題:SRAM如何克服其擴展問題?

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PSRAM與DRAM/SRAM相比的優勢是什么?

低功耗串口SRAM外擴芯片型號有哪些

低功耗同步SRAM擴展存儲器結構特點

國產芯片偽SRAM存儲器psram

AT32F011 SRAM應用指南

并行sram芯片介紹,并行sram芯片應用場景

利用Solido Design Environment準確預測SRAM晶圓良率

低功耗異步SRAM系列的應用優點

高速數據存取同步SRAM與異步SRAM的區別

SRAM是什么,SRAM的芯片型號都有哪些

如何檢查EZ-USB? CX3 上的 SRAM 使用情況(JTAG 不可用)?

外置SRAM與芯片設計之間的平衡

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

SRAM如何克服其擴展問題?有哪些方法呢?

SRAM如何克服其擴展問題?有哪些方法呢?

評論