有群友提問,下面的代碼為什么在DC里可以綜合成DFF,而在FPGA上卻綜合成了latch。

always@(posedgeclk,negedgerstn,negedgesetn) if(!rstn) a <= 1'b0; ??else?if(!setn) ????a?<=?1'b1; ??else ?? a <= a;

我們可以看到這段代碼有兩個特別之處:

同時有異步復位和異步置位

除了復位和置位,數(shù)據(jù)要保持

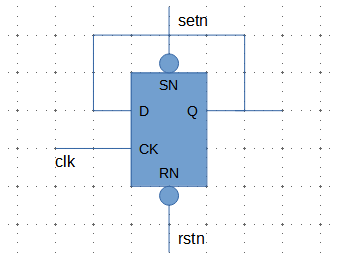

我們可以畫出這段代碼的邏輯圖,如下圖。這圖也就是DC綜合出來的結果。

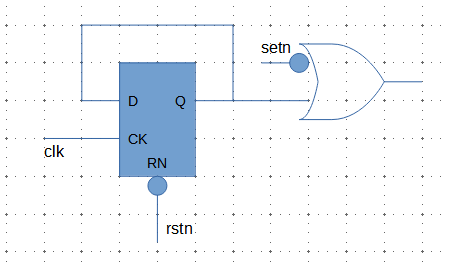

那在FPGA上為什么會變成latch呢?有人說FPGA平臺沒有l(wèi)atch,但quartus里確實報了生成latch的warning。我們來試著把電路等價變換,先把setn端簡化掉:

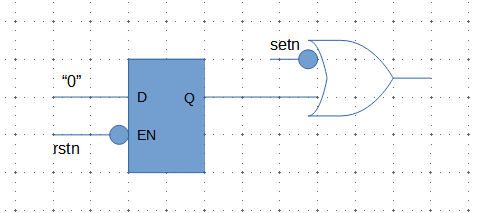

我們看到上圖左邊dff的邏輯,當rstn==0時,dff輸出0,否則就保持。這不就是latch的邏輯嗎?整理出下圖:

由此可見FPGA平臺綜合成latch也是有可能的。

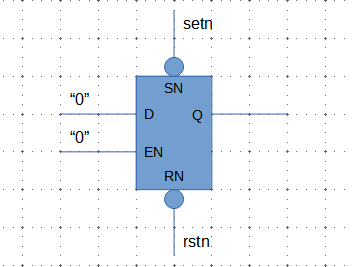

后來讓群友直接看看FPGA平臺綜合出來的電路圖,看看究竟是什么樣的電路。群友回復如下:

哎,真是神奇!時鐘都優(yōu)化沒了,直接用了一個帶復位和置位的latch。看了這個電路的邏輯,確實與一開頭的RTL等價的,并且還不需要數(shù)據(jù)loop了,挺簡潔的。

所以得出結論,F(xiàn)PGA平臺之所以與DC有差異,只是綜合策略或者說是綜合引擎優(yōu)化算法的問題。綜合結果都是可以用的。

審核編輯:劉清

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636231 -

時序電路

+關注

關注

1文章

114瀏覽量

22294 -

異步復位

+關注

關注

0文章

47瀏覽量

13684 -

dff

+關注

關注

0文章

26瀏覽量

3853

原文標題:時序電路為什么綜合成了latch

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

數(shù)字電路之時序電路

時序電路的分析與設計方法

FPGA的設計主要是以時序電路為主嗎?

組合電路和時序電路的講解

時序電路基本介紹

什么是時序電路?

什么是同步時序電路和異步時序電路,同步和異步電路的區(qū)別?

時序電路為什么在FPGA上綜合成了latch?

時序電路為什么在FPGA上綜合成了latch?

評論