與非門脈沖通過時,輸出波形和輸入波形有何差別?

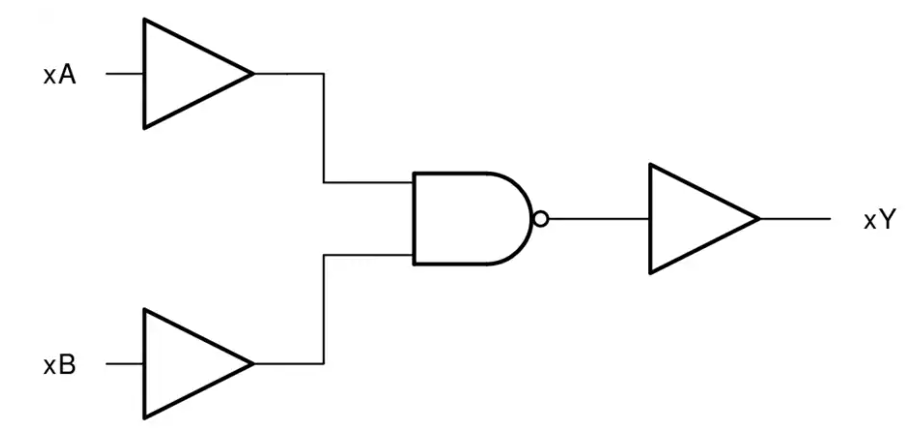

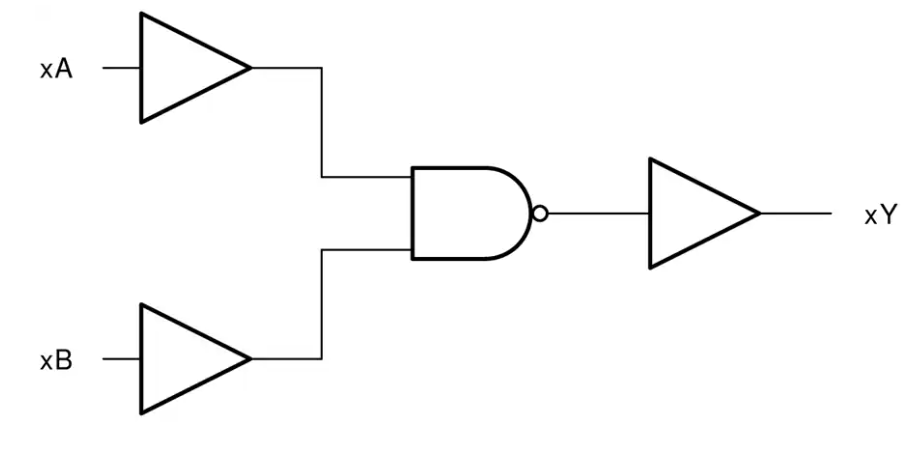

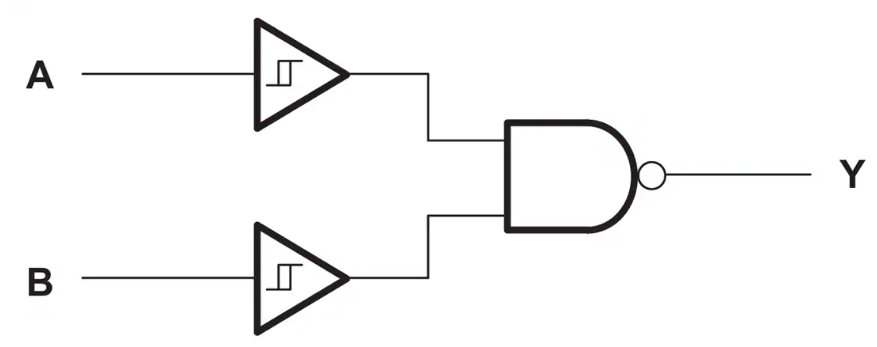

與非門是基本的邏輯門電路元件,用于將兩個輸入信號進(jìn)行邏輯與運算后,輸出一個結(jié)果。與非門的輸出為兩個輸入信號的邏輯與的反向。在電子電路中,與非門可以通過不同的方式來實現(xiàn),其中一種常見的設(shè)計是使用晶體管來構(gòu)成。

當(dāng)與非門脈沖輸入信號通過時,輸出波形和輸入波形存在一些差別。為了更好地理解這種差別,我們需要先了解與非門的工作原理和輸入輸出特性。

與非門有兩個輸入端和一個輸出端。輸入端可以接收兩個不同的電平信號,通常表示為0和1,代表邏輯低電平和邏輯高電平。輸出端也有兩種電平信號,與輸入信號的邏輯與運算結(jié)果相反。輸出結(jié)果用1和0來表示,1表示邏輯低電平,0表示邏輯高電平。

下面我們來詳細(xì)討論與非門脈沖輸入時的具體情況。

在討論輸入脈沖時,我們需要討論輸入信號的上升沿、下降沿、寬度等因素。脈沖信號的上升沿表示信號從低電平轉(zhuǎn)換到高電平的過程,而下降沿則表示信號從高電平轉(zhuǎn)換到低電平的過程。脈沖信號的寬度表示高電平和低電平之間的時間間隔。

當(dāng)與非門脈沖輸入時,首先考慮的是輸入脈沖的上升沿。與非門內(nèi)部的晶體管需要經(jīng)過一定的時間來完成開關(guān)過程,因此在輸入脈沖的上升沿瞬間,輸出信號可能并不會立即反應(yīng)出邏輯與運算的結(jié)果。在這個過程中,輸出信號可能會出現(xiàn)一些漣漪或不穩(wěn)定的現(xiàn)象,導(dǎo)致輸出波形出現(xiàn)一些起伏。

接下來,我們考慮輸入脈沖的下降沿。當(dāng)輸入脈沖的下降沿瞬間到來時,與非門內(nèi)部的晶體管會從導(dǎo)通狀態(tài)切換到截止?fàn)顟B(tài)。這個切換過程同樣需要一定的時間,而在這個過程中,輸出信號也可能會出現(xiàn)一些不穩(wěn)定的現(xiàn)象。因此,在輸入脈沖的下降沿瞬間,輸出波形也可能會出現(xiàn)一些起伏。

除了考慮輸入脈沖的上升沿和下降沿外,我們還需要考慮輸入脈沖的寬度。當(dāng)輸入脈沖的寬度較窄時,可能會導(dǎo)致與非門無法完全響應(yīng)每個脈沖,并且輸出信號可能只會變化一次。這樣輸出波形就與輸入波形有所不同。

綜上所述,與非門脈沖輸入時,輸出波形和輸入波形存在一些差別。這些差別主要源于與非門內(nèi)部晶體管的開關(guān)過程和切換時間所導(dǎo)致的不穩(wěn)定現(xiàn)象。在輸入脈沖的上升沿和下降沿瞬間,輸出信號可能會出現(xiàn)一些起伏。而當(dāng)輸入脈沖的寬度較窄時,輸出信號可能只會變化一次。因此,輸出波形可能會在短時間內(nèi)產(chǎn)生不同的起伏和變化,與輸入波形有所差別。

需要注意的是,與非門脈沖輸入時的具體輸出波形差別會受到電路設(shè)計和具體實現(xiàn)方式的影響。不同的電路設(shè)計和實現(xiàn)方式可能會有不同的響應(yīng)時間和輸出波形特性。因此,在具體的電路設(shè)計和實現(xiàn)中,需要根據(jù)實際情況來確定與非門脈沖輸入時的輸出波形差別。

-

晶體管

+關(guān)注

關(guān)注

78文章

10395瀏覽量

147730 -

門電路

+關(guān)注

關(guān)注

7文章

202瀏覽量

41454 -

與非門

+關(guān)注

關(guān)注

1文章

141瀏覽量

13427

發(fā)布評論請先 登錄

深入解析M74HC03:高速CMOS四2輸入開漏與非門的卓越性能

晶振的輸出波形有哪些

ZUS示波器如何讓雙脈沖測試從“波形”走向“數(shù)據(jù)”?

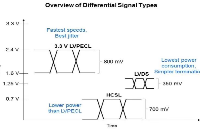

晶振的輸出波形:TTL、CMOS、LVPECL、LVDS和正弦波

確保電壓擊穿試驗儀輸出波形純凈度的技術(shù)與方法

網(wǎng)絡(luò)延遲具體是怎樣影響實時波形查看的?

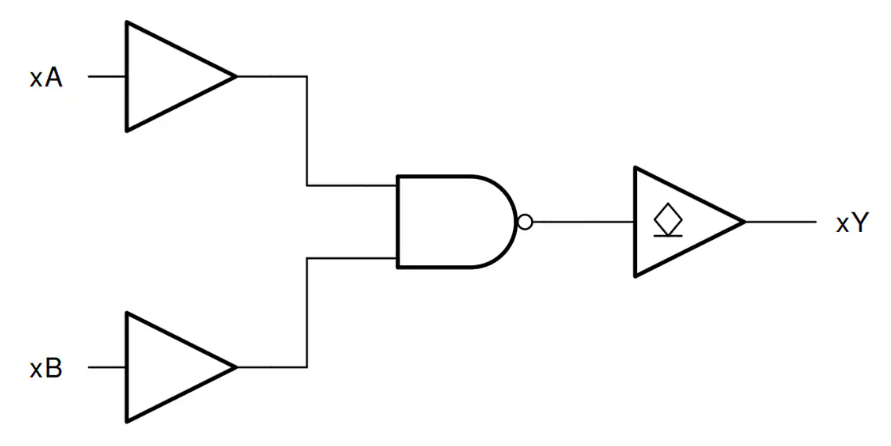

SN74LV4T00四路2輸入正邏輯與非門技術(shù)解析

SN74AHCT00四路2輸入正邏輯與非門技術(shù)解析

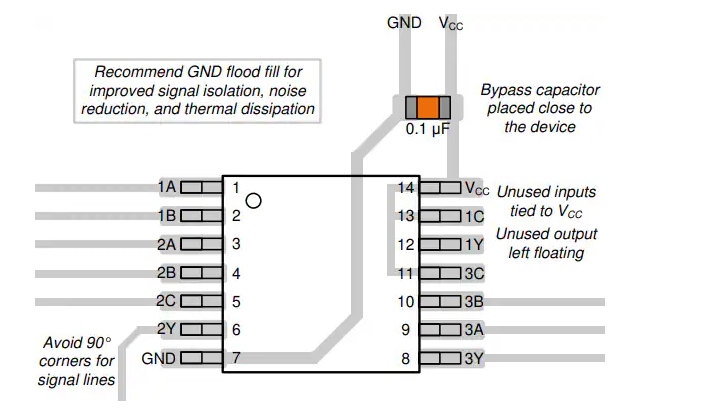

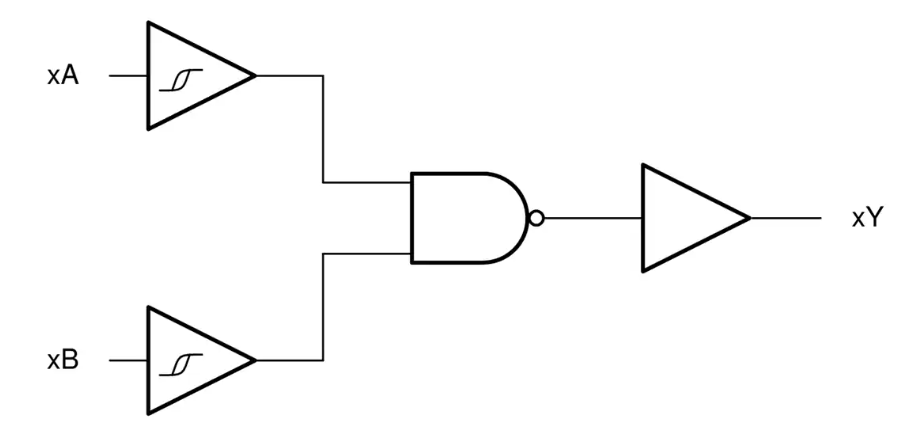

SN74AHC132四通道施密特觸發(fā)與非門技術(shù)解析與應(yīng)用指南

標(biāo)準(zhǔn)浪涌測試波形對比解析

Texas Instruments SN74LVC10A與非門數(shù)據(jù)手冊

高壓變頻經(jīng)常講30脈沖、36脈沖是什么意思?

Texas Instruments SN74HC132/SN74HC132-Q1四路雙輸入與非門數(shù)據(jù)手冊

Texas Instruments SN74HC03四路雙輸入與非門數(shù)據(jù)手冊

與非門脈沖通過時,輸出波形和輸入波形有何差別?

與非門脈沖通過時,輸出波形和輸入波形有何差別?

評論