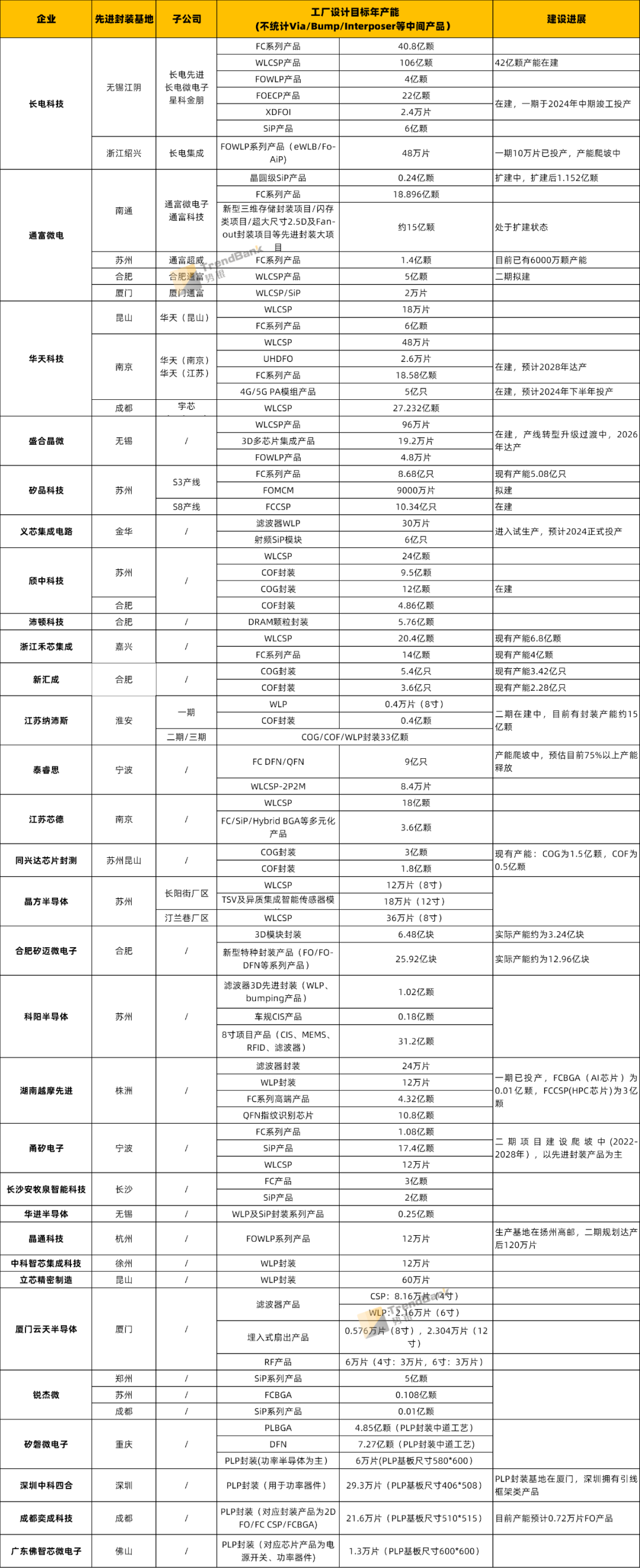

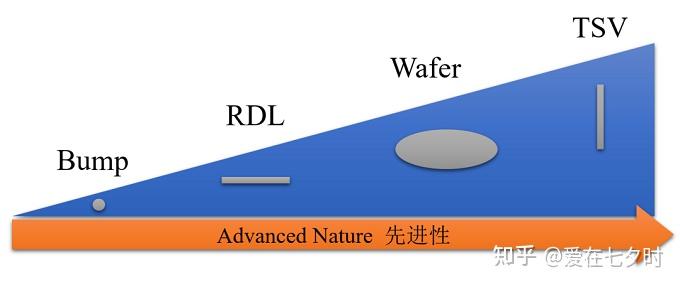

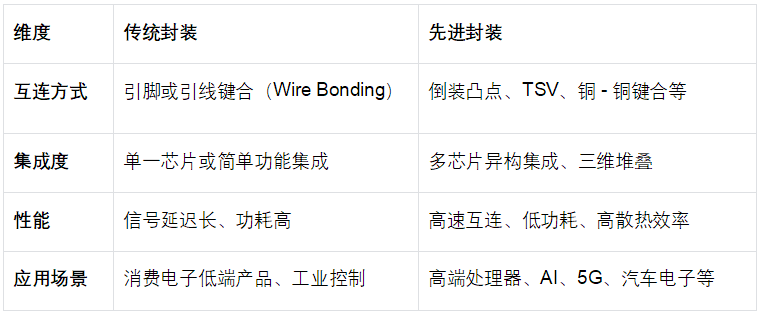

先進(jìn)封裝產(chǎn)品通過半導(dǎo)體中道工藝實(shí)現(xiàn)芯片物理性能的優(yōu)化或者說維持裸片性能的優(yōu)勢(shì),接下來(lái)的后道封裝從工序上而言與傳統(tǒng)封裝基本類似。從封裝工藝角度來(lái)定義,先進(jìn)封裝路線大致可以分為四大類:芯片尺寸封裝(CSP)、晶圓級(jí)封裝(WLP)、面板級(jí)封裝(PLP)、2.5D/3D封裝以及系統(tǒng)級(jí)(SiP)封裝。廣義的SiP封裝可以分解為Chip層面/Wafer層面多芯片集成封裝,也包含著2.5D/3D集成封裝,以及基板層面chiplet集成封裝,甚至是小尺寸PCB板級(jí)多系統(tǒng)集成封裝。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

Chip

+關(guān)注

關(guān)注

1文章

59瀏覽量

27214 -

半導(dǎo)體材料

+關(guān)注

關(guān)注

11文章

577瀏覽量

30850 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

533瀏覽量

1026

原文標(biāo)題:主要先進(jìn)封裝廠商匯總名單半導(dǎo)體材料與工藝設(shè)備

文章出處:【微信號(hào):wc_ysj,微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

芯矽科技:半導(dǎo)體濕法工藝設(shè)備引領(lǐng)者

在半導(dǎo)體制造領(lǐng)域,濕法工藝設(shè)備是保障芯片良率與性能的關(guān)鍵環(huán)節(jié)。芯矽科技憑借深厚的技術(shù)積累與持續(xù)創(chuàng)新,推出一系列先進(jìn)的半導(dǎo)體濕法工藝設(shè)備,為行

鍵合玻璃載板:半導(dǎo)體先進(jìn)封裝的核心支撐材料

鍵合玻璃載板(Glass Carrier/Substrate)是一種用于半導(dǎo)體封裝工藝的臨時(shí)性硬質(zhì)支撐材料,通過鍵合技術(shù)與硅晶圓或芯片臨時(shí)固定在一起,在特定工序(如減薄、RDL布線)完成后通過紫外光

半導(dǎo)體先進(jìn)封裝“Bumping(凸點(diǎn))”工藝技術(shù)的詳解;

如有雷同或是不當(dāng)之處,還請(qǐng)大家海涵。當(dāng)前在各網(wǎng)絡(luò)平臺(tái)上均以此昵稱為ID跟大家一起交流學(xué)習(xí)! 從事半導(dǎo)體行業(yè)的朋友都知道:隨著半導(dǎo)體工藝逼近物理極限,傳統(tǒng)制程微縮已經(jīng)無(wú)法滿足高帶寬、低延遲的需求。這時(shí)候,

目前最先進(jìn)的半導(dǎo)體工藝水平介紹

當(dāng)前全球半導(dǎo)體工藝水平已進(jìn)入納米級(jí)突破階段,各大廠商在制程節(jié)點(diǎn)、材料創(chuàng)新、封裝技術(shù)和能效優(yōu)化等方面展開激烈競(jìng)爭(zhēng)。以下是目前最

BW-4022A半導(dǎo)體分立器件綜合測(cè)試平臺(tái)---精準(zhǔn)洞察,卓越測(cè)量

可靠性保駕護(hù)航!

一、嚴(yán)謹(jǐn)細(xì)微,鑄就精準(zhǔn)測(cè)試之魂

BW-4022A半導(dǎo)體分立器件綜合測(cè)試平臺(tái)采用先進(jìn)的高精度傳感器和精密的測(cè)量算法,如同擁有一雙“火眼金睛”,能夠?qū)?Si/SiC/GaN 等各類材料

發(fā)表于 10-10 10:35

半導(dǎo)體封裝清洗工藝有哪些

半導(dǎo)體封裝過程中的清洗工藝是確保器件可靠性和性能的關(guān)鍵環(huán)節(jié),主要涉及去除污染物、改善表面狀態(tài)及為后續(xù)工藝做準(zhǔn)備。以下是主流的清洗技術(shù)及其應(yīng)用

半導(dǎo)體人必懂的50個(gè)‘黑話’:從光刻到封裝,一文解鎖行業(yè)暗號(hào)!

以下是半導(dǎo)體工藝行業(yè)中常見的“黑話”(行業(yè)術(shù)語(yǔ))匯總,涵蓋晶圓制造、封裝測(cè)試、設(shè)備材料等環(huán)節(jié),幫

漢思膠水在半導(dǎo)體封裝中的應(yīng)用概覽

漢思膠水在半導(dǎo)體封裝中的應(yīng)用概覽漢思膠水在半導(dǎo)體封裝領(lǐng)域的應(yīng)用具有顯著的技術(shù)優(yōu)勢(shì)和市場(chǎng)價(jià)值,其產(chǎn)品體系覆蓋底部填充、固晶粘接、圍壩填充、芯片包封等關(guān)鍵

什么是半導(dǎo)體行業(yè)用的面板系列Panel Chiller?

半導(dǎo)體面板Chiller是用于半導(dǎo)體制造和顯示面板(如LCD/OLED)生產(chǎn)中的高精度冷卻設(shè)備,主要功能是為關(guān)鍵工藝設(shè)備提供穩(wěn)定的溫度控制,

半導(dǎo)體封裝工藝流程的主要步驟

半導(dǎo)體的典型封裝工藝流程包括芯片減薄、芯片切割、芯片貼裝、芯片互連、成型固化、去飛邊毛刺、切筋成型、上焊錫、打碼、外觀檢查、成品測(cè)試和包裝出庫(kù),涵蓋了前段(FOL)、中段(EOL)、電鍍(plating)、后段(EOL)以及終測(cè)(final test)等多個(gè)關(guān)鍵環(huán)節(jié)。

提供半導(dǎo)體工藝可靠性測(cè)試-WLR晶圓可靠性測(cè)試

隨著半導(dǎo)體工藝復(fù)雜度提升,可靠性要求與測(cè)試成本及時(shí)間之間的矛盾日益凸顯。晶圓級(jí)可靠性(Wafer Level Reliability, WLR)技術(shù)通過直接在未封裝晶圓上施加加速應(yīng)力,實(shí)現(xiàn)快速

發(fā)表于 05-07 20:34

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測(cè)

——薄膜制作(Layer)、圖形光刻(Pattern)、刻蝕和摻雜,再到測(cè)試封裝,一目了然。 全書共分20章,根據(jù)應(yīng)用于半導(dǎo)體制造的主要技術(shù)分類來(lái)安排章節(jié),包括與半導(dǎo)體制造相關(guān)的基礎(chǔ)技

發(fā)表于 04-15 13:52

半導(dǎo)體貼裝工藝大揭秘:精度與效率的雙重飛躍

隨著半導(dǎo)體技術(shù)的飛速發(fā)展,芯片集成度不斷提高,功能日益復(fù)雜,這對(duì)半導(dǎo)體貼裝工藝和設(shè)備提出了更高的要求。半導(dǎo)體貼裝

主要先進(jìn)封裝廠商匯總名單半導(dǎo)體材料與工藝設(shè)備

主要先進(jìn)封裝廠商匯總名單半導(dǎo)體材料與工藝設(shè)備

評(píng)論