摩爾定律走下神壇,誰會是芯片下一個制勝法則?

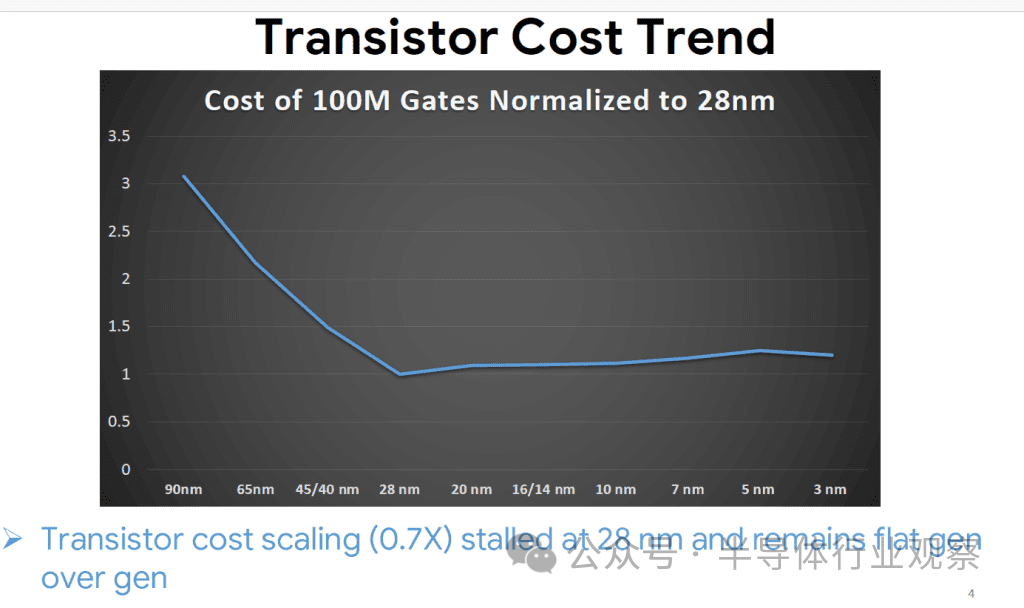

在動態的半導體技術領域,圍繞摩爾定律的持續討論經歷了顯著的演變,其中最突出的是 MonolithIC 3D 首席執行官Zvi Or-Bach于2014 年的主張。他關于晶體管成本縮減在 28 nm 達到關鍵節點的說法引起了廣泛關注。

最近,谷歌的 Milind Shah 在 IEDM 2023 的短期課程中驗證了這一說法。這一明確的說法“晶體管成本縮放 (0.7 倍) 在 28 納米處停滯不前,并且一代一代之間保持持平”,這證實了之前的說法。最初在 2014 年的公眾觀點和博客中預見到了摩爾定律的結論。

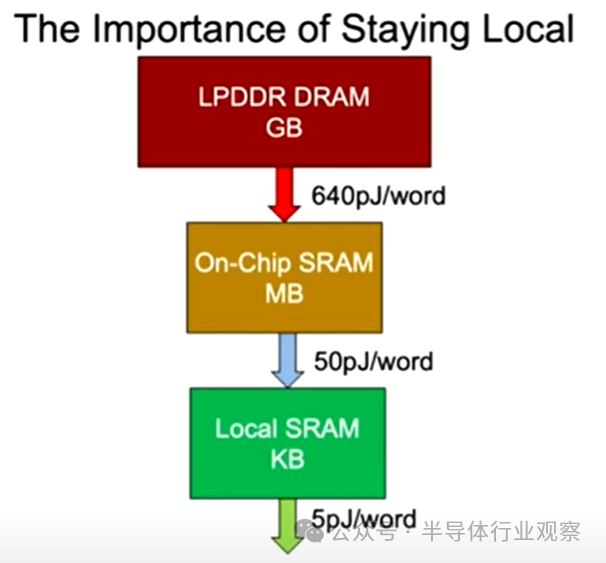

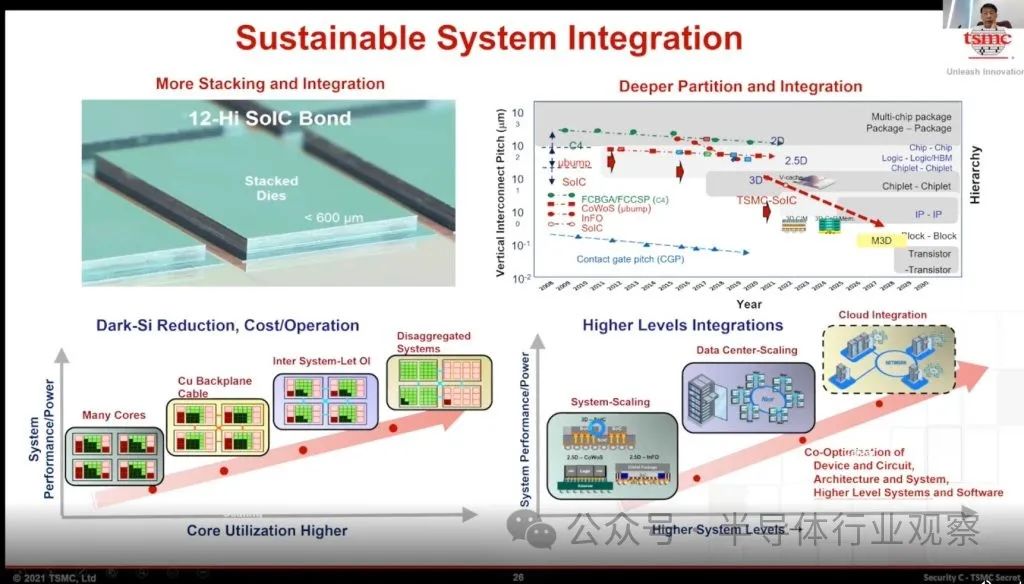

盡管成本擴展停滯不前,為什么業界仍在推動更小的晶體管,目標是令人難以置信的 1 nm 節點?答案在于系統級的好處。正如 NVIDIA 首席科學家 Bill Dally 的圖表所示。

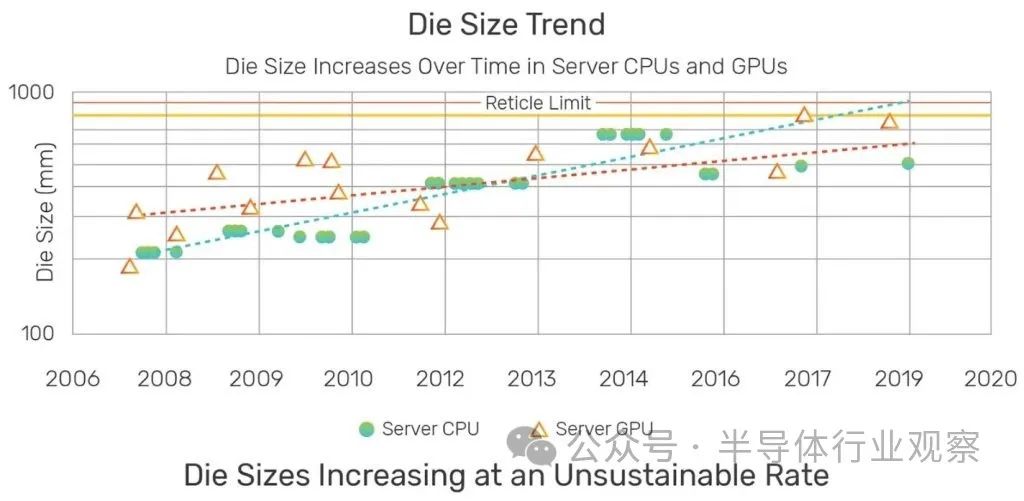

這反過來又推動了 CPU 和 GPU 等領先計算設備達到甚至更大尺寸的趨勢。對更小節點的追求使得芯片上的組件集成更加緊密,從而進一步提高性能和效率。

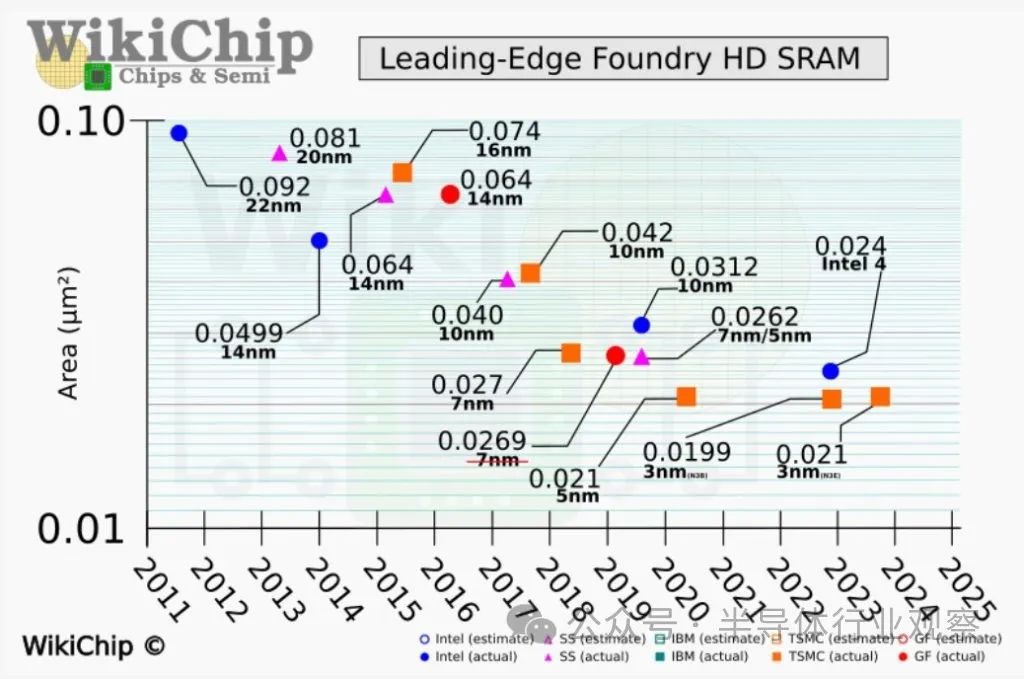

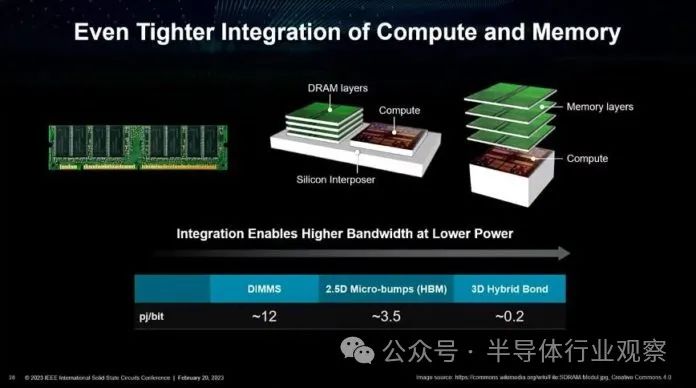

不幸的是,邏輯和存儲器(DRAM、NAND)制造工藝非常不同。因此,它們是在不同的晶圓上生產的并且不能通過縮放來集成。更糟糕的是,SRAM 位單元縮放已停止在 5 納米節點。

AMD 和臺積電似乎都 了解這些趨勢,并在過去幾年中采用了混合鍵合技術,以實現未來計算性能的進步。

雖然當前的實施(例如 AMD 的 3D V-Cache)是充分發揮 3D 集成潛力的墊腳石,但仍然存在重大障礙。其中包括架構思維的根本轉變,從傳統的邊緣互連轉向新穎的 3D 集成方法。此外,要實現廣泛采用,還需要在系統級冗余、晶圓級集成、甚至片上射頻網絡方面進行創新

拯救摩爾定律的終極辦法

正如IMEC負責計算擴展的邏輯副總裁Julien Ryckaert所說:“整個半導體行業目前正在經歷一場巨大的變革。十多年來,很明顯,受摩爾定律(更具體地說是登納德定律)啟發的尺寸縮放不能用作預測 CMOS 技術節點未來的晴雨表。”

這源于我們現在稱為“縮放墻”的幾個因素。不僅擴展 CMOS 組件的特征尺寸變得極其困難和昂貴,而且行業在其復雜系統中也面臨著嚴重的功率和速度障礙。

在技術層面,新的器件架構和縮放助推器——由設計技術協同優化 (DTCO) 支持——可以在接下來的幾個 CMOS 節點中保持一定的面積縮放。但是這些將不可避免地失去動力,或者至少不足以提供未來應用程序的系統擴展期望。

在架構級別,復雜的內存層次結構、多核和多線程以及單個片上系統 (SoC) 或小芯片中的核心專業化 (xPUs...) 已成為克服這些擴展的方法墻壁。

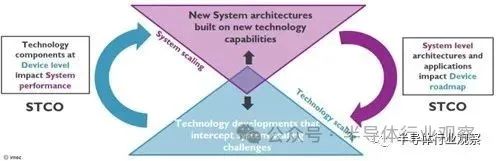

“我們今天面臨的問題是,早期的創新很少是真正的系統架構到技術優化循環的結果。向前邁進的最大挑戰將是解決可以解決主要系統擴展瓶頸的正確技術成分,以及探索一些技術中斷如何能夠實現新的計算方式。這就是系統技術協同優化 (STCO) 框架的目的。”Julien Ryckaert接著說。

在IMEC看來,由于自身需要在定義未來技術方面處于領先地位,因此他們現在必須通過系統擴展挑戰來豐富其技術路線圖。這種演變從根本上意味著我們需要跳出傳統的“通用”技術產品,接受這樣一個事實,即解決方案是由如人工智能、高性能計算 (HPC)和增強現實/虛擬現實等特定應用需求驅動的。

此外,最佳系統實施將是跨多種技術(例如極端 CMOS 邏輯縮放、高級 3D 封裝、新型存儲元件甚至 Si 光子學)的微妙優化的結果。到目前為止,這些不同的技術研究活動是分別進行的,每個活動都有自己的 DTCO 研究和路線圖。

為了為系統驅動的擴展過渡做好準備,IMEC重組了核心項目,并將所有 DTCO 活動整合到一個項目中,該項目將研究所有核心技術項目中的技術到電路優化,并用 STCO 計劃補充了這個 DTCO 計劃,這將確保 DTCO 研究和系統應用空間之間的聯系。

“此 STCO 計劃的目標是以自上而下的方式將未來的系統需求和瓶頸轉化為技術需求。它還將探索利用獨特和新穎的技術能力啟用新架構的可能性。”Julien Ryckaert說。

據他所說,在IMEC的每個核心技術項目中,都開始了獨立的研究活動,這些活動已經需要一定程度的系統評估。

一個很好的例子是其在 2022 年 VLSI 研討會上展示的背面供電網絡。這項工作是 3D 程序活動和邏輯活動共同開發電力傳輸系統解決方案的結果。背面技術嚴重影響邏輯縮放路線圖,因為它需要 3D 技術功能,例如晶圓處理和硅通孔 (TSV) 處理。但要了解背面供電網絡為何以及如何帶來真正的系統性能優勢,需要評估其在更復雜環境中的行為,并深入研究系統配置。

另一個例子是新興存儲器,其中一些預計將取代片上 SRAM。這樣的內存方案必然會影響邏輯縮放路線圖,只能在系統仿真框架中進行評估。更不用說其中一些記憶可能會以 3D 方式堆疊。

當我們開始為這些示例解決系統級挑戰時,我們很快意識到,對于每個示例,所有技術解決方案都相互糾纏在一起。很明顯,邏輯、內存和 3D 程序中的技術研究不能再在單獨的“孤島”中處理:它必須同時完成并由系統應用程序目標驅動。

”好消息是我們不是從頭開始,因為我們已經有許多從系統角度分析的研究活動。我們現在需要的是將這些活動組織成一個共同的愿景,并為它們制定路線圖。”Julien Ryckaert表示。

Julien Ryckaert進一步指出,IMEC的 DTCO/STCO 活動圍繞系統的 3 個基本擴展壁進行了闡述:內存/帶寬壁(即,如何以足夠的速度獲取數據以饋送邏輯內核)、功率/熱壁(即,如何有效地處理功率傳輸和散熱)和尺寸縮放墻。

IMEC希望能與其合作伙伴一起校準這個研究路線圖,并確保我們正在為行業應對正確的挑戰。這將需要與所有的合作伙伴進行深入討論,而這些已經開始進行。

Julien Ryckaert表示:“盡管人們和我們一樣認為這是一個雄心勃勃的計劃目標,但我們確實看到了圍繞這一倡議的很多興奮。我們必須明智地選擇我們的戰斗,那些與未來系統擴展最相關的戰斗,同時利用我們獨特的技術能力。”

在他看來,真正的 STCO 研究需要將許多學科整合在一起,每個學科都處理廣泛不同的規模,并在不同的抽象領域運作他們的科學。一個真正的挑戰是在不丟失關鍵信息的情況下,構建從一個域到另一個域的一組適當的抽象層。這是從上到下和從下到上傳播信息以執行完整系統優化的唯一方法。

而要正確地做到這一點,您不僅需要每個領域的所有正確專業知識,而且還需要這些學科彼此密切互動。Imec 擁有獨特的基礎設施,其中大多數學科都在同一屋檐下緊密合作。這有助于思想的交流、信息的順利傳播以及擴大對結果和解釋的批判眼光。

“我對在這個 STCO 領域向前邁進感到非常興奮,因為我們所有人,無論我們來自哪個領域,都明白在未來半導體研究中發揮作用的將是通過 STCO 框架。而 imec 是這種計劃起飛的合適地點。”Julien Ryckaer說。

審核編輯:黃飛

-

cpu

+關注

關注

68文章

11277瀏覽量

224944 -

摩爾定律

+關注

關注

4文章

640瀏覽量

80897 -

gpu

+關注

關注

28文章

5194瀏覽量

135427 -

晶體管

+關注

關注

78文章

10395瀏覽量

147723 -

28nm

+關注

關注

0文章

173瀏覽量

95699

原文標題:摩爾定律止步28nm

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Chiplet,改變了芯片

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

當摩爾定律 “踩剎車” ,三星 、AP、普迪飛共話半導體制造新變革新機遇

【原創】TDMS設置下一個寫入位置函數的摸索

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

AI玩具或成為下一個萬億新賽道

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

電力電子中的“摩爾定律”(1)

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

評論