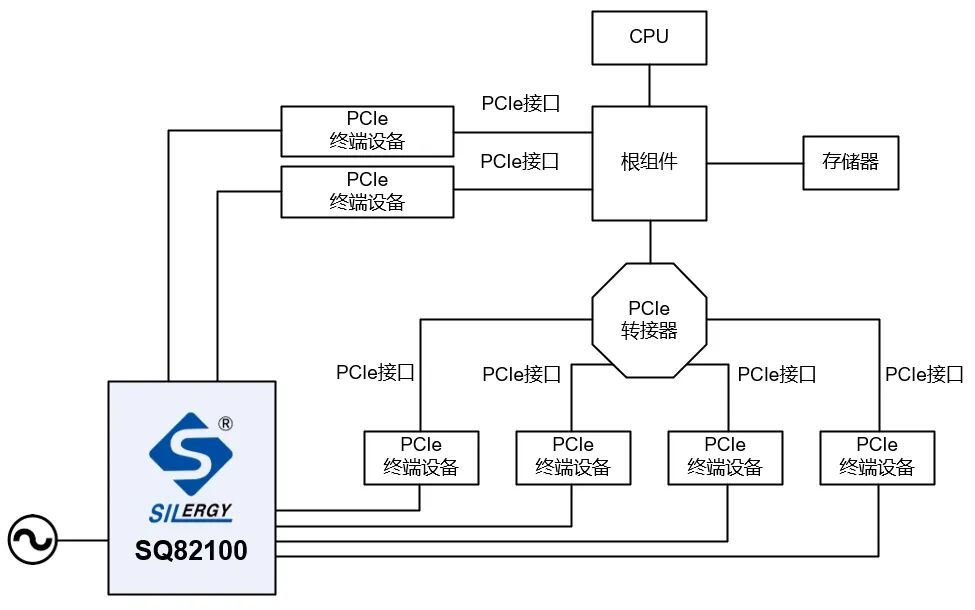

PCI-Express(PCIe)是一種高速串行計算機擴展總線標準,主要用于擴充計算機系統總線數據吞吐量以及提高設備通信速度。目前服務器等應用已集成越來越多的PCIe終端,矽力杰新一代高性能PCIe時鐘緩沖器SQ82100可以為系統提供20路超低附加抖動的LP-HCSL參考時鐘,能夠簡化系統布局,進一步提高終端系統性能和集成度。

PCIe接口

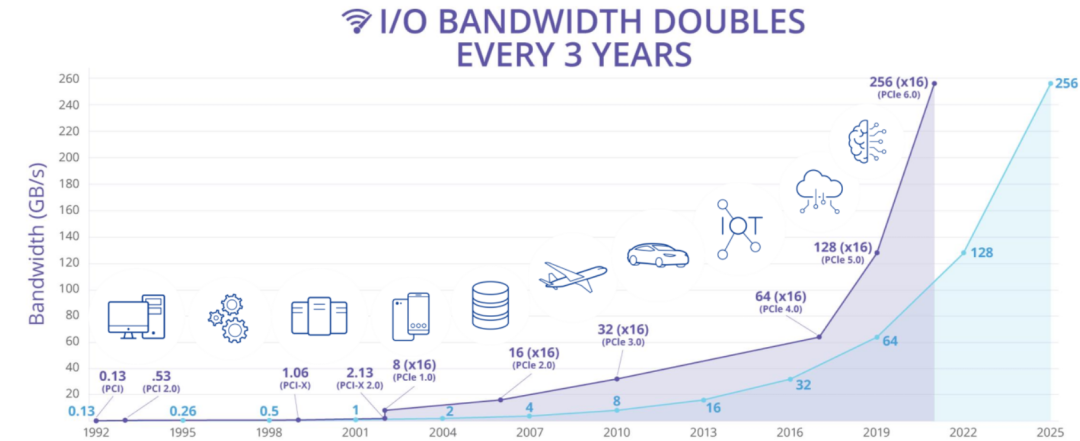

PCIe接口常用于服務器和高性能計算系統的高速數據接口,經過多年發展,PCIe接口已經從PCIe Gen1(2.5GT/s)演進到如今的PCIe Gen6(64GT/s),在個人計算機,服務器,工作站,輔助駕駛等電子設備終端中被廣泛應用。

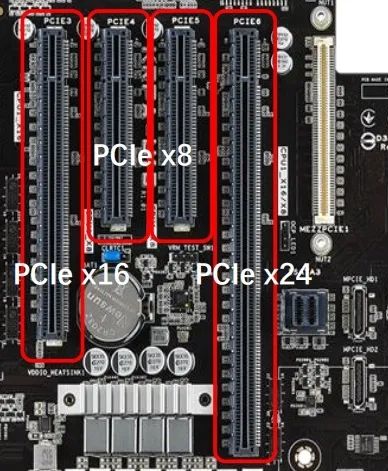

PCIe接口的參考時鐘為100MHz的差分 HCSL/LP-HCSL 電平信號。最為常用和可靠的時鐘架構是Common Clock Architecture (CC),即使用單一的時鐘緩沖器為多個PCIe終端設備提供點對點的參考時鐘,如下圖為服務器的主板上的PCIe接口。

矽力杰多通道時鐘緩沖器方案

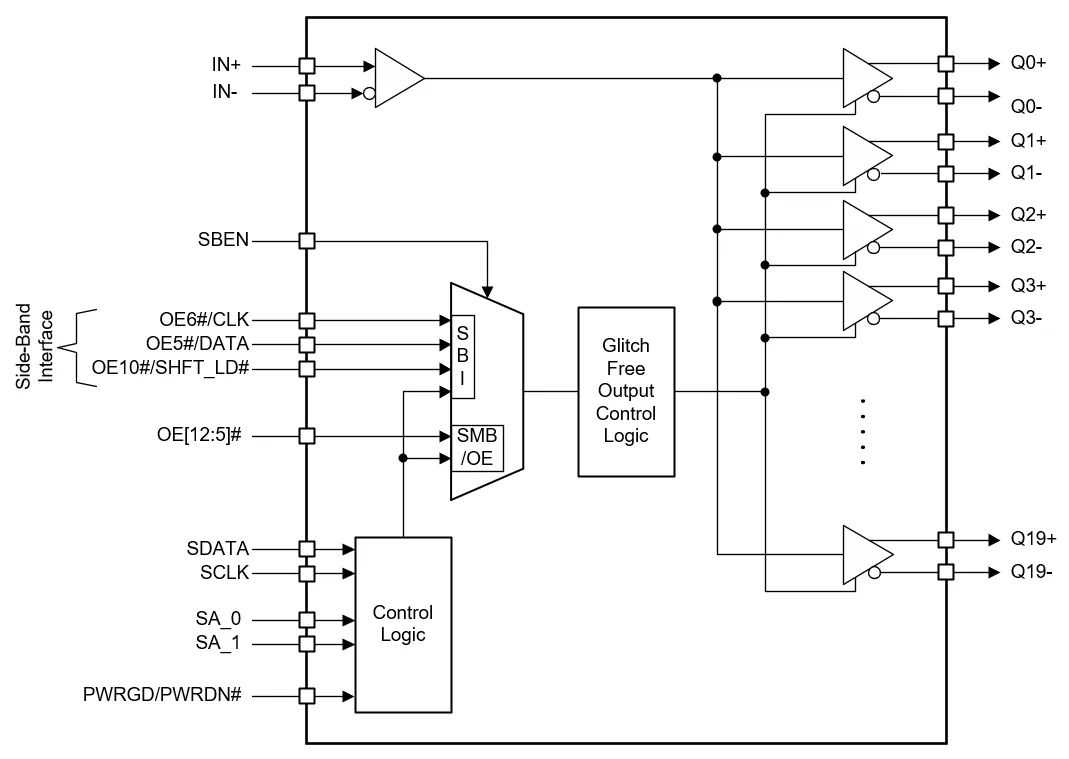

矽力杰新一代時鐘緩沖器SQ82100提供20路超低附加抖動的LP-HCSL參考時鐘,輸出差分阻抗為85Ω。SQ82100高集成的輸出端口可以節省外部匹配的80個終端電阻從而優化PCB布局。內部集成OE,SMBus以及3線SBI (Side Band Interface) 功能以方便控制打開或關閉任何通道,調節輸出信號幅度、阻抗及默認下電電平。

SQ82100

高性能20路PCIe時鐘緩沖器

◆20路低功耗推挽式LP-HCSL PCIe 85Ω差分輸出時鐘

◆ 滿足Intel DB2000QL指標要求

◆ 差分輸出時鐘附加抖動:

?DB2000QL<30fs RMS

?PCIe Gen4 <30fs RMS

?PCIe Gen5 <20fs RMS

?PCIe Gen6 <10fs RMS

◆ 輸出頻率范圍: 1MHz to 400MHz

◆ 3.3V供電,典型功耗600mW

◆ 內部集成LDO

◆ 通道間Skew<50ps

◆ SMBus接口和SBI接口

◆ 8個OE控制引腳

◆ 允許掉電情況下數字引腳有輸入信號(PDT), 確保在異常系統條件下的器件得到保護

◆可選的SMBus地址允許同時使用多個器件

◆ 緊湊型封裝: AQFN6x6-80

性能優勢

超低附加抖動

隨著數據傳輸速率要求不斷提高,為了保證系統無碼傳輸,PCIe高速接口對參考時鐘的RMS抖動指標要求愈加苛刻,最新的PCIe Gen6要求100MHz參數時鐘在協議規定的積分帶寬內低于100fs RMS的時鐘抖動。PCIe接口對參考時鐘的指標要求如下:

SQ82100 的超低附加抖動遠超PCIe Gen5.0, Gen6.0的性能指標要求,能夠有效簡化PCIe系統設計,為系統設計提供更多的設計余量。

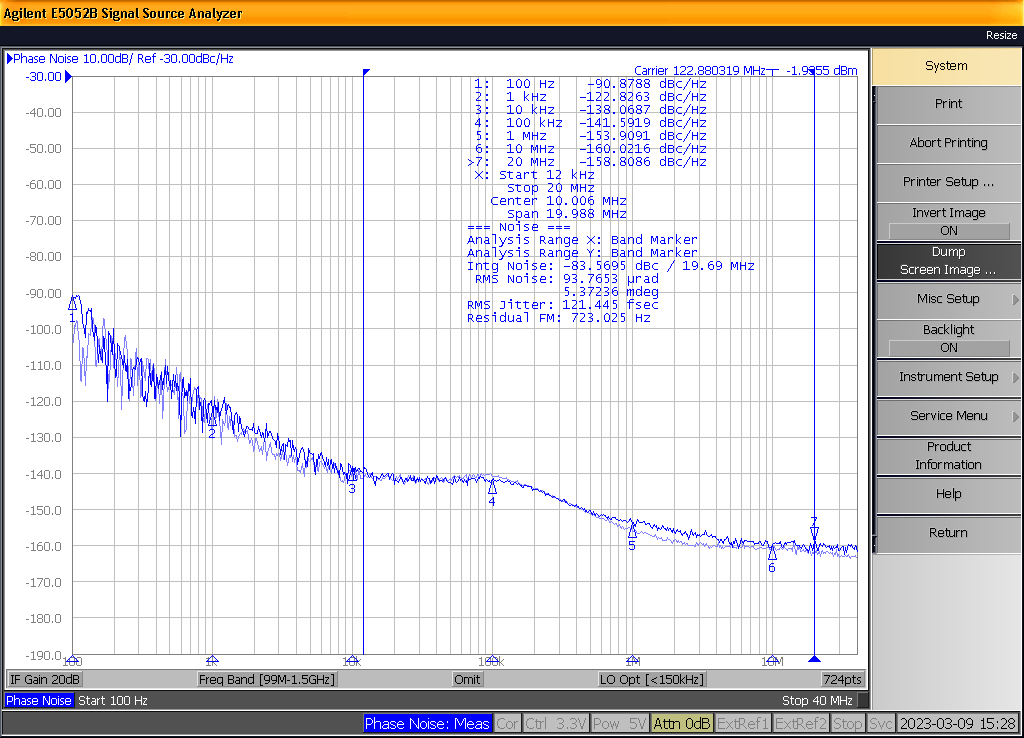

下圖為SQ82100附加抖動測試:時鐘頻率122.88MHz,附加抖動測試值為48fs。

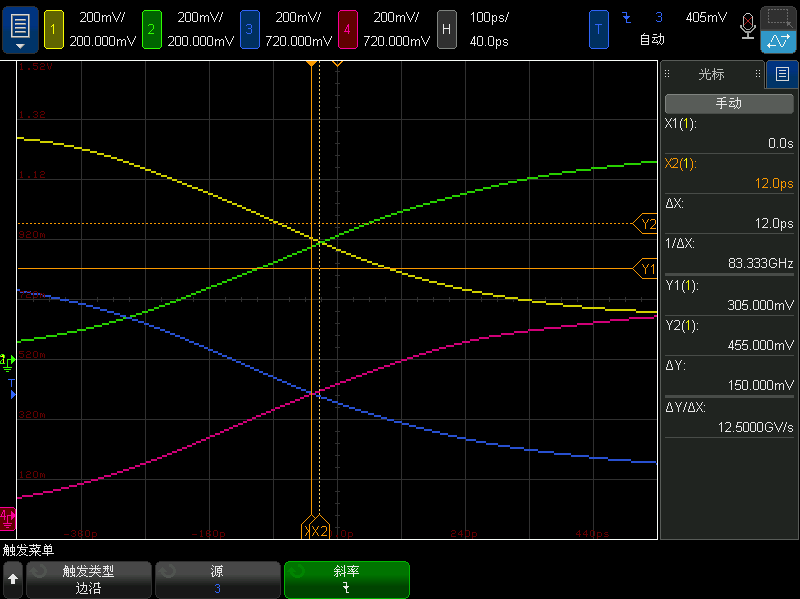

通道間skew<50ps

通道間skew將影響各PCIe終端之間的時鐘同步,甚至限制系統速率和PCIe速率。SQ82100通道間skew<50ps,實現了20路輸出時鐘的精確同步,可保證PCIe系統正常工作,充分發揮PCIe Gen5.0, Gen6.0傳輸速率。

-

時鐘緩沖器

+關注

關注

2文章

270瀏覽量

51911 -

計算機

+關注

關注

19文章

7807瀏覽量

93198 -

PCIe

+關注

關注

16文章

1461瀏覽量

88418 -

矽力杰

+關注

關注

4文章

111瀏覽量

2698

發布評論請先 登錄

CDCM1802時鐘緩沖器:高性能與靈活性的完美結合

深入解析CDCLVP2106:高性能時鐘緩沖器的卓越之選

CDCLVP1204:高性能時鐘緩沖器的技術剖析與應用探索

深入剖析CDCLVP1208:高性能時鐘緩沖器的卓越之選

深入剖析CDCLVC11xx:高性能時鐘緩沖器的卓越之選

CDCLVC11xx:高性能LVCMOS時鐘緩沖器的卓越之選

CDCLVD2106:高性能雙路 1:6 低附加抖動 LVDS 時鐘緩沖器的深度解析

CDCDB2000:PCIe時鐘緩沖器的卓越之選

探秘LMKDB11xx:PCIe時鐘緩沖器的卓越之選

探索LMKDB11xx:PCIe時鐘緩沖器的卓越之選

高性能PCIe Gen7 1.8V扇出緩沖器RC191xx:特性、應用與設計指南

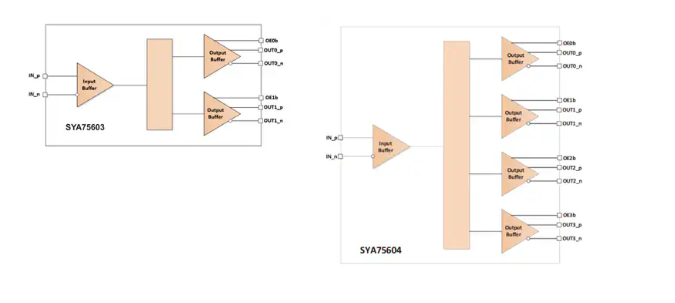

?Microchip SYA7560系列PCIe時鐘緩沖器技術總結

Diodes公司PCIe 6.0時鐘緩沖器介紹

矽力杰高性能20路PCIe時鐘緩沖器

矽力杰高性能20路PCIe時鐘緩沖器

評論