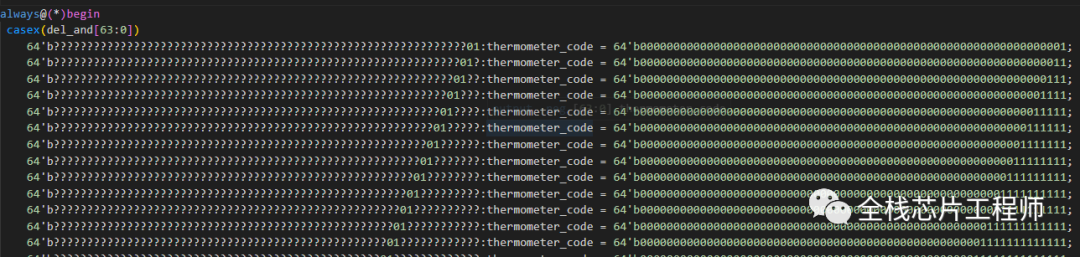

代碼如下,大家看到這個代碼有什么體會?綜合會有什么Warning?

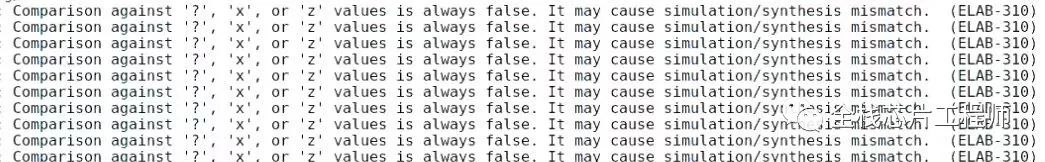

綜合會有告警如下:

注意:casez與casex都不可綜合,多用于仿真。

casex、 casez 語句是 case 語句的變形。

在casex中,casex允許"x"、"z"和"?"值在比較時被當做不關心的值。

在casez中,casez允許"z"和"?"對應的bit在比較時會被忽略,x不會被忽略。

casex 用"x" 來表示無關值

casez 用"?" 來表示無關值

兩者的實現的功能是完全一致的,語法與 case 語句也完全一致。

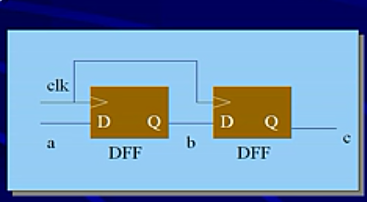

在case item中,0、1、z、x都是要比較的,不會忽略。

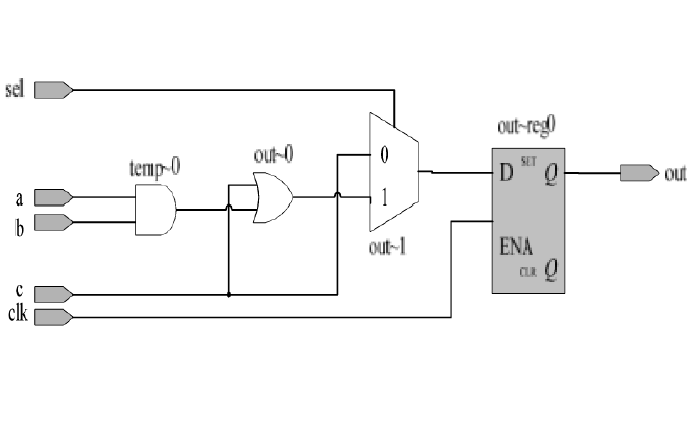

但是我們可以使用casez忽略某些bit位。在使用casez時,最好使用?表示比較時要忽略的對應比特。

case語句當條件互斥時是沒有優先級,但是條件選項不要求互斥。雖然這些條件選項是并發比較的,但執行效果是誰在前且條件為真誰被執行,詳細內容分享在知識星球。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

仿真

+關注

關注

54文章

4482瀏覽量

138251 -

Verilog

+關注

關注

30文章

1374瀏覽量

114522 -

代碼

+關注

關注

30文章

4967瀏覽量

73960

原文標題:Verilog中有casex? 注意,綜合會告警!

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

Verilog中 generate if 語句如何用systemc實現?

Verilog 中generate if語句如何用systemc實現?例如:generateif (SIZE < 8)assign y = a & b & c;else

發表于 08-28 12:06

新手求解verilog 中的生成塊語句 的意思

verilog 中的 generate for 語句好理解,但是 generate if 和 generate case 語句怎么理解??

發表于 12-21 12:44

verilog中generate語句的用法分享

generate為verilog中的生成語句,當對矢量中的多個位進行重復操作時,或者當進行多個模塊的實例引用的重復操作時,或者根據參數的定義來確定程序

發表于 12-23 16:59

verilog中if與case語句不完整產生鎖存器的原因分析

在很多地方都能看到,verilog中if與case語句必須完整,即if要加上else,case后要加上default語句,以防止鎖存器的發生,下載內容中就談到了其中原因。

發表于 09-16 09:29

?24次下載

FPGA視頻教程之Verilog中兩種不同的賦值語句的資料說明

本文檔的主要內容詳細介紹的是FPGA視頻教程之Verilog中兩種不同的賦值語句的資料說明免費下載。

發表于 03-27 10:55

?6次下載

Verilog可綜合的循環語句

Verilog中提供了四種循環語句,可用于控制語句的執行次數,分別為:for,while,repeat,forever。其中,for,while,repeat是可綜合的,但循環的次數需要在編譯之前就確定,動態改變循環次數的

發表于 10-13 12:23

?2w次閱讀

Verilog教程之Verilog HDL程序設計語句和描述方式

本文檔的主要內容詳細介紹的是Verilog教程之Verilog HDL程序設計語句和描述方式。

發表于 12-09 11:24

?53次下載

簡述Verilog HDL中阻塞語句和非阻塞語句的區別

阻塞賦值,但從字面意思來看,阻塞就是執行的時候在某個地方卡住了,等這個操作執行完在繼續執行下面的語句,而非阻塞就是不管執行完沒有,我不管執行的結果是什么,反正我繼續下面的事情。而Verilog中的阻塞賦值與非阻塞賦值正好也是這個

Verilog邏輯設計中的循環語句和運算符

“ 本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括循環語句(forever、repeat、while和for)、運算符。”

什么是SystemVerilog-決策語句-if-else語句?

決策語句(Decision statements)允許程序塊的執行流程根據設計中信號的當前值分支到特定語句。SystemVerilog有兩個主要的決策語句:if…else語句和case

Verilog中循環語句簡介

在這篇文章中,我們討論了可以在verilog中使用的不同類型的循環 - for循環,while循環,forever循環和repeat循環。

Verilog中的If語句和case語句介紹

我們在上一篇文章中已經看到了如何使用程序塊(例如 always 塊來編寫按順序執行的 verilog 代碼。

我們還可以在程序塊中使用許多語句來控制在我們的verilog設計中信

淺談Verilog中casex語句

淺談Verilog中casex語句

評論