每次作為面試官問一些RTL功耗優化的問題時候,都會希望聽到一個答案:優化了RTL的clk-gating比例。

相傳在很多年前,時序邏輯中是不存在自動時鐘門控(clk-gating)的。那個時候我還小沒趕上,如果我們回家問問家大人的話,他們會告訴我們那時候流行的D觸發器綜合應該是這樣的:

這種結構呢在沒有使能的情況下,觸發器的D端是不會有信號跳變的,能夠有限的降低一些功耗。不過大家也清楚寄存器的動態功耗主要來源于時鐘的跳變,因此這種綜合結果下時鐘信號保持翻轉,觸發器的內部電路也大多保持活躍,于是后面進一步的出現了自動時鐘門控結構。

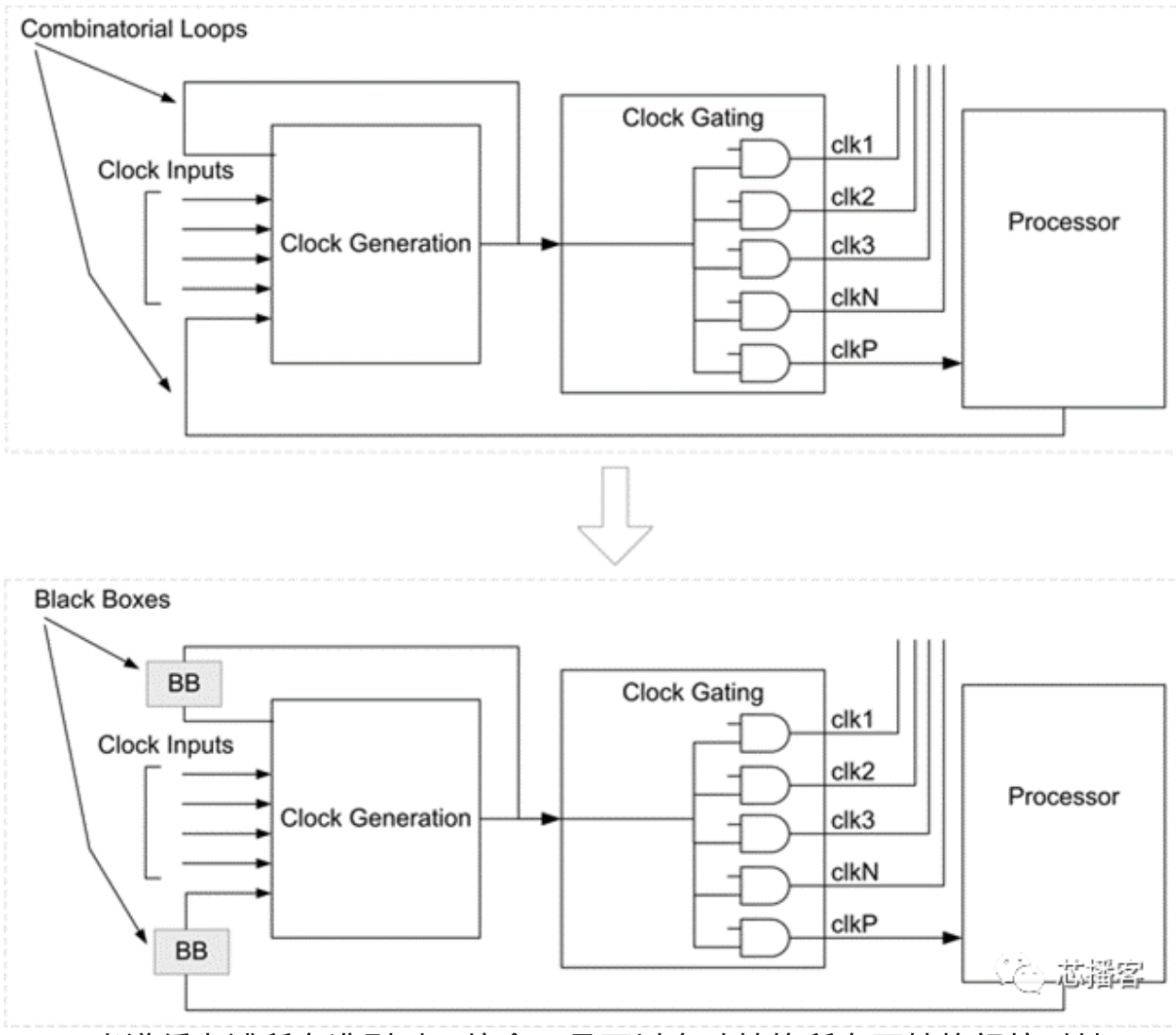

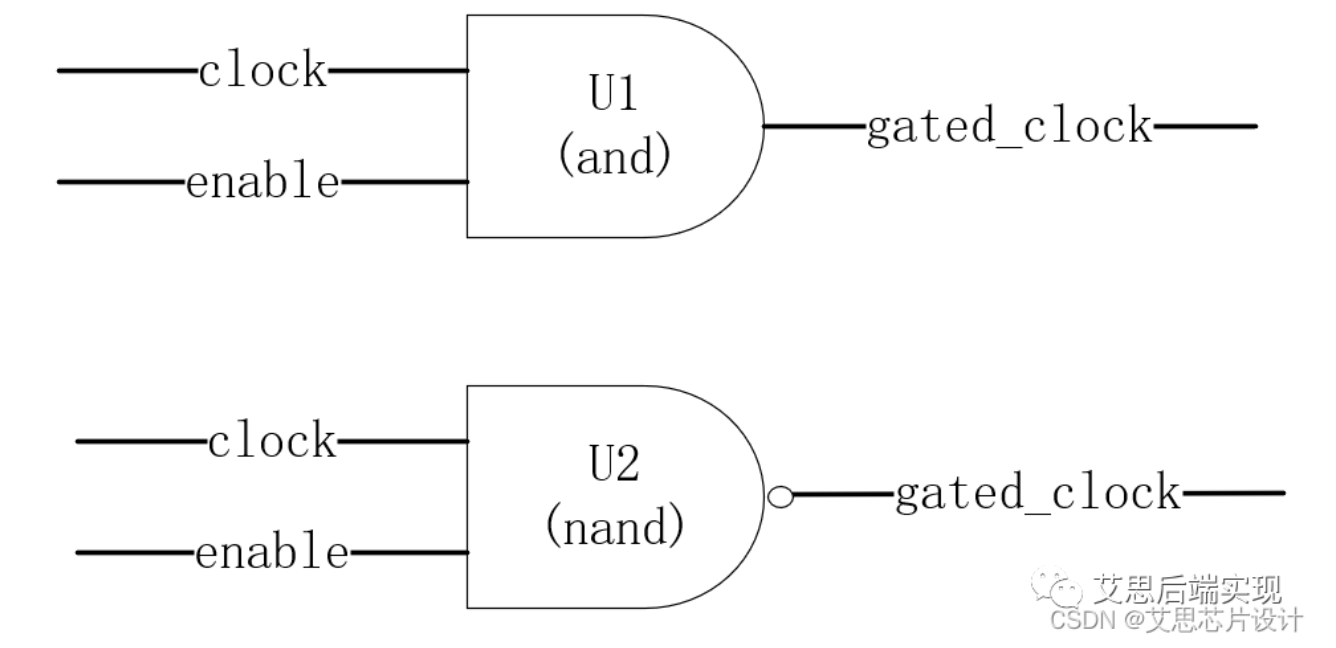

什么是自動時鐘門控結構呢?就是通過工具自動的插入一些結構,能夠在數據不跳變的時間里,關斷寄存器的時鐘輸入。那么如果來做一個最簡單的門控結構,那必然就是如此了:

當使能為低時,D觸發器的時鐘被關斷,沒有時鐘跳變自然寄存器也不會翻轉,因此Q端也不需要連線回接到D端來實現數據保持。不過這樣的結構存在一個明顯的問題,en信號顯然是邏輯電路生成的,雖然其必然滿足建立時間和保持時間要求,但是當en信號維持時間過短時,時鐘會被過早的關斷:

以及en的邏輯跳變引起的時鐘脈沖和毛刺:

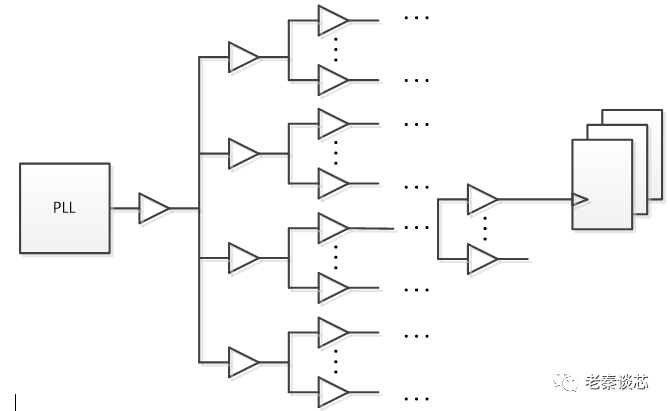

因此呢就出現一個需求,作用在clk上的en信號必須要能在時鐘上升沿到時鐘下降沿這個區間保持為一個常量,所以進一步的我們引入一個鎖存結構:

clk信號作為鎖存器的控制端,en信號為被鎖存信號,當clk為1時鎖存en信號,clk為0時透傳en信號,對應的波形如下:

通過鎖存器的鎖存功能,en信號只要在上升沿前保持穩定,即可保證產生完整的時鐘脈沖,這個結構就已經基本滿足我們的需求了。此外,大部分的廠商會在標準單元庫中提供“時鐘門控單元”,比上面的結構會多一個test_se信號,在掃描測試時候使用,因此一個完成的gating結構大體是這樣的:

而最終一個插入了自動時鐘門控的D觸發器的門電路結構圖也就完成了:

那么完成了clk-gating結構后我們需要分析一下,clk-gating的收益是什么呢?功耗收益,能夠在EN端不使能時關斷時鐘降低寄存器的動態功耗。那么對應的額外消耗支出有哪些呢?

1.面積增加,與門、或門和latch都是會增加面積的,因此工具不會無腦的插入gating,一般只有在EN控制的寄存器超過4bit時才會插入,這個值是可以設置的;

2.EN路徑的時序更加緊張,為了保證時鐘及時被開啟,EN端必須更早的實現時序收斂(或者理解為EN路徑是相對clk的,D路徑是相對gating clk的)。關于這一點綜合完的clk timing.rpt和clk gating timing.rpt對比下就會發現gating的timing路徑中一般會減去一個時間比如-100ps;

最后再解答還是經常在面試里問的問題:為什么時序邏輯里不寫else工具才能自動插入時鐘門控呢?

通過觀察結構就可以發現,時鐘門控的結果就是當EN不使能時Q端數據不發生改變,如果else分支里有賦值,那么天然就不滿足這個條件了,因此工具無法插入時鐘門控。

當然本篇所述是在觸發器級的自動時鐘門控,而整體看門控時鐘可以處于整個時鐘樹的任何節點,越靠近根部的門控時鐘對于降低功耗的作用越明顯。原因顯而易見,整個電路結構的功耗整體由三部分組成:組合邏輯產生的功耗+觸發器產生的功耗+時鐘樹功耗;靠近根部的門控結構不僅降低了大量觸發器的功耗,同時降低了區域的時鐘樹功耗(時鐘樹功耗幾乎占到了芯片功耗的50%)。

-

寄存器

+關注

關注

31文章

5615瀏覽量

130325 -

RTL

+關注

關注

1文章

395瀏覽量

62826 -

觸發器

+關注

關注

14文章

2065瀏覽量

63512 -

CLK

+關注

關注

0文章

132瀏覽量

18091 -

時鐘門控

+關注

關注

0文章

8瀏覽量

7078

發布評論請先 登錄

fpga門控時鐘問題

什么是時鐘門控?如何去實線時鐘門控的設計呢

門控時鐘與時鐘偏移研究

什么是自動時鐘門控結構呢?關于自動時鐘門控的解析

什么是自動時鐘門控結構呢?關于自動時鐘門控的解析

評論