SoC芯片無處不在,小到家電控制的MCU,大到手機芯片,我們都會接觸到。如今大部分芯片設計公司都在開發SoC芯片,一顆SoC芯片可以集成越來越多的功能,儼然它已成為IC設計業界的焦點。

高性能、高速、高帶寬的互聯和存儲的性能需求日漸占據主流。 掌握PCle協議和DDR協議可以有效地提升SoC的設計驗證、FPGA的設計、亦或是系統級的開發效率 。

今天移知小編就帶大家了解一下高性能SoC的“雙引擎”——DDR與PCIe。

一、何為SoC

1、 SoC概念與傳統的FPGA/MCU單片機的優勢

SoC是一種集成電路設計,將計算機系統的各個功能組件集成在一塊芯片上。傳統的FPGA和MCU單片機也是集成電路,但SoC在功能上更加復雜、完整。

與傳統的FPGA/MCU相比, SoC的優勢在于它將CPU、GPU、NPU、IO接口、存儲器控制器等功能模塊集成在一顆芯片上,形成一個高度集成、高性能的計算平臺 。

SoC芯片讓電子設備變得更加智能,使人們的生活變得更加便捷。

2、SoC包含哪些功能模塊

SoC集成了多個功能模塊,常見的包括:

● 中央處理器(CPU):執行計算任務和控制任務的核心處理單元。

● 圖形處理器(GPU):專門用于圖形和圖像處理,加速圖形渲染、計算和加速深度學習等任務。

● 神經網絡處理單元(NPU):專門用于加速人工智能和深度學習任務。

● 存儲器控制器:管理內存和外部存儲器的讀寫操作。

● 輸入/輸出接口(IO):用于與外部設備通信,如USB、Ethernet、HDMI等接口。

● 安全單元:提供芯片級別的安全功能,保護數據和系統免受攻擊。

二、SoC高性能體現在哪里?

高性能SoC在多個方面體現出卓越的表現:

● 計算能力:SoC集成了強大的CPU和GPU,能夠處理復雜的計算任務和圖形渲染,滿足高性能應用的要求。

● AI加速:通過集成專用的NPU,SoC能夠在處理人工智能和深度學習任務時加速運算,提升效率。

● 數據處理速度:SoC內部的高速總線和存儲器控制器使得數據訪問速度更快,減少數據處理瓶頸。

● 低功耗:雖然擁有強大性能,但高性能SoC也注重功耗的優化,以延長電池壽命和降低能源消耗。

三、SoC高性能是如何實現的?

1、更快的數據處理來源于高速接口PCIe

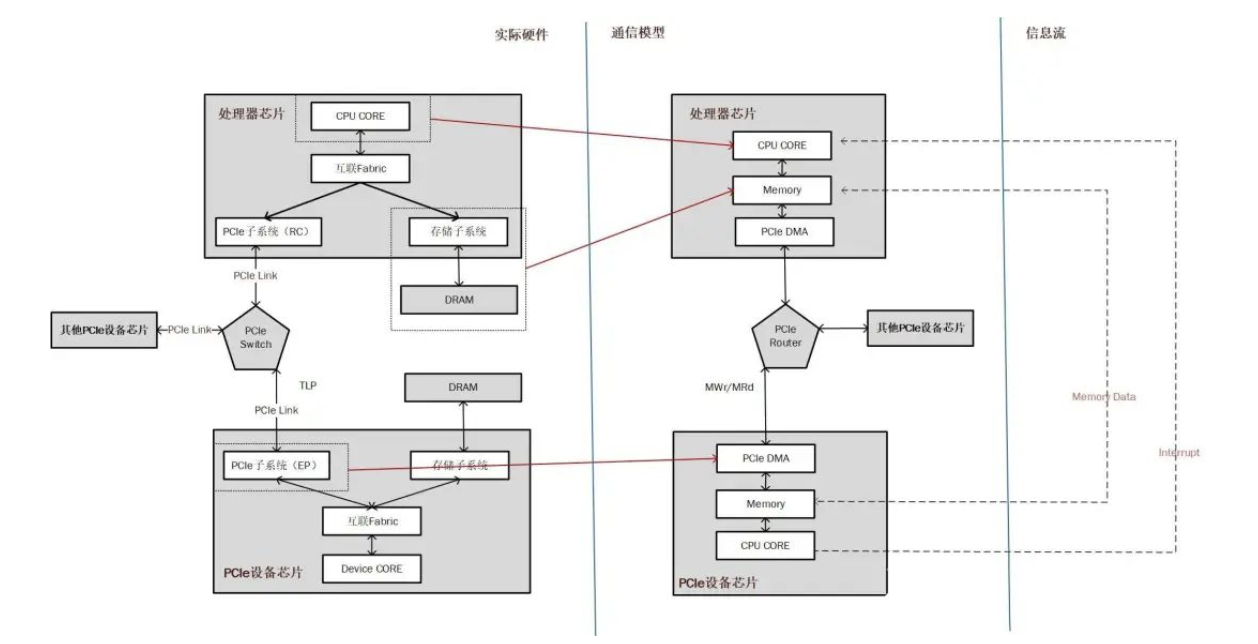

PCIe(Peripheral Component Interconnect Express)芯片是高性能SoC中的重要組成部分。它是一種高速傳輸接口,連接計算機內部的各種硬件組件,如CPU、GPU、存儲器、網絡接口等。

PCIe具有高速傳輸和可靠性的特點,使得數據在各個組件之間的傳輸更加快速和穩定。 這使得高性能計算、數據中心和企業級應用等領域得到極大的受益,加快了數據處理速度,提升了整體系統性能。

在數字IC工程師的職業生涯中,了解PCle還可以為他們提供更多的職業發展機會。掌握PCle技術可以使數字IC工程師在芯片設計、系統架構、嵌入式系統等領域中有更廣泛的應用。

掌握PCIe協議不管是對SoC的設計驗證,FPGA的設計,還是系統級的開發都提升效率,掌握PCIe協議更是成為芯片設計、驗證工程師、SoC的求職加分項,PCIe并沒有想象中那么容易掌握。

● PCIe的協議難以掌握?

國外的參考文獻的理解難易度,沒有實際項目紙上談兵的學習;空有公開協議,沒有結合案例理解上手,哪怕是已經翻譯的中文教材,也容易導致無從下手。

移知教育特邀資深工程師精心打磨 《PCIe協議全面解析》 本課程介紹了PCle總線協議的方方面面,包括系統架構、設備互聯、分層結構等, 讓大家深刻理解PCle的高帶寬、低延時的特性 。

從形象到抽象,讓學習PCIe不再晦澀難懂 ,講解最新Spec的協議特性和演進,通過協議分析儀實際抓取的數據包,生動介紹PCIe設備上的電、枚舉、及工作過程。

● PCIe設計的各種層級問題如何理解,如何解決?

PCIe 協議測試在物理層、數據鏈路層和傳輸層上都需要進行協議確認測試。鏈路訓練和狀態機(LTSSM)是協議測試里面的一個關鍵方面。鏈路訓練可以確保數據包在鏈路伙伴之間可靠地傳輸。協議分析和訓練器工具可以確定PCIe 器件是否能與其鏈接伙伴成功通信。

隨著數據速率的提升,高速串行數據鏈路的設計變得非常復雜。通道拓撲越來越復雜多變。

PCIe 互連測試通道是 PCIe 系統中最關鍵的元素之一快速確認測試PCIe 設計的參數,確保它們符合 PCIe 規范定義的性能要求,這是測試過程的一個重要環節。

● 向下兼容的難,各個版本迭代的兼容問題

各個版本的迭代兼容處理,實際的公司業務場景處理。

-

電源管理

+關注

關注

117文章

8143瀏覽量

148176 -

DDR

+關注

關注

11文章

760瀏覽量

69414 -

SoC芯片

+關注

關注

2文章

672瀏覽量

37239 -

圖形處理器

+關注

關注

0文章

202瀏覽量

27555 -

PCIe接口

+關注

關注

0文章

128瀏覽量

10635

發布評論請先 登錄

Xilinx FPGA 1/4/8通道PCIe-DMA控制器IP,高性能應用介紹

Xilinx FPGA NVMe主機控制器IP,高性能版本介紹應用

高性能NVMe主機控制器,Xilinx FPGA PCIe 3

Xilinx高性能NVMe Host控制器IP+PCIe 3.0軟核控制器IP,純邏輯實現,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

6槽雙槽位PCIe擴展塢

中國市場的高性能模擬SoC

開發QorIQ T2080的高性能網絡控制設備

高度集成的SoC用于開發高性能網絡控制設備

高性能FPGA可編程模擬前端(AFE)模擬計算引擎(ACE)特點

[資料] AI加速計算卡設計資料第636篇:基于FMC的Kintex XCKU060高性能PCIe載板

高性能低功耗的SOC平臺體系結構

『 RJIBI 』- FACE-ZU:基于FPGA的SOC高性能計算平臺

使用多代 PCIe 構建高性能互連

高性能SoC的“雙引擎”—DDR與PCIe

高性能SoC的“雙引擎”—DDR與PCIe

評論