PCI Express 和對帶寬的渴望

作為將計算、嵌入式和定制主機處理器連接到“端點”外圍設備(例如以太網端口、USB 端口、視頻卡和存儲設備)的一種方式,PCI Express? (PCIe?) 已成為參考的高性能互連。利用高速串行通信,PCIe 提供高效的點對點連接,并通過增加通道數和信號傳輸速率,提供可擴展的接口帶寬。

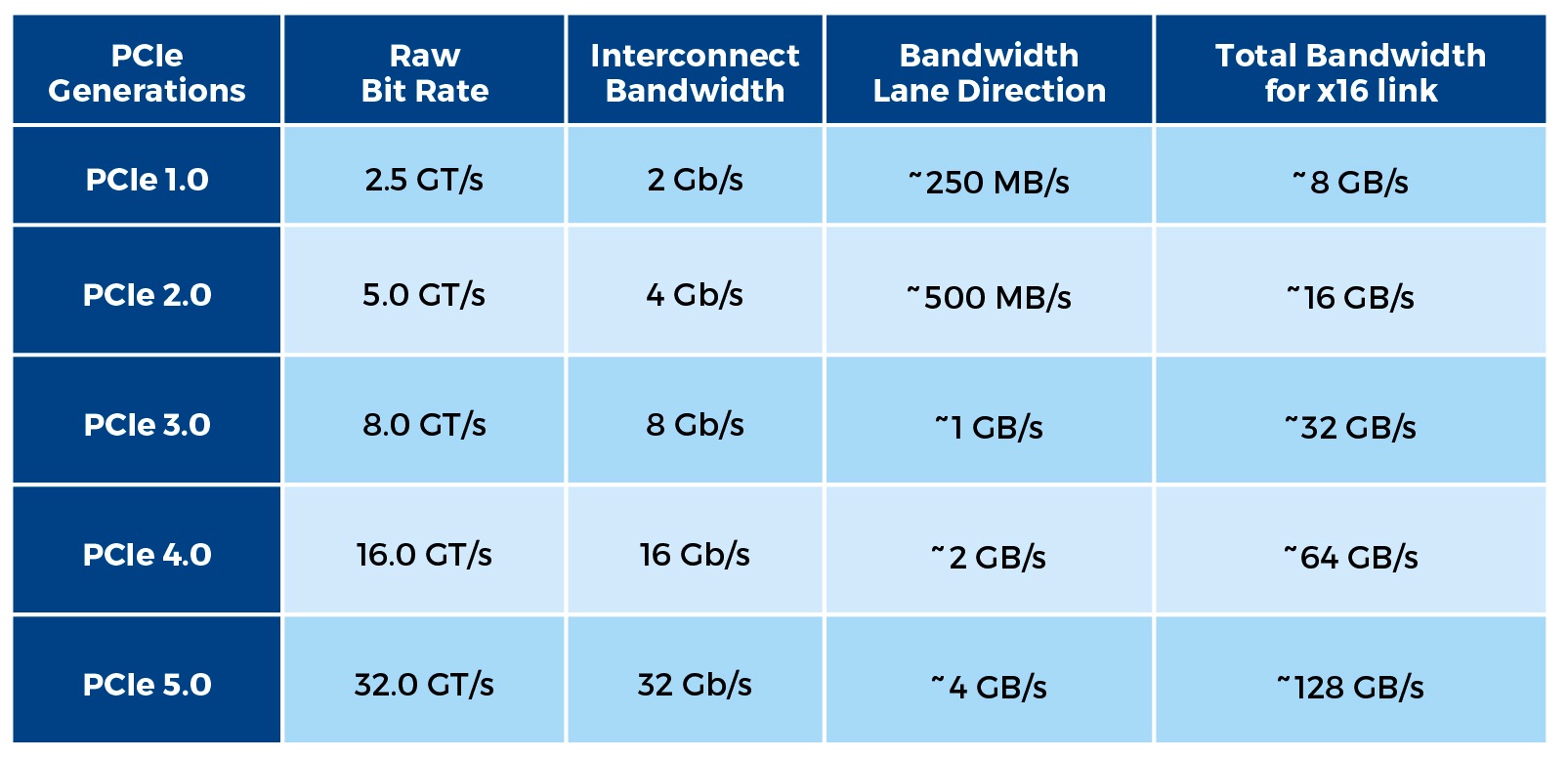

PCIe 1.0 規范于 2002 年發布,以每秒 2.5 千兆傳輸 (GT/s) 的速度運行,總 x16 接口帶寬為 8GByte/s。隨著第二代 PCIe 2.0 規范的到來,帶寬隨后在 2006 年翻了一番,并在 2010 年再次將帶寬提高到 32GByte/s,以滿足包括高端 PC、游戲、企業計算和網絡。

PCI Express 已成為各種系統設計的參考高性能互連。

(來源:Diodes Inc.)

最近,基于云的服務(例如社交媒體和視頻流)的快速普及對大型數據中心內的高速連接提出了新的和更苛刻的要求。

現在,隨著物聯網時代的到來,安裝在智能城市和基礎設施、智能工廠和其他工業資產、商業和住宅建筑以及用于健身和醫療跟蹤的可穿戴設備的聯網傳感器將為超大規模數據中心生成大量數據,捕獲、存儲、處理和分析。這些力量正在推動對下一代 PCIe 的需求,以有效地將數據中心服務器連接到高速以太網、網絡附加存儲和 AI 加速器。

聯網汽車將進一步增加數據負載,增加實時壓力,以實現更高水平的自動駕駛并最終實現全自動駕駛汽車。在數據中心的背后,訓練用于 AI 推理的神經網絡是一項計算密集型任務,它極大地暴露了外圍通信的瓶頸。

隨著這些各種因素現在發揮作用,PCIe 再次向前發展的時機已經成熟。2017 年發布的 PCIe 4.0 緊隨其后的是 2019 年發布的 PCIe 5.0。圖 1 顯示了每個 PCIe 版本提供的總速度。

圖 1:PCIe 版本提供的總速度(來源:Diodes Inc.)

隨著領先的數據中心從 100Gb 以太網過渡到最新的 400Gb 規范,PCIe 5.0 有望得到廣泛應用。在實踐中,PCIe 帶寬的增加或多或少與以太網速度的進步保持同步,理想情況下保持兩種標準之間的平衡有助于避免性能瓶頸。

“傳統” PCI 標準保持最新

隨著 PCIe 5.0 產品開始進入市場,并且隨著 PCI 特別興趣小組 (PCI-SIG) 最近宣布下一代 PCIe 6.0 將于 2021 年完成的工作已經開始,PCIe 是性能的首選協議- 在可預見的未來,饑餓的外圍通信。

同時,向后兼容性是 PCIe 沿襲的一個關鍵優勢。由于 PCIe 規范沒有到期日期,因此幾代產品可以在市場上共存,甚至在同一個應用程序中。這對系統設計人員來說是一個優勢:雖然新一代 PCIe 不斷涌現以解決日益增長的帶寬需求,但早期的迭代繼續在個人計算、游戲以及一些企業計算和網絡應用等大量場景中提供價值。

解決實施挑戰

各種 PCIe 代之間的向后兼容性使系統能夠在新芯片可用時受益于更高的傳輸速度,而設計更改最少。另一方面,不斷提高的信號速度會給信號裕量帶來額外壓力,并會增加設計復雜性。此外,顯然需要能夠橋接 PCIe 和從 PCIe 橋接的解決方案,不僅在傳統接口之間,而且在 USB 或圖形端口等其他接口之間。

為了應對這些挑戰,設計人員需要使用支持各種 PCIe 代的設備,例如時鐘發生器、時鐘緩沖器、控制器、數據包交換機/橋、ReDriver? 芯片和高速多路復用器,如圖 2 所示。

圖2:Diodes Inc.提供的PCIe解決方案示例(來源:Diodes Inc.)

ReDriver芯片可以為提高高速系統中的信號完整性提供一種經濟高效且方便的解決方案。使用均衡和預加重等技術,通過引入最小延遲的輸出驅動器,ReDriver補償傳輸線損耗,以恢復信號裕度并最小化抖動,以確保接收器的低誤碼率。與集成了時鐘和數據恢復等附加功能的重定時器相比,ReDriver引入了低延遲,相對經濟且易于實現。圖2顯示了當信號需要在較長的PCB軌道上驅動時,如到外部圖形卡或通過電纜到外部存儲器時,如何使用PCIe ReDriver。這些ReDrivers完全向后兼容,支持所有以前的PCIe代。

網橋和交換機滿足各種類型的主機和終端設備之間的接口要求。包橋通常在OSI參考模型的兩層之間或兩個協議之間提供接口。圖2還顯示了如何使用網橋連接PCIe和傳統PCI標準(包括PCI-X),或USB端口或UART總線接口。分組交換機是多端口/多通道設備,通常用于將單個根復合體擴展到多個具有多通道的端口,以訪問其他對等系統,如外圍設備或線路卡。

除了具有各種端口配置和轉換能力的單個分組網橋和交換機外,PCIe分組交換機和PCIe-to-USB2.0網橋的功能還結合在設備中,例如Diodes Incorporated的PI7C9X442SL PCI Express to USB 2.0“swidge”。該多功能設備可以從一個PCIe x1上游端口扇出到兩個x1下游端口和四個USB 2.0端口,并允許系統主機處理器同時訪問多個PCIe和USB設備。

Diodes股份有限公司等公司可以提供無源雙向PCIe 1.0、PCIe 2.0或PCIe 3.0信號多路復用器/解復用器組合,以將單個PCIe通道連接到多個通道,以擴展用于圖形或計算的帶寬。這些設備還可用于啟用單個多協議接口的連接。

時鐘緩沖器通常可以將單個參考信號作為輸入并產生多個輸出,以便在 PCB 周圍更廣泛地分布。時鐘緩沖器 IC 提供多種配置,Diodes 提供專有的 PLL 設計,確保抖動保持在 PCIe 要求范圍內。時鐘發生器可以生成具有極低輸出抖動的特定頻率的時鐘信號,使其適用于 PCIe 以及其他系統時鐘。設計人員可以找到各種合適的設備,例如 Diodes 的 1.8V PI6CG18xxx 和 1.5V PI6CG15xxx PCIe 4.0 時鐘發生器和 2 通道、4 通道和 8 通道配置的緩沖器,它們與所有先前的 PCIe 代兼容。通過在片上集成終端,這些器件在每個輸出端節省了四個外部電阻器,從材料清單中減少了多達 32 個組件。

結論

PCIe 是適用于從嵌入式和桌面計算到高帶寬數據中心連接和神經網絡訓練的應用的首選高性能互連。設計人員可以利用早期 PCIe 標準的長使用壽命,以及舊版和下一代規范之間的向后兼容性,以經濟高效的方式滿足各種系統要求。通過訪問包含橋接器、緩沖器、轉接驅動器、開關和復用/解復用 IC 等功能的器件組合,設計人員可以為要求苛刻的應用提供高效的解決方案。

審核編輯 黃昊宇

-

PCI

+關注

關注

5文章

689瀏覽量

134459 -

PCIe

+關注

關注

16文章

1470瀏覽量

88850

發布評論請先 登錄

青翼基于KU115FPGA 高性能數據預處理載板-PCIe信號處理板-FPGA載板

探索Renesas 89HPES24NT6AG2:高性能PCIe Gen2系統互連交換機

解析IDT 89HPES12NT12G2:高性能PCIe Gen2系統互連交換機的卓越之選

IDT 89HPES32NT24BG2:高性能PCIe Gen2系統互連交換機深度解析

多Chiplet異構集成的先進互連技術

瀾起科技發布PCIe 6.x/CXL 3.x AEC解決方案

從內存接口到PCIe/CXL、以太網及光互連,高速互連芯片市場分析

使用多代 PCIe 構建高性能互連

使用多代 PCIe 構建高性能互連

評論