在進行多層PCB的設計時,PCB的層疊是其中一個非常重要的環節,層疊的好壞對于產品的性能有直接的影響,下面我們將為大家梳理一下多層板層疊的一些基本原則。

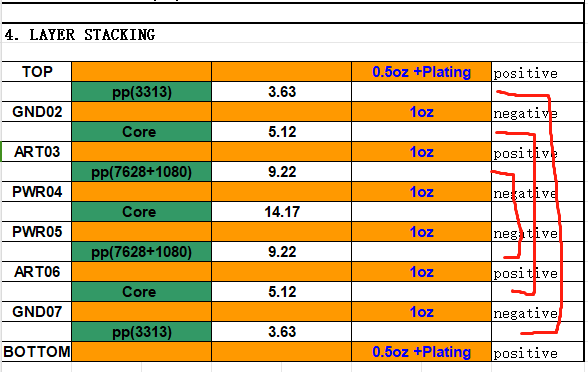

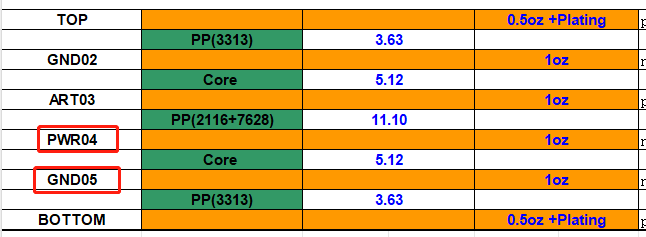

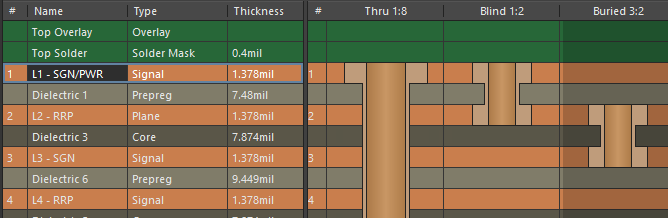

首先,我們需要滿足信號層與地層相鄰疊放,在有相鄰地層的作用下可以有效的減小信號之間的串擾和電磁輻射,地層可用于提供電流回路和屏蔽信號層的電磁輻射,特別是在高頻高速的PCB設計中,在有相鄰地層的情況下也能避免信號跨分割的問題,所以在PCB設計時我們的重要信號也應該放置在靠近地層的信號層中。

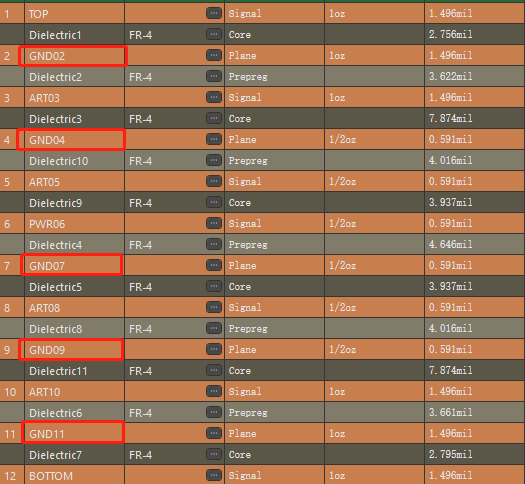

第二點,在疊層時應該要保持層疊的對稱性,層疊是否對稱關系到后期PCB板成品的彎曲度,如果層疊不對稱會導致板子成品出現翹曲的情況,從而進一步影響板子的貼片,可能會出現焊接不牢固,虛焊等情況。

第三點,與元器件相鄰的層要設置為地平面,可以為器件提供屏蔽的作用,以及避免表底層信號出現跨分割情況(跨分割指的是一個信號的相鄰參考層經過了多個平面)

第四點,電源層應該盡可能的與地平面相鄰,構成平面電容,從而降低電源平面阻抗

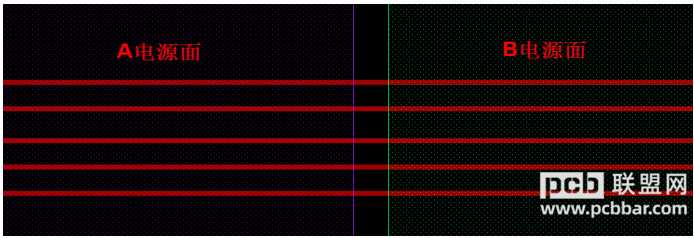

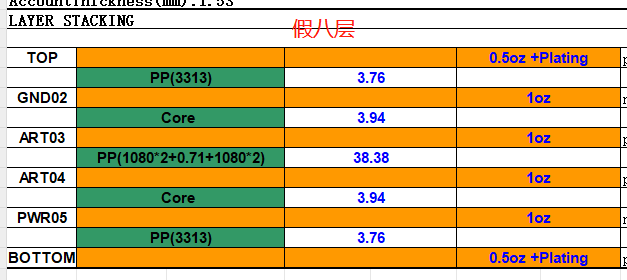

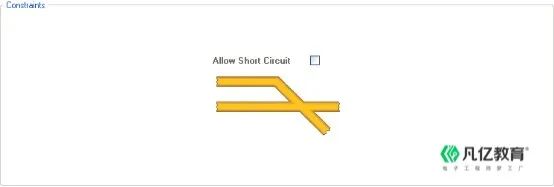

第五點,盡量不要出現相鄰的平行布線層,相鄰平行布線層間串擾會非常大,從而影響信號質量,影響板子性能,如果在出現相鄰布線層的情況盡量一層走橫的,一層走豎的,或者增加這兩個層之間的厚度,把間距拉開也能有效解決串擾問題,比如我們常說的“假八層”設計。

-

pcb

+關注

關注

4414文章

23925瀏覽量

425544 -

PCB設計

+關注

關注

396文章

4930瀏覽量

95618 -

疊層

+關注

關注

0文章

30瀏覽量

10326

原文標題:PCB設計中的疊層原則

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

技術資訊 I PCB設計三大頑疾:規則亂、布線慢、疊層偏——Allegro X Designer 的系統級解法

西門子PCB疊層設計工具Z-planner Enterprise 2510版本的新增功能

疊層固態電容:小型化封裝,釋放PCB更多空間

從入門到精通:PCB設計必須遵守的5大核心原則

貼片電感代理-疊層電感的實際應用

PCB疊層設計避坑指南

PCB疊層設計避坑指南

原理圖和PCB設計中的常見錯誤

Altium Designer中PCB設計規則設置

PCB設計中的疊層原則

PCB設計中的疊層原則

評論