隨著時(shí)間的推移摩爾定律逐漸趨于極限,人們迎來(lái)了后摩爾時(shí)代。封裝技術(shù)即將成為摩爾定律的新拐點(diǎn),為芯片集成的歷史翻開了新的一頁(yè)。

遙想當(dāng)年,戈登·摩爾創(chuàng)造了摩爾定律,為半導(dǎo)體行業(yè)發(fā)展指明了一條羅馬大道。不過(guò),畢竟理論自1965年至今已有五十余年,節(jié)點(diǎn)已微縮至幾近納米極限,行業(yè)摩爾定律逐漸放緩,甚至有言道“摩爾定律已死”。

擺在現(xiàn)實(shí)的是,納米節(jié)點(diǎn)轉(zhuǎn)換越來(lái)越難了,物理極限越來(lái)越近了。處在后摩爾時(shí)代的企業(yè)只能默默面對(duì)納米極限的逼近嗎?不,摩爾定律探索中出現(xiàn)了新拐點(diǎn),即封裝技術(shù)。

封裝技術(shù)成為摩爾定律的新拐點(diǎn)

摩爾定律到底是什么,封裝技術(shù)和摩爾定律到底有什么關(guān)系?1965年起初,戈登·摩爾表示集成電路上可容納的元器件數(shù)量約18個(gè)月便會(huì)增加一倍,后在1975年將這一定律修改為單位面積芯片上的晶體管數(shù)量每?jī)赡昴軐?shí)現(xiàn)翻番。

回望摩爾定律整個(gè)歷史,讓晶體管溝道進(jìn)一步縮短,突破物理極限也曾先后經(jīng)歷多個(gè)瓶頸。首先碰到的便是半導(dǎo)體材料的限制,由此行業(yè)發(fā)明了電化學(xué)鍍銅和機(jī)械平面化的雙鑲嵌結(jié)構(gòu)技術(shù);而后遇到了設(shè)備物理限制,Si柵極和SiO2柵極電介質(zhì)材料被金屬柵極和高K電介質(zhì)取代;再到193nm節(jié)點(diǎn)以上,受到光刻技術(shù)限制,行業(yè)光刻技術(shù)得以發(fā)揚(yáng),在制程節(jié)點(diǎn)45nm-32nm下產(chǎn)生了浸沒工藝、16nm-10nm下產(chǎn)生了多重曝光工藝、7nm-5nm則引入了極紫外線(EUV)工藝。

因此,可以看出,為了延續(xù)摩爾定律,專家絞盡腦汁想盡各種辦法,包括改變半導(dǎo)體材料、改變整體結(jié)構(gòu)、引入新的工藝。但不可否認(rèn)的是,摩爾定律在近幾年逐漸放緩。10nm、7nm、5nm……芯片制程節(jié)點(diǎn)越來(lái)越先進(jìn),芯片物理瓶頸也越來(lái)越難克服。

因此,業(yè)內(nèi)專家指出了后摩爾時(shí)代的硅技術(shù)的發(fā)展方向。一種是繼續(xù)采用“硅-馮諾依曼”范式,通過(guò)改變結(jié)構(gòu)形成新型器件,使得摩爾定律能夠繼續(xù);另一種則是采用類腦模式的新興架構(gòu),利用3D封裝模擬神經(jīng)元特性,構(gòu)建存算一體的計(jì)算,這種架構(gòu)不僅低功耗,還擁有并行性。

那么封裝究竟和摩爾定律有什么關(guān)系呢?

簡(jiǎn)單來(lái)說(shuō),封裝能夠減少芯片間的凸點(diǎn)間距,增大凸點(diǎn)密度。整體的密度越大,實(shí)際上也代表著單位面積上晶體管數(shù)量越密。所以說(shuō),封裝雖然和摩爾定律沒有直接關(guān)聯(lián),但卻又影響著摩爾定律的發(fā)展。

封裝技術(shù)正邁向新的凸點(diǎn)間距

封裝技術(shù)是如何發(fā)展的?

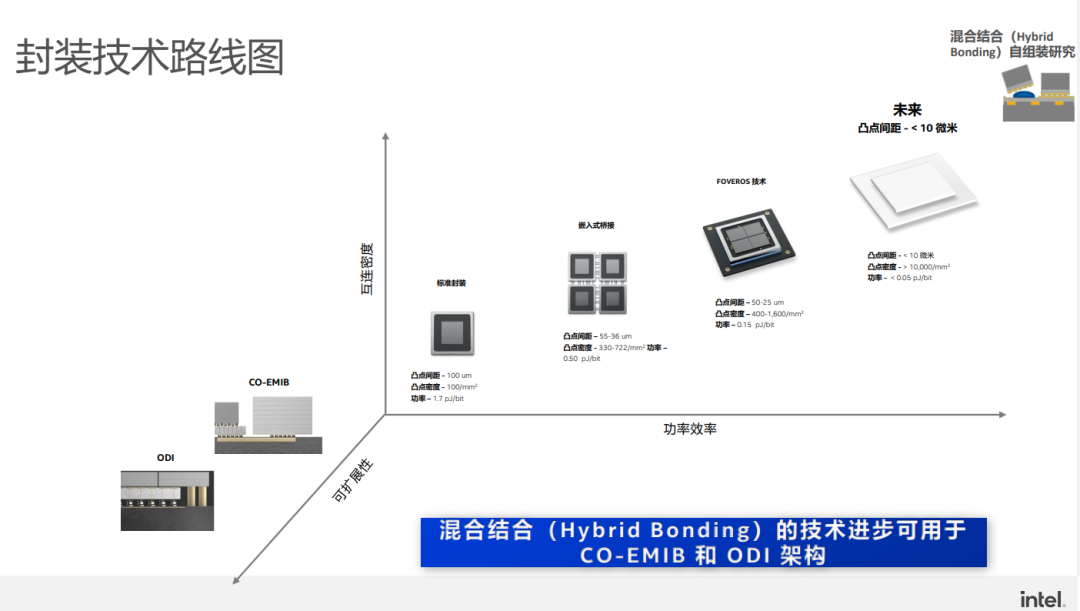

從標(biāo)準(zhǔn)封裝到EMIB(嵌入式多管芯互聯(lián)橋接)再到Foveros,凸點(diǎn)間距從100μm縮減到50-25μm。未來(lái)要做到小于10μm的凸點(diǎn)間距。

EMIB是一種2.5D高密度微縮技術(shù),通過(guò)EMIB技術(shù)可以實(shí)現(xiàn)更好的導(dǎo)線密度。通過(guò)將硅中介層放入封裝內(nèi),因而可進(jìn)行局部高密度布線,并非全部芯片的高密度布線。利用EMIB技術(shù),可將典型FCBGA(有機(jī)封裝)的IO層提升至256-1024 IO/mm/層。這項(xiàng)技術(shù)能夠?qū)崿F(xiàn)55-36μm的凸點(diǎn)間距和每平方毫米330-722/m㎡的凸點(diǎn)密度,功率可以控制在0.5pJ/bit。

Foveros則是一種3D高密度微縮技術(shù),如若在此基礎(chǔ)上進(jìn)行完美的設(shè)計(jì),IO就甚至可以達(dá)到從400至10000 IO/mm2。這項(xiàng)技術(shù)能夠?qū)崿F(xiàn)50-25μm的凸點(diǎn)間距和400-1600/m㎡的凸點(diǎn)密度,功率可以控制在0.15pJ/bit。

既然目標(biāo)是10μm以下,那么如何實(shí)現(xiàn)?答案是“混合結(jié)合”的Hybrid bonding技術(shù)。利用該技術(shù)不僅能夠?qū)崿F(xiàn)10μm凸點(diǎn)間距的愿景,還能使得凸點(diǎn)密度達(dá)到10000/m㎡,功率控制在0.05 pJ/bit。并且,混合結(jié)合技術(shù)可以使用與晶片到晶圓,也可以使用與晶圓到晶圓。

Hybrid bonding能夠使兩芯片間實(shí)現(xiàn)更多互連,也不必做扇入(fan-in)和扇出(fan-out)。有了更簡(jiǎn)單的電路,可以使用更低的電容,以降低通道的功率。

隨著摩爾定律的繼續(xù)推進(jìn),芯片的尺寸可能會(huì)變得越來(lái)越小,為了保證足夠的帶寬,必須要在導(dǎo)線上下功夫。整個(gè)小芯片尺寸變得越來(lái)越小,其實(shí)隨著間距變得越來(lái)越短,傳統(tǒng)基于焊料的技術(shù)已經(jīng)快要到極限了,這就是為什么要使用全新的技術(shù)混合結(jié)合Hybrid bonding封裝。

那么Hybrid Bonding到底和Foveros有什么區(qū)別,憑什么混合結(jié)合封裝就能減少凸點(diǎn)間距?

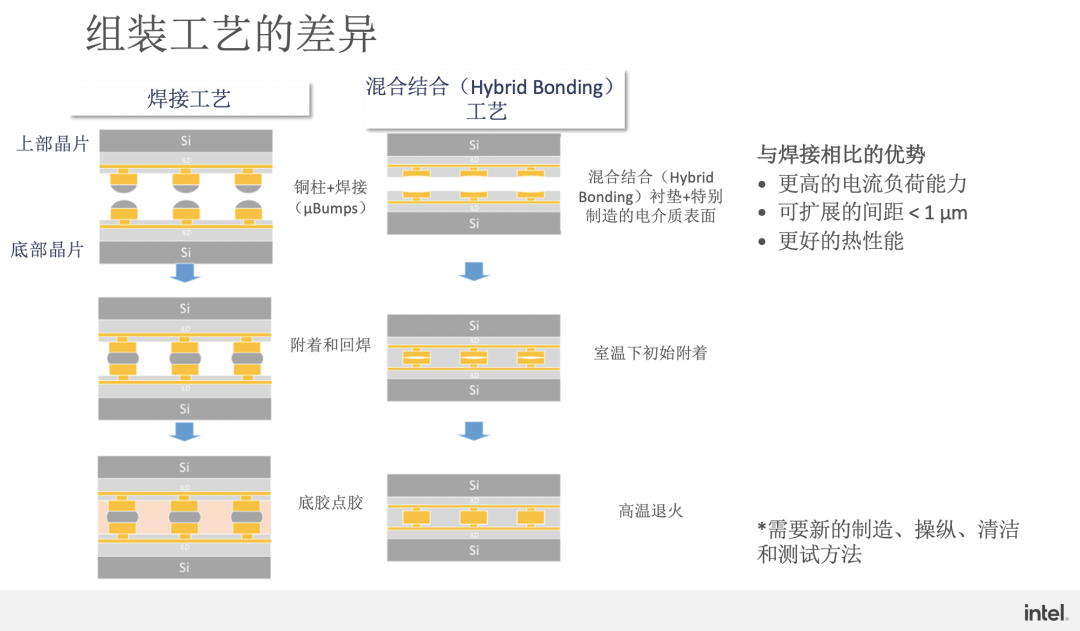

硅晶片分布在頂部和底部,中間則是帶焊料的銅柱,將它們附著在一起和回焊,讓它升溫。這些芯片之間有不同的溫度,需要熔化焊料,將其放在一起,進(jìn)行連接和回焊,再制作電氣接頭。在這之后,進(jìn)行底部填充膠的分配,將填充有環(huán)氧樹脂的硅放入模具之間以確保它們密封并能夠完成放入并組裝。

Hybrid Bonding與Foveros的焊接工藝不同,與焊接技術(shù)相反,混合結(jié)合技術(shù)使電介質(zhì)的芯片非常光滑,而不是有突出的凸點(diǎn),甚至實(shí)際上還會(huì)略微凹陷。當(dāng)采用混合結(jié)合技術(shù)將這兩個(gè)組件放在一起時(shí),不必升高溫度,可以在室溫粘合兩個(gè)組件。在其相互附著后,再升高溫度并進(jìn)行退火,銅在這時(shí)會(huì)膨脹,從而形成電氣連接。Swan強(qiáng)調(diào),這是非常有用的,因?yàn)檫@樣可獲得更高的載流能力。

甚至可以將間距縮小到 10 微米以下。這樣在這些接口之間獲得了比底部填充和緊密的銅密度更好的熱性能。不過(guò),當(dāng)使用混合結(jié)合技術(shù)時(shí),將需要一種新的制造、清潔和測(cè)試方法。

實(shí)際上,這種更小的間距頗具吸引力,能夠聯(lián)動(dòng)許多技術(shù)的進(jìn)化。

封裝技術(shù)是三位一體的

除了在功率效率和互連密度上的提升,封裝技術(shù)還分出可擴(kuò)展性這個(gè)維度。這一維度之上,包括Co-EMIB和ODI兩個(gè)技術(shù)。

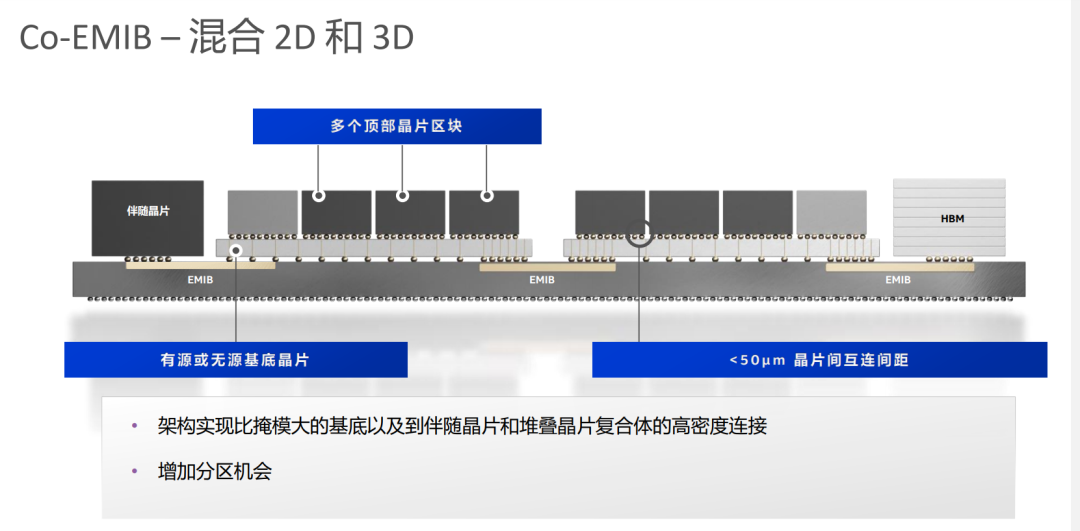

Co-EMIB是融合EMIB技術(shù)和Foveros技術(shù)的一種封裝,是融合2.5D和3D的技術(shù)。如果將EMIB理解成水平方向,F(xiàn)overos理解成垂直方向,那么Co-EMIB就是三位一體的兼顧兩個(gè)方向的封裝方式,能夠真正發(fā)揮高密度微縮的效果。

可以說(shuō),可擴(kuò)展的Co-EMIB的技術(shù)是發(fā)揮所有封裝方式優(yōu)勢(shì)的平臺(tái),也是2.5D和3D封裝技術(shù)碰撞交融、各自發(fā)揮優(yōu)勢(shì)的匯集地。

另一個(gè)頗具可擴(kuò)展性的技術(shù)就是ODI(全方位互連技術(shù))。根據(jù)此前的介紹,在常規(guī)的疊加方式下,下面的基礎(chǔ)裸片必須是較大的,它要大于上面疊加的所有小芯片的總和。通過(guò)ODI技術(shù)可以改變這一點(diǎn),兩者之間可以進(jìn)行更好的協(xié)調(diào),并且可以上下做到面積統(tǒng)一。

總結(jié)

實(shí)際上現(xiàn)今封裝技術(shù),不僅達(dá)到了晶體管的級(jí)別,使得成為摩爾定律探索的新關(guān)鍵,還與未來(lái)新架構(gòu)息息相關(guān)。

在摩爾定律逐漸逼近極限之時(shí),未來(lái)集成電路行業(yè)在后摩爾時(shí)代不僅要著眼于半導(dǎo)體材料、結(jié)構(gòu)和工藝,還要注意封裝互連技術(shù)對(duì)晶體管的影響,或許這是未來(lái)破局的關(guān)鍵。

-

摩爾定律

+關(guān)注

關(guān)注

4文章

640瀏覽量

81075 -

封裝

+關(guān)注

關(guān)注

128文章

9297瀏覽量

148881 -

半導(dǎo)體材料

+關(guān)注

關(guān)注

11文章

578瀏覽量

30887

原文標(biāo)題:摩爾定律不會(huì)死去!這項(xiàng)技術(shù)將成為摩爾定律的拐點(diǎn)

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

2.5D封裝關(guān)鍵技術(shù)的研究進(jìn)展

3D IC設(shè)計(jì)中的信號(hào)完整性與電源完整性分析

Chiplet,改變了芯片

芯片封裝的功能、等級(jí)以及分類

借助AMD無(wú)頂蓋封裝技術(shù)應(yīng)對(duì)散熱挑戰(zhàn)

當(dāng)摩爾定律 “踩剎車” ,三星 、AP、普迪飛共話半導(dǎo)體制造新變革新機(jī)遇

AI狂飆, FPGA會(huì)掉隊(duì)嗎? (上)

Chiplet與3D封裝技術(shù):后摩爾時(shí)代的芯片革命與屹立芯創(chuàng)的良率保障

晶心科技:摩爾定律放緩,RISC-V在高性能計(jì)算的重要性突顯

鰭式場(chǎng)效應(yīng)晶體管的原理和優(yōu)勢(shì)

電力電子中的“摩爾定律”(2)

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規(guī)則

電力電子中的“摩爾定律”(1)

玻璃基板在芯片封裝中的應(yīng)用

淺談Chiplet與先進(jìn)封裝

摩爾定律不會(huì)死去!這項(xiàng)技術(shù)將成為摩爾定律的拐點(diǎn)

摩爾定律不會(huì)死去!這項(xiàng)技術(shù)將成為摩爾定律的拐點(diǎn)

評(píng)論