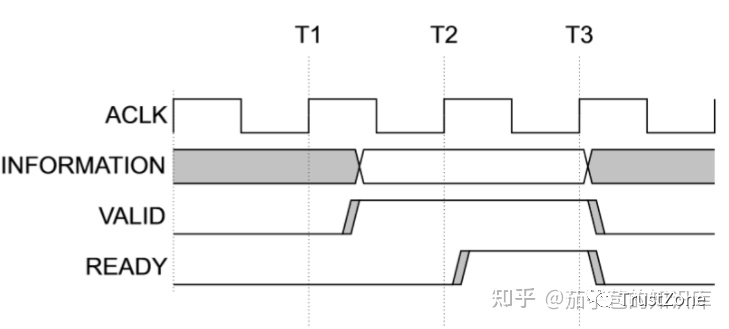

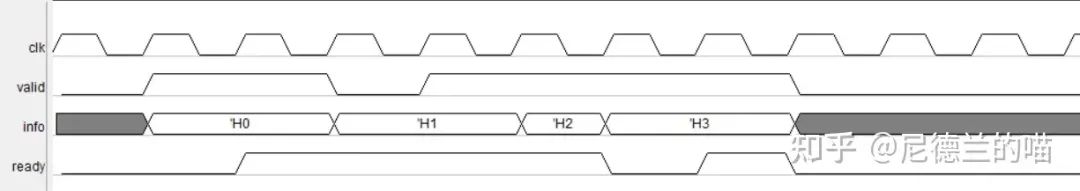

(1)valid信號先到達

主機valid信號早早就到了,T2時刻并沒有見到接收方的ready信號。只能在T3時刻傳輸完成。

協(xié)議規(guī)定在這種情況下,valid信號一旦置起就不能置低,直到完成握手,至少傳輸一周期數(shù)據(jù)。 協(xié)議另外規(guī)定:發(fā)送方不能通過等待接收方 READY信號來確定置起 VALID 信號的時機。

通俗來講就是設計發(fā)送方邏輯時,不能將 READY 信號作為置高 VALID 邏輯的條件,比如將 READY 信號通過組合邏輯生成 VALID信號,但接收方的ready信號按照協(xié)議可以依賴發(fā)送方的valid信號。

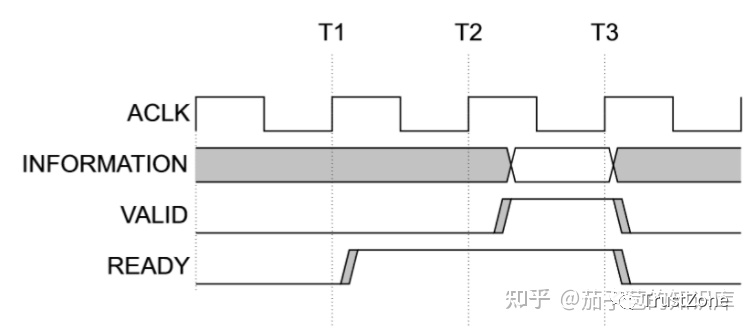

(2)ready信號先到達

ready信號很自由,可以等待valid信號到來之后再做響應,也可在valid信號到來前就置高,表示接收端已經(jīng)做好準備。

而且,READY 信號與 VALID 不同,接收方可以置起 READY 之后發(fā)現(xiàn):其實我好像還挺忙,然后置低 READY 信號。只要此時 VALID信號沒有置起,這種操作是完全可以。

(3)tips

AXI總線是全雙工的,全雙工就意味著該總線的讀寫通道是分開的,互不影響,那就意味著每條通道都是單向傳輸,單向傳輸?shù)耐ǖ谰鸵馕哆@兩端節(jié)點的身份有差距,在AXI總線傳輸中,通道兩端分為Master和Slave,主機總是發(fā)起讀寫請求的一方。

常見主機有CPU、DMA,而存儲介質(zhì)控制器則是典型的從機。主機可能通過從機讀取或者寫入存儲介質(zhì)。而顯然從機不可能主動向 CPU 寫入數(shù)據(jù)。

-

信號

+關(guān)注

關(guān)注

12文章

2921瀏覽量

80365 -

總線

+關(guān)注

關(guān)注

10文章

3050瀏覽量

91810 -

AXI

+關(guān)注

關(guān)注

1文章

145瀏覽量

18003

發(fā)布評論請先 登錄

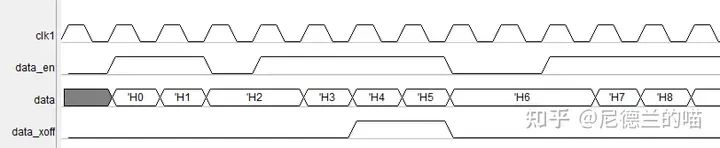

valid-ready握手協(xié)議和enable-xoff協(xié)議對比

數(shù)碼相機充電器對電池的充電狀態(tài)判斷方式有哪三種?

三種投影機散熱技術(shù)是哪三種

電路的三種工作狀態(tài)分別是什么

網(wǎng)絡拓撲結(jié)構(gòu)哪三種

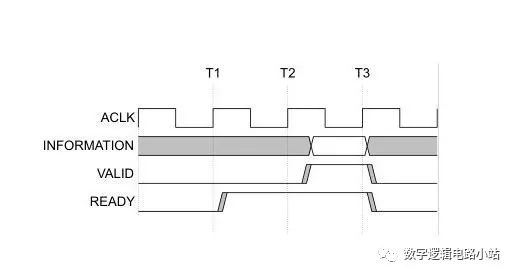

在握手協(xié)議中的Valid及data打拍技巧

半導體的導電特性有哪三種

電路短路的三種情況

Valid-Ready握手協(xié)議的介紹與時序說明

valid與ready信號有哪三種情況

valid與ready信號有哪三種情況

評論