對于波形和電平不標準的時鐘信號一般應進行怎樣的處理?

時鐘信號是數字系統中非常重要的信號之一,它用于同步各種數字電路的操作,以確保正確的數據傳輸和處理。然而,在現實應用中,時鐘信號的波形和電平往往不夠標準,這可能導致系統性能下降或故障。因此,我們需要對這種情況進行適當的處理。

對于波形和電平不標準的時鐘信號,一般應進行以下處理:

1. 時鐘信號濾波

波形和電平不標準的時鐘信號往往會出現抖動或噪聲,這會對數字系統的穩定性和可靠性產生負面影響。因此,我們可以通過濾波的方式對時鐘信號進行處理,減少其噪聲和抖動。濾波的選擇和參數需要根據具體的情況進行確定,常見的濾波方法包括低通濾波、中通濾波和高通濾波等。

2. 時鐘信號重整

在一些情況下,時鐘信號可能會出現頻率偏差或相位偏移,導致信號的時序不準確。這種情況下,我們可以使用時鐘信號重整技術,對時鐘信號進行重新定時,使其滿足系統要求的時序特性。常見的時鐘信號重整技術包括鎖相環(PLL)和延遲鎖定環(DLL)等。

3. 恢復時鐘信號

在某些情況下,時鐘信號可能會被丟失或干擾,這會導致數據傳輸中斷或出錯。因此,我們需要使用恢復時鐘信號的技術,對時鐘信號進行重構,以確保正常的數據傳輸。常見的恢復時鐘信號技術包括自適應等化器和時鐘恢復電路等。

4. 時鐘信號干擾分析與解決

在實際應用中,時鐘信號可能會受到其他信號的干擾,例如電源噪聲、信號泄漏等。這種干擾會導致時鐘信號的波形和電平不規范,進而影響系統的性能。因此,我們需要通過干擾分析和解決技術,對干擾因素進行識別和消除,以確保時鐘信號的正常運行。干擾分析和解決技術包括電磁兼容性設計、屏蔽技術、地線設計等。

5. 時鐘信號優化設計

在數字系統設計過程中,時鐘信號的選擇、布線和優化設計對系統性能至關重要。因此,我們需要進行適當的時鐘信號優化設計,以確保時鐘信號的正確性、穩定性和可靠性。常見的優化設計技術包括時鐘路線設計、時鐘延時優化、時鐘功耗優化等。

綜上所述,對于波形和電平不標準的時鐘信號,我們需要進行多方面的處理和優化設計,以確保系統的穩定性和可靠性。這需要我們掌握一定的電子信號處理和數字系統設計知識,有針對性地進行解決和優化,從而為數字系統應用提供更加優化的時鐘信號。

-

低通濾波器

+關注

關注

15文章

552瀏覽量

48953 -

電源噪聲

+關注

關注

3文章

169瀏覽量

18118 -

時鐘信號

+關注

關注

4文章

503瀏覽量

29874

發布評論請先 登錄

單片機TTL和CMOS電平知識

電能質量在線監測裝置的暫態波形存儲時長一般是多久?

淺談DDR的邏輯電平標準

使用nuclei studio進行調試的一些方法和技巧

光模塊TTL電平是什么?

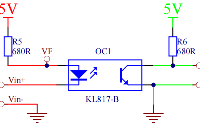

一般光耦的開關電路設計

對于波形和電平不標準的時鐘信號一般應進行怎樣的處理?

對于波形和電平不標準的時鐘信號一般應進行怎樣的處理?

評論