點擊上方藍(lán)字關(guān)注我們

引言

圖像信息的獲取和傳輸是圖像處理系統(tǒng)的重要組成部分,直接影響圖像處理系統(tǒng)的性能。圖像信息的采集包括對圖像數(shù)據(jù)、各種附帶參數(shù)信息以及狀態(tài)控制信號的采集,一般圖像信號和狀態(tài)參數(shù)信號以及控制信號是獨立產(chǎn)生的,因此需要設(shè)計一種系統(tǒng)能夠?qū)⑼獠吭O(shè)備產(chǎn)生的圖像數(shù)據(jù)和狀態(tài)控制信號同步采集,并能長距離高速傳輸,綜合考慮到圖像采集系統(tǒng)所要求的實時性,可靠性,以及FPGA在數(shù)字電路的設(shè)計中的優(yōu)勢,為此本文討論了一種利用FPGA實現(xiàn)基于LVDS的圖像數(shù)據(jù)采集傳輸技術(shù)。

系統(tǒng)設(shè)計

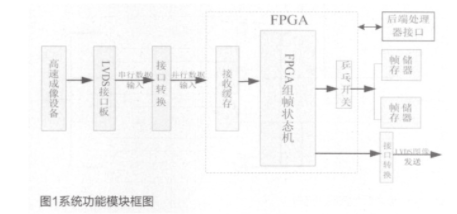

高速圖像數(shù)據(jù)的采集傳輸系統(tǒng)如圖1 所示,主要包括圖像數(shù)據(jù)源的形成、數(shù)據(jù)信息的處理和緩存以及幀數(shù)據(jù)的轉(zhuǎn)發(fā)三部分。其中,圖像數(shù)據(jù)源的形成過程中,成像設(shè)備作為圖像數(shù)據(jù)的來源,它為系統(tǒng)提供高分辨率的可見光和紅外圖像,考慮系統(tǒng)的實時性和高可靠性因素,采用LVDS傳輸接口實現(xiàn)數(shù)據(jù)長距離高速傳輸,解決了傳輸瓶頸問題,圖像數(shù)據(jù)在進(jìn)入FPGA之前需通過數(shù)據(jù)格式轉(zhuǎn)換接口(采用MAX9218實現(xiàn))將串行的數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù)并緩存。

數(shù)據(jù)信息的處理由協(xié)處理器FPGA完成,主要包括圖像數(shù)據(jù)及相關(guān)參數(shù)信息的采集、緩存、組幀和圖像數(shù)據(jù)的轉(zhuǎn)發(fā)。其中圖像數(shù)據(jù)的組幀過程最為復(fù)雜, FPGA根據(jù)圖像源中幀同步、行同步、圖像選擇信號接收解串圖像,存儲至緩存區(qū),并將圖像附帶的參數(shù)信息寫入緩存后部,經(jīng)組幀狀態(tài)機(jī)形成所需的圖像數(shù)據(jù)幀。

圖像數(shù)據(jù)幀形成后,轉(zhuǎn)發(fā)存儲至乒乓結(jié)構(gòu)的幀存儲器,其容量為:512×512×8bit=2Mb。同時硬件邏輯自動將圖像和配套參數(shù)信息數(shù)據(jù)通過LVDS圖像發(fā)送接口發(fā)送至數(shù)據(jù)鏈,圖像數(shù)據(jù)再次以串行的LVDS方式傳輸?shù)胶罄m(xù)設(shè)備進(jìn)行處理。

系統(tǒng)實現(xiàn)

FPGA及外圍硬件電路

在接口轉(zhuǎn)換電路模塊中,圖像數(shù)據(jù)接收端和發(fā)送端均需采用LVDS串行方式進(jìn)行傳輸,所以在接收端將串行輸入的數(shù)據(jù)并行接收進(jìn)FPGA進(jìn)行處理和在發(fā)送端將并行的數(shù)據(jù)串行輸出時,需要進(jìn)行并串和串并轉(zhuǎn)換。

本設(shè)計選用MAXIM公司點對點LVDS串行/解串器芯片MAX9247/MAX9218實現(xiàn)數(shù)據(jù)收發(fā)。

在MAX9218接收端,需要進(jìn)行數(shù)據(jù)格式轉(zhuǎn)換,將串行數(shù)據(jù)源變成并行格式供FPGA處理,同樣在圖像數(shù)據(jù)鏈路終端發(fā)送方MAX9247對輸入的圖像數(shù)據(jù)也有特定的時序要求,涉及到數(shù)據(jù)位和控制位的交替?zhèn)鬏敚枰蒄PGA完成數(shù)據(jù)格式的轉(zhuǎn)換, 并產(chǎn)生相應(yīng)的控制信號DE_IN。

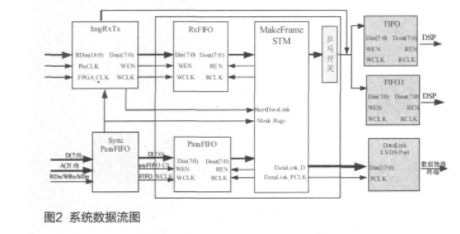

可編程器件FPGA選用Xilinx公司Virtex-4系列XC4VLX25。實現(xiàn)的功能主要是:根據(jù)輸入的行幀同步,采圖像同步和圖像選擇信號來實現(xiàn)圖像數(shù)據(jù)的接收,并緩存到FPGA內(nèi)部的接收RxFIFO中,進(jìn)行幀頭幀尾識別、時序轉(zhuǎn)換,控制信號的生成,并且根據(jù)自定義的通訊協(xié)議,從數(shù)據(jù)流中分解出數(shù)據(jù)幀,同時將原始圖像數(shù)據(jù)和狀態(tài)數(shù)據(jù)打包到同一幀數(shù)據(jù)包中,輸出至數(shù)據(jù)鏈路終端。

圖像數(shù)據(jù)鏈路層

由圖3數(shù)據(jù)的流向來分析,從LVDS接口板輸出的串行圖像數(shù)據(jù)由14個數(shù)據(jù)位(數(shù)字圖像數(shù)據(jù)為D0--D13,低位在前高位在后)、幀同步、行同步、時鐘同步、圖像選擇信號、采圖同步信號組成。圖像數(shù)據(jù)同步時鐘采用7.375MHz,DE_IN由圖像的幀同步信號產(chǎn)生,幀、行同步均為高電平有效,圖像選擇信號用來區(qū)分紅外和可見光圖像,紅外圖像為256×320b,可見光圖像為512×512b,19位圖像數(shù)據(jù)信號經(jīng)過MAX9218解串后的數(shù)據(jù)和控制位接入FPGA。

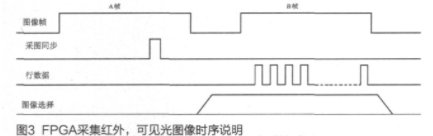

FPGA設(shè)計時,針對紅外和可見光兩種不同類型的圖像數(shù)據(jù)進(jìn)行采集傳輸,設(shè)置一個模式寄存器ModeReg來實現(xiàn)圖像選擇,可以填0或1,用來區(qū)分紅外和可見光,當(dāng)采集可見光時,每輸出一幀有效圖像數(shù)據(jù),需輸出兩個幀信號,第一幀內(nèi)(A幀)只輸出采圖同步信號,不輸出圖像數(shù)據(jù)、行信號等,第二幀(B幀)中不輸出采圖同步信號,只輸出圖像數(shù)據(jù)、行信號等;當(dāng)采集紅外圖像時,只需輸出一幀,圖像選擇信號在第一個幀信號的下降沿跳變,至第二個幀信號下降沿有效,高電平表示紅外圖像,低電平表示可見光圖像。具體時序參考圖3。

經(jīng)過FPGA組幀完成的幀數(shù)據(jù)同時要轉(zhuǎn)發(fā)到終端數(shù)據(jù)鏈路和外部幀存儲器中,供后續(xù)設(shè)備調(diào)用。為了實現(xiàn)后續(xù)設(shè)備提取圖像信息時的實時性,外部存儲模塊采用由乒乓開關(guān)控制的兩個片外幀存儲器,應(yīng)用FPGA實現(xiàn)雙幀存交替切換,將圖像數(shù)據(jù)存儲在兩個獨立的FIFO中,F(xiàn)IFO采用IDT公司的IDT72V2103,此器件快速的存取允許圖像實時存儲轉(zhuǎn)發(fā)。在FPGA的控制下,F(xiàn)IFO空間的一幀數(shù)據(jù)送出后,然后開始將FIFO1 空間的數(shù)據(jù)送出,同時又向FIFO中寫入下一幀數(shù)據(jù),這樣可以保證后續(xù)圖像處理設(shè)備不間斷的提取圖像數(shù)據(jù),以實現(xiàn)快速處理,提高工作效率。

組幀狀態(tài)機(jī)

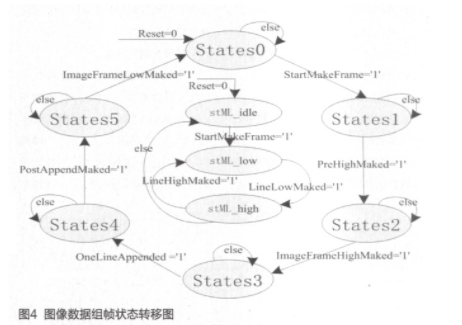

狀態(tài)機(jī)在FPGA內(nèi)部設(shè)計成兩部分,為組幀狀態(tài)機(jī)(外圈)和組行狀態(tài)機(jī)(內(nèi)圈)。其中組幀狀態(tài)機(jī)各狀態(tài)轉(zhuǎn)移順序及條件見圖4,各狀態(tài)占用時間可以通過組行狀態(tài)機(jī)中的行計數(shù)來控制,近而可以完成不同大小規(guī)格的圖像的接收。組幀狀態(tài)機(jī)共有6個狀態(tài)。

state0:空閑狀態(tài)(系統(tǒng)復(fù)位)。state1:幀有效期開始到行有效期開始之間的延時。state2:圖像幀有效期,state3:圖像參數(shù)幀有效期。state4:行有效期結(jié)束到幀有效期結(jié)束之間的延時。state5:幀無效期。Reset為輸入的狀態(tài)機(jī)復(fù)位信號,在系統(tǒng)復(fù)位狀態(tài),如果用來啟動狀態(tài)機(jī)的信號StartMakeFrame = 1,狀態(tài)機(jī)開始工作,進(jìn)入系統(tǒng)下一狀態(tài),組幀狀態(tài)機(jī)在各狀態(tài)轉(zhuǎn)移條件滿足時,依次進(jìn)入下一狀態(tài),否則,保持在原狀態(tài)。

組行狀態(tài)機(jī)共有3個狀態(tài)。

stML_Idle:空閑狀態(tài)。stML_High:行有效期。stML_Low:行無效期。在外圈組幀狀態(tài)機(jī)的每個狀態(tài)中,包含n個組行狀態(tài),所包含的組行狀態(tài)機(jī)中的行數(shù)即組幀狀態(tài)機(jī)各狀態(tài)所占用時間,組行狀態(tài)機(jī)和組幀狀態(tài)機(jī)啟動條件一致,同時啟動。

以采集可見光圖像數(shù)據(jù)為例,上電復(fù)位期間系統(tǒng)處于states0狀態(tài),狀態(tài)機(jī)用外部輸入的7.375MHz時鐘同步整個運行過程,圖像的幀、行、圖像數(shù)據(jù)等信號在同步時鐘的下降沿跳變,上升沿鎖存。一幀圖像數(shù)據(jù)的大小為512×512bit,并將圖像附帶的參數(shù)信息寫入圖像數(shù)據(jù)后一行(即513行),在幀有效期間(states1、 states2、 states3狀態(tài)),CLK 信號作為行計數(shù)器的時鐘,每幀圖像在行有效之前有1行無效圖像信號(states1), 在states2狀態(tài)下,控制采集一幀中的前512行,在states3狀態(tài)下,采集圖象的參數(shù)信息,將圖像數(shù)據(jù)和狀態(tài)參數(shù)組合為統(tǒng)一的數(shù)據(jù)幀,采集完一幀圖像數(shù)據(jù)后等待下一個幀同步信號的到來。在行有效期(stML_High)控制采集一行中的512個像素點數(shù)據(jù),在CLK信號的上升沿進(jìn)行計數(shù), 在數(shù)據(jù)有效期間采集完512個像素點,等待下一個行同步信號的到來,按同樣方式對下一行512像素點數(shù)據(jù)進(jìn)行采集,直至采集完一幀中的512行。

系統(tǒng)仿真

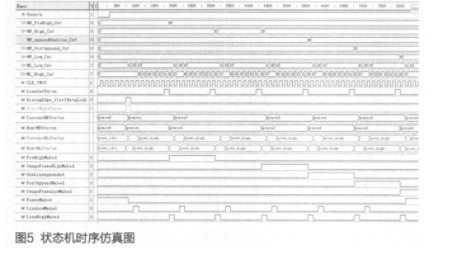

在該系統(tǒng)中,狀態(tài)機(jī)設(shè)計是難點,圖5是運用Active-HDL7.1仿真工具的狀態(tài)機(jī)仿真結(jié)果,仿真時,采用7.375MHz時鐘同步,狀態(tài)機(jī)啟動后,計數(shù)寄存器里的數(shù)據(jù)遞減,進(jìn)而產(chǎn)生各狀態(tài)轉(zhuǎn)移滿足的條件,以此實現(xiàn)狀態(tài)機(jī)的翻轉(zhuǎn)。

在Active-HDL7.1中編寫TestBench文件時,通過向組幀狀態(tài)機(jī)計數(shù)寄存器寫數(shù),來控制各狀態(tài)所占用的時間,利用 StartMakeFrame信號高電平啟動狀態(tài)機(jī),各狀態(tài)發(fā)生翻轉(zhuǎn)時,狀態(tài)完成標(biāo)志就產(chǎn)生產(chǎn)生高電平跳變。

根據(jù)圖5的仿真結(jié)果,可以看出組幀狀態(tài)機(jī)工作正常,所有的邏輯關(guān)系也都驗證無誤。

結(jié)語

本文采用FPGA設(shè)計實現(xiàn)高速圖像采集系統(tǒng),并采用LVDS接口實現(xiàn)接收與發(fā)送,各種模塊之間通過緩存實現(xiàn)通信,避免圖像的丟失;采集的圖像類型和圖像尺寸可以通過軟件重新配置FPGA進(jìn)行調(diào)整。總之,基于FPGA 的高速專用圖像采集系統(tǒng)電路集成度高、信噪比高、功耗低、成本低、速度快以及接口方便,所設(shè)計系統(tǒng)采用兩幀切換存儲方式,使得后續(xù)的其它圖像處理模塊能夠與圖像采集模塊并行工作,為圖像處理器的高度集成化實現(xiàn)提供了可能性。

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標(biāo)題:利用FPGA設(shè)計基于LVDS的圖像數(shù)據(jù)采集傳輸系統(tǒng)

文章出處:【微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

FPGA

+關(guān)注

關(guān)注

1662文章

22480瀏覽量

638472

原文標(biāo)題:利用FPGA設(shè)計基于LVDS的圖像數(shù)據(jù)采集傳輸系統(tǒng)

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于FPGA的DAQ系統(tǒng)|實現(xiàn)高性能數(shù)據(jù)采集的挑戰(zhàn)

工業(yè)視覺時代,圖像采集卡如何重構(gòu)數(shù)據(jù)采集

充電樁數(shù)據(jù)采集設(shè)備有哪些?有什么功能?

PCIe接口-高速模擬采集—高性能-高精度-高品質(zhì)- 青翼凌云軍工級數(shù)據(jù)采集板

圖像采集卡:連接設(shè)備與數(shù)據(jù)的圖像樞紐

單片機(jī)多路數(shù)據(jù)采集系統(tǒng)的設(shè)計

圖像采集卡:機(jī)器視覺時代的圖像數(shù)據(jù)核心樞紐

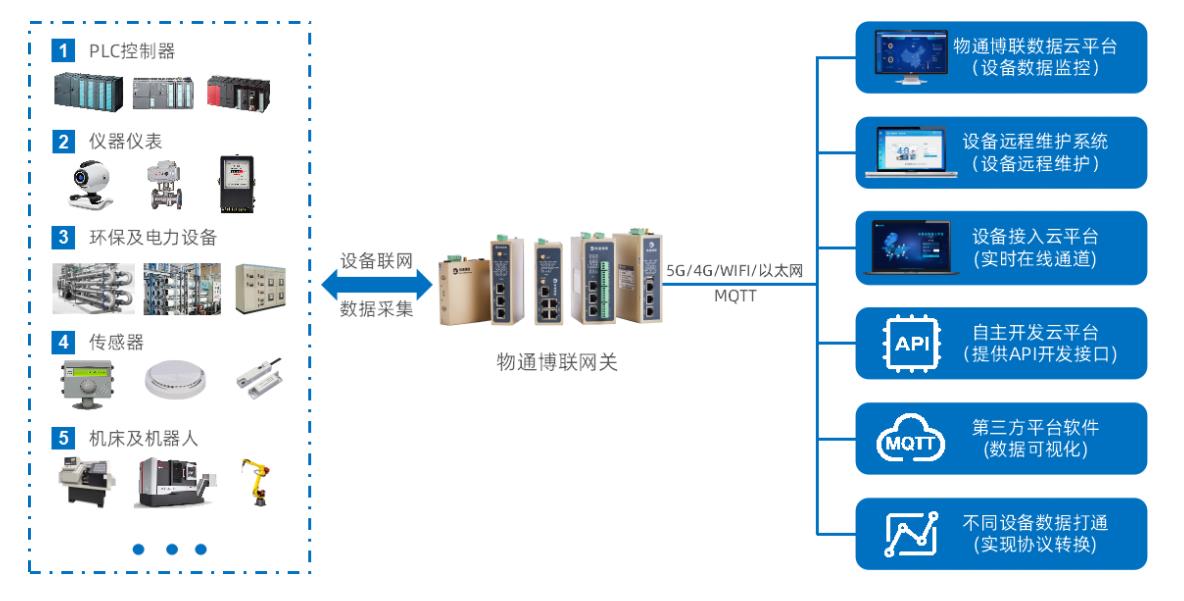

高速分切機(jī)PLC數(shù)據(jù)采集遠(yuǎn)程監(jiān)控系統(tǒng)方案

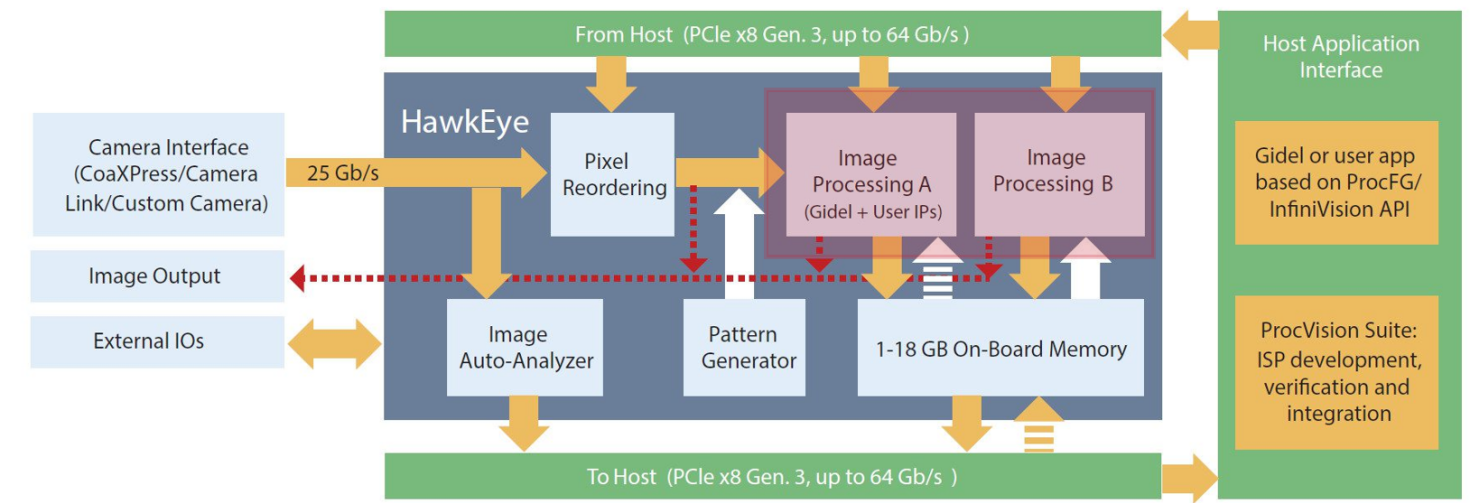

FPGA 加持,友思特圖像采集卡高速預(yù)處理助力視覺系統(tǒng)運行提速增效

利用FPGA設(shè)計基于LVDS的圖像數(shù)據(jù)采集傳輸系統(tǒng)

利用FPGA設(shè)計基于LVDS的圖像數(shù)據(jù)采集傳輸系統(tǒng)

評論