pcb平行走線的影響

隨著電子技術的飛速發(fā)展,PCB(Printed Circuit Board)平行走線引起了越來越多的關注。PCB平行走線是指在電路板上,有兩條或多條電路走線在同一平面上平行布置。

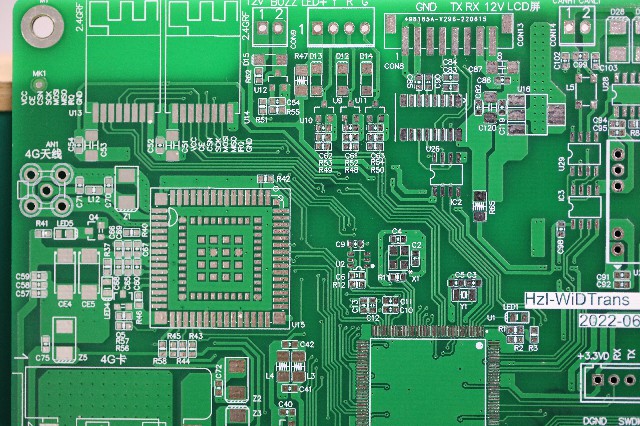

PCB平行走線在電路設計和PCB制造中是相當常見的,不同的電路要求不同的布線方式,有些電路需要平行走線來傳輸信號,而有些需要將走線纏繞在一起以降低電磁輻射的干擾。然而,如果平行走線布置不當,可能會導致電磁干擾噪聲、信號串擾、線路互相干擾等問題,從而影響電路的性能和穩(wěn)定性。

那么,PCB平行走線的影響是什么?

1. 電磁輻射和干擾

當一對平行走線上有電流通過時,它們之間會產(chǎn)生一定的電磁輻射。在高速和高頻信號傳輸時,這種電磁輻射會給其他信號、線路和器件帶來干擾,從而影響電路的性能和穩(wěn)定性。

2. 信號串擾

在兩條相鄰的平行信號線上運行不同信號時,會產(chǎn)生信號串擾現(xiàn)象。這是因為在信號線上的電流會在相鄰的線上感應電壓,從而導致相鄰信號間出現(xiàn)噪聲。特別是在高速傳輸線路中,這種信號串擾會導致誤碼率的增加,降低系統(tǒng)性能。

3. 線路互相干擾

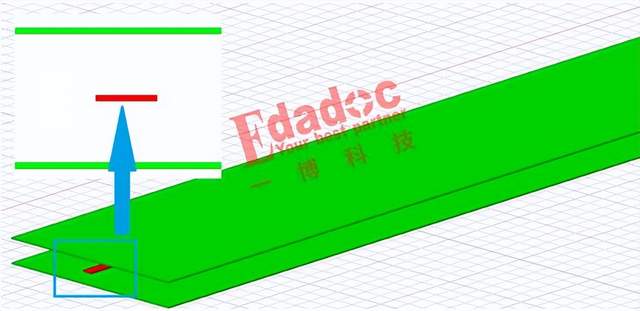

在多層PCB上,平行走線可能會穿過多層,與其他線路相交,從而導致線路互相干擾。這樣的干擾可能會導致電路的不穩(wěn)定性,例如時鐘抖動、時序問題等。

那么如何避免PCB平行走線帶來的影響?

1. 控制走線間距

人們可以通過增加走線之間的距離來減少電磁輻射和干擾。在布局和布線的時候,要避免平行走線之間的距離過近。IPC-2221標準建議最小走線間距為3.175mm,在一些高速傳輸?shù)脑O計中可以適度加大走線間距。

2. 使用差分線路

差分線路是一對平行走線,它們承載同樣的信號,但極性相反。這種設計方式可以減少信號串擾和電磁輻射。差分線路的布線要求嚴格,它需要在走線長度、終端阻抗以及分布電容等方面進行匹配,以保證信號的正確傳輸。

3. 使用屏蔽材料

為了減少電磁輻射和干擾,可以在PCB下面或周圍引入屏蔽材料,如屏蔽墻、屏蔽罩等。這些材料可以將電磁波隔離在PCB外面,減少電磁輻射和干擾。

4. 布局精細,多層分離

在高速設計中,要避免平行走線之間的穿越、相交。可以將同一層的線路拆開,盡量減少線路之間的互相干擾。此外,在多層PCB設計中,通過分層來減少不同層之間的相互影響。

綜上所述,PCB平行走線的影響包括電磁輻射和干擾、信號串擾、線路互相干擾等問題,而避免這些影響的方法通常包括控制走線間距、使用差分線路、使用屏蔽材料、布局精細、多層分離等。在實際的PCB設計中,設計者需要綜合考慮這些影響因素,以確保PCB設計的穩(wěn)定性和最佳性能。

-

電磁干擾

+關注

關注

36文章

2482瀏覽量

107927 -

電磁波

+關注

關注

21文章

1503瀏覽量

55707 -

PCB走線

+關注

關注

4文章

135瀏覽量

14554

發(fā)布評論請先 登錄

班通科技:PCB線寬線距對阻抗的影響有哪些?

BNC PCB線束 | 穩(wěn)定信號傳輸?shù)墓I(yè)連接方案

平行光太陽模擬器測試系統(tǒng)的原理

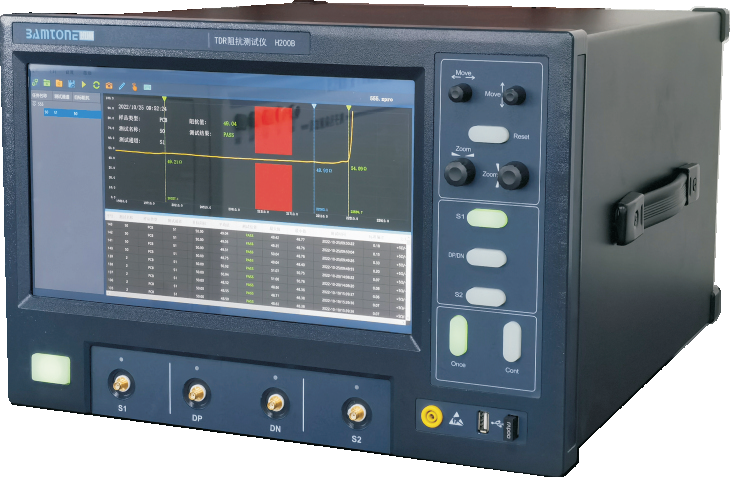

如何用TDR阻抗測量儀快速定位PCB傳輸線故障?

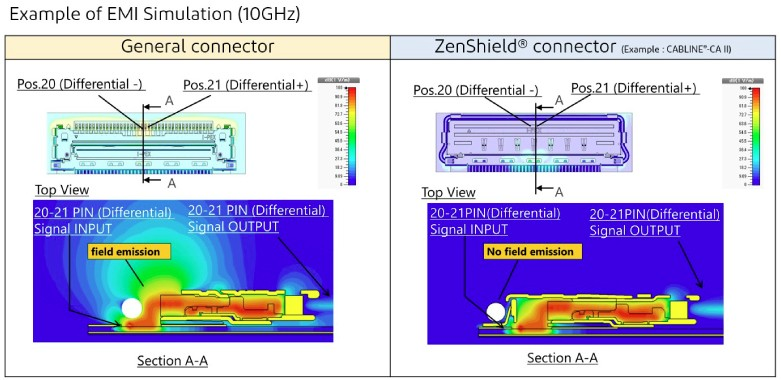

如何管理線束到 PCB 接口的 EMI

allegro軟件走線命令下參數(shù)不顯示如何解決

pcb平行走線的影響

pcb平行走線的影響

評論