SiC FET(即SiC JFET和硅MOSFET的常閉共源共柵組合)等寬帶隙半導(dǎo)體開關(guān)推出后,功率轉(zhuǎn)換產(chǎn)品無疑受益匪淺。此類器件具有超快的開關(guān)速度和較低的傳導(dǎo)損耗,能夠在各類應(yīng)用中提高效率和功率密度。然而,與緩慢的舊技術(shù)相比,高電壓和電流邊緣速率與板寄生電容和電感的相互作用更大,可能產(chǎn)生不必要的感應(yīng)電流和電壓,導(dǎo)致效率降低,組件受到應(yīng)力,影響可靠性。此外,由于現(xiàn)在SiC FET導(dǎo)通電阻通常以毫歐為單位進行測量,因此,PCB跡線電阻可能相當大,須謹慎降低以保持低系統(tǒng)傳導(dǎo)損耗。

設(shè)定電流邊緣速率

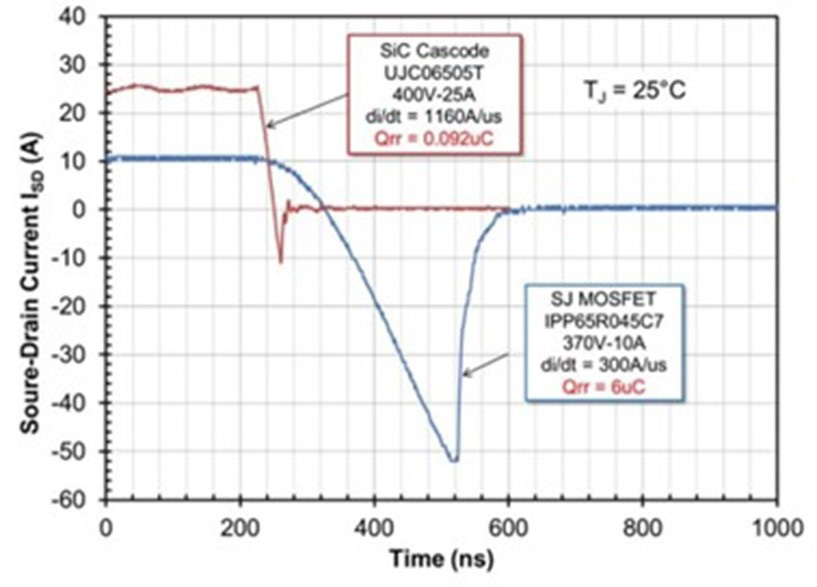

SiC FET可輕松實現(xiàn)超過1000A/μs的電流邊緣速率(圖1),這樣SiC FET、其負載和本地去耦電容之間的開關(guān)回路周圍的電感會產(chǎn)生瞬態(tài)電壓(圖2)。例如,依據(jù)E = -Ldi/dt,100nH回路電感可產(chǎn)生100V的瞬態(tài)電壓,這會導(dǎo)致器件工作電壓提高、擊穿裕量減少且EMI增加。

圖1 :與同等級的Si SJ MOSFET相比,SiC FET開關(guān)波形顯示 >1000A/μs 的邊緣速率

圖1 :與同等級的Si SJ MOSFET相比,SiC FET開關(guān)波形顯示 >1000A/μs 的邊緣速率

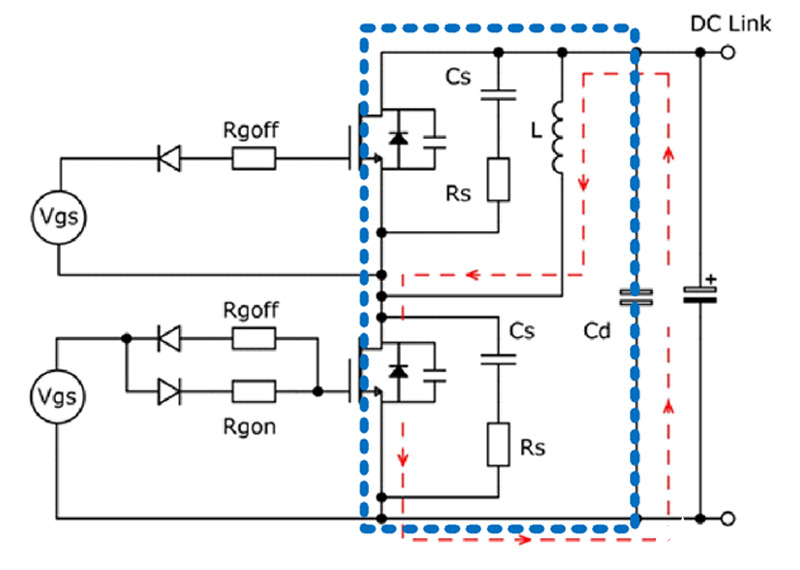

圖2 :具有高di/dt的典型開關(guān)回路

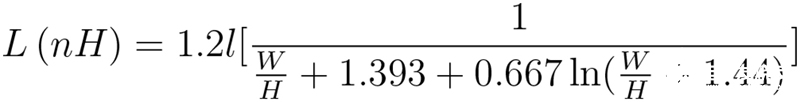

這是真實的電感值,在典型電源應(yīng)用中,考慮到組件的物理尺寸,無法將其緊密封裝在一起。例如,根據(jù)Terman的等式1計算得出,如果寬度(W)為2.5mm且銅重量(T)為2oz (0.07mm),對于每個 “出發(fā)” 和 “返回” 連接,僅50mm (l) 的PCB跡線可產(chǎn)生大約100nH的總電感。

圖2 :具有高di/dt的典型開關(guān)回路

這是真實的電感值,在典型電源應(yīng)用中,考慮到組件的物理尺寸,無法將其緊密封裝在一起。例如,根據(jù)Terman的等式1計算得出,如果寬度(W)為2.5mm且銅重量(T)為2oz (0.07mm),對于每個 “出發(fā)” 和 “返回” 連接,僅50mm (l) 的PCB跡線可產(chǎn)生大約100nH的總電感。

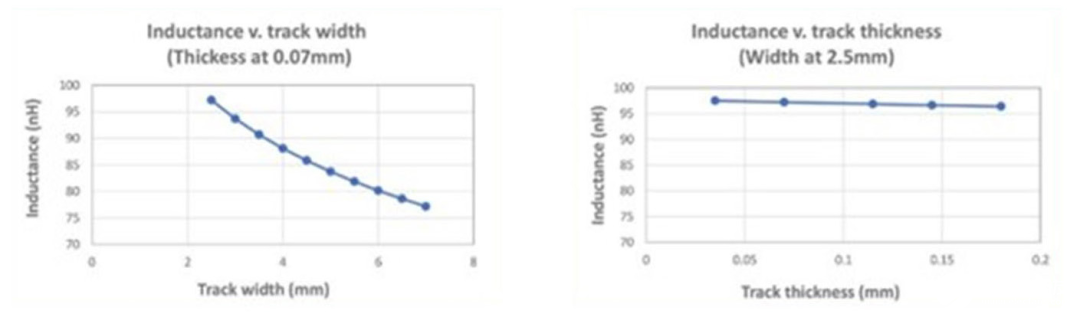

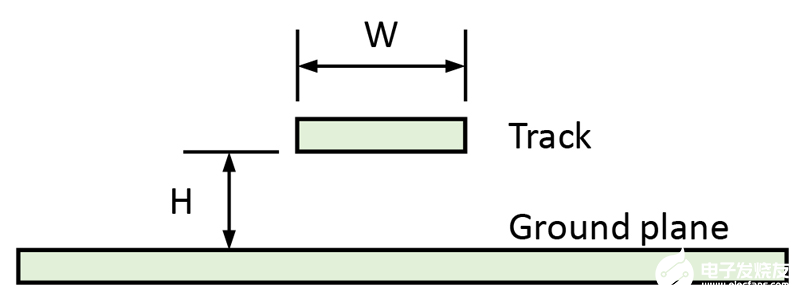

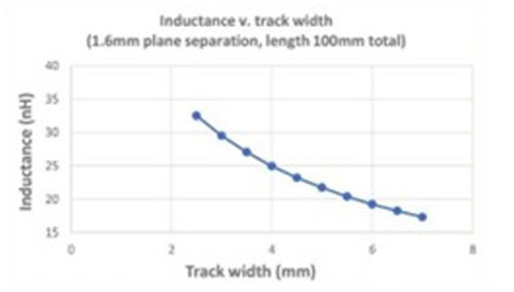

?這個關(guān)系適用于隔離的出發(fā)和返回跡線,不適用于返回平面上方的單條跡線。有趣的是,從圖中可以看出,電感與跡線寬度和厚度的關(guān)系相對較小,長度是主要因素。(圖3)

?這個關(guān)系適用于隔離的出發(fā)和返回跡線,不適用于返回平面上方的單條跡線。有趣的是,從圖中可以看出,電感與跡線寬度和厚度的關(guān)系相對較小,長度是主要因素。(圖3)

圖3 :根據(jù)等式1,隔離的跡線電感隨厚度和寬度的變化

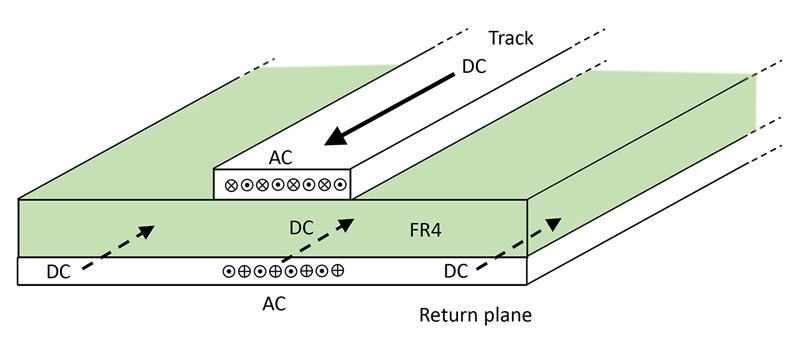

圖表顯示,通過將高頻率去耦電容(圖2中的Cd)放置在比大直流鏈路電容更靠近開關(guān)的位置,可有效縮短長度并獲得最大優(yōu)勢,電容不是低電感類型時候效果更為明顯。如果出發(fā)和返回路徑十分接近,通常使用銅平面, 則電感大幅減少(圖4)。

圖3 :根據(jù)等式1,隔離的跡線電感隨厚度和寬度的變化

圖表顯示,通過將高頻率去耦電容(圖2中的Cd)放置在比大直流鏈路電容更靠近開關(guān)的位置,可有效縮短長度并獲得最大優(yōu)勢,電容不是低電感類型時候效果更為明顯。如果出發(fā)和返回路徑十分接近,通常使用銅平面, 則電感大幅減少(圖4)。 圖4 :返回平面在跡線下方可顯著減少總電感

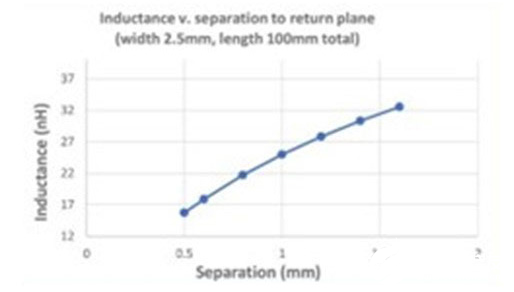

根據(jù)Clayton的等式2,現(xiàn)在,與返回平面相距1.6mm(H)的2.5mm(W) 跡線的總回路電感僅為32nH。該等式對W/H>1有效,同樣,跡線厚度不是主要因素,但現(xiàn)在,跡線寬度以及跡線與平面之間的距離可產(chǎn)生顯著影響(圖5)。如果返回平面同時位于跡線上方和下方,則電感進一步減少,并獲得增強屏蔽的額外優(yōu)勢。

圖4 :返回平面在跡線下方可顯著減少總電感

根據(jù)Clayton的等式2,現(xiàn)在,與返回平面相距1.6mm(H)的2.5mm(W) 跡線的總回路電感僅為32nH。該等式對W/H>1有效,同樣,跡線厚度不是主要因素,但現(xiàn)在,跡線寬度以及跡線與平面之間的距離可產(chǎn)生顯著影響(圖5)。如果返回平面同時位于跡線上方和下方,則電感進一步減少,并獲得增強屏蔽的額外優(yōu)勢。

柵極和源連接中的公共連接電感是一大問題

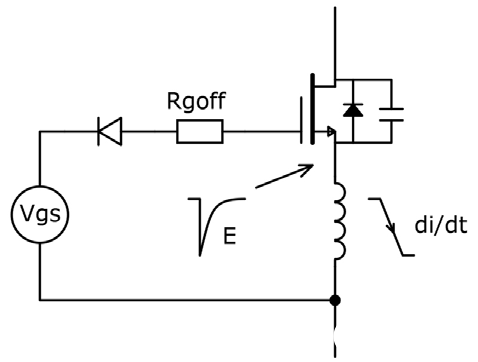

如果 SiC FET 柵極驅(qū)動回路及其源極電流共用任一長度的跡線,則公共連接的電感會產(chǎn)生瞬態(tài)電壓,其中負載電流階躍作用于柵極驅(qū)動(圖6)。最糟糕的情況是,關(guān)斷驅(qū)動信號的幅度減小,這可能會導(dǎo)致 “幻象導(dǎo)通”,在橋式轉(zhuǎn)換器支路中產(chǎn)生 “擊穿”,帶來災(zāi)難性損壞。即使分離的柵極驅(qū)動回路連接至三引腳TO-247器件的源極,仍有大約10nH的封裝電感,這是常見現(xiàn)象,無法消除,如果源極電流邊緣速率為1000A/μs,會產(chǎn)生10伏的瞬態(tài)電壓。在實際設(shè)計中,這些邊緣速率通常較為緩慢,解決方案之一是使用四引腳器件,并與源極建立單獨的內(nèi)部 “開爾文” 連接,比如UnitedSiC (Qorvo)提供的器件。這能夠?qū)⒐策B接電感降至大約1nH的裸片數(shù)據(jù),從而實現(xiàn)更高的邊緣速率以及可能更低的動態(tài)損耗。

圖6 :高源極 di/dt 和公共連接電感會產(chǎn)生瞬態(tài)柵極電壓

圖6 :高源極 di/dt 和公共連接電感會產(chǎn)生瞬態(tài)柵極電壓電路電容可導(dǎo)致不必要的耦合

請注意,較寬的跡線可有效降低電感和瞬態(tài)電壓,但也會提高對相鄰跡線、組件和地面的電容。SiC FET所具備的高dV/dt 速率能夠引起位移電流,這會導(dǎo)致高EMI水平和混亂操作。例如,邊緣速率為100kV/μs 時,SiC FET可輕松開關(guān),僅通過10pF就能產(chǎn)生1A。電流以通常難以識別的路線圍繞系統(tǒng)流動。在高側(cè)開關(guān)的源連接處,對主開關(guān)節(jié)點的電容是一個特殊問題。主開關(guān)節(jié)點可通過物理方式隔離,以避免耦合至任何敏感的控制或反饋連接。然而,始終有路徑通過柵極驅(qū)動器連接至系統(tǒng)其余部分,即使利用磁力或通過光耦合器將其隔離,信號路徑和提供柵極驅(qū)動電源的DC-DC轉(zhuǎn)換器中也將存在殘余電容。為此,在指定具有低耦合電容的隔離部件時,應(yīng)格外小心,最好不超過數(shù)pF。 開關(guān)節(jié)點和機箱接地之間的電容是共模EMI的主要來源,可能會導(dǎo)致超出法定限制。好在SiC FET等器件的效率往往意味著它們能夠使用小型未接地散熱器操作。如果必須使用較大的接地散熱器,開關(guān)器件和散熱器之間可使用銅箔形式的靜電屏蔽,但這勢必會提高熱阻,因此必須小心地對其進行絕緣處理,以滿足安全標準。

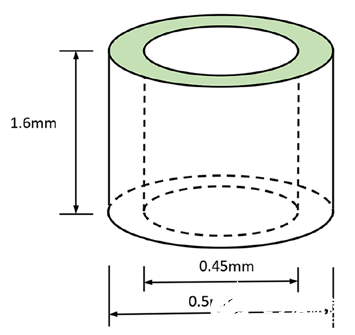

散熱考慮因素 SiC FET的損耗通常非常低,因此PCB跡線和平面可作為散熱器,將結(jié)溫保持在合理的范圍內(nèi)。由于與其他發(fā)熱組件的相互作用,此類布局的熱阻可能很難量化,因此通常使用多物理模擬軟件來預(yù)測結(jié)果。PCB材料、層數(shù)及其銅重量、氣流方向和速率、表面輻射系數(shù)和其他組件產(chǎn)生的交叉加熱都必須考慮在內(nèi)。 熱量可使用散熱孔通過PCB傳遞,憑借僅大約0.25W/m-K的核心熱導(dǎo)率,對FR4進行改進。直徑為0.5mm、長1.6mm且壁厚為0.025mm的未填補散熱孔的熱阻約為100°C/W(圖7)。

PCB跡線電阻導(dǎo)致效率降低

現(xiàn)在,即使在高額定電壓下,SiC FET的導(dǎo)通電阻只有數(shù)毫歐,因此其傳導(dǎo)損耗可能非常低。然而,相關(guān)跡線電阻可能相當大,因此應(yīng)盡可能減少跡線電阻,以維持SiC FET優(yōu)勢。為了評估影響,PCB電阻取決于銅電阻率、厚度、溫度和跡線長度。一種便捷的測量方式是沿著跡線計算 “平方” 的數(shù)量,例如,在25°C時,無論尺寸如何,35μm/1oz銅在每 “平方” 的電阻為0.5毫歐,所以1mm寬、 1mm長的跡線和10密耳寬、10密耳長的跡線一樣,電阻均為0.5毫歐。因此,正如我們在計算電感時使用的,對于長度只有 100mm的2.5mm跡線,測量得出其電阻為20毫歐——通常比最低的SiC FET導(dǎo)通電阻還要多。此外,隨著溫度升高,銅電阻增加,在本例中,100°C時,銅電阻增加至大約26毫歐,因此應(yīng)將這一因素考慮在內(nèi)。對于直跡線,“計算平方數(shù)” 的方法十分準確,如有突然轉(zhuǎn)彎,由于電流集聚效應(yīng),拐角處的電阻率會提高。無論如何,應(yīng)避免直角,以防止出現(xiàn)局部高電場強度,避免電壓擊穿風險增加。 對于交流電,應(yīng)考慮 “趨膚效應(yīng)”,即隨著頻率增加,電流往往集中到表面流動,而不是在大部分導(dǎo)線內(nèi)流動。但對于PCB跡線,該效應(yīng)通常較小,趨膚深度約為66/f1/2mm,因此,即使在1MHz時,開關(guān)電流流向深度為0.07mm或總厚度為2oz的銅。諧波電流不會滲透得這么深,但其幅度更小。 當高頻率交流電通過銅平面返回時,可以假設(shè)該路徑上的電阻更低。然而,由于電流集中到功率跡線下方且只有直流組件顯著分散,優(yōu)勢并不明顯(圖8)。

結(jié)論

應(yīng)了解并降低實際連接電阻,以便充分發(fā)揮SiC FET的潛在性能。在一些轉(zhuǎn)換拓撲結(jié)構(gòu)中,寄生電感和電容可能是諧振槽的一部分,因此通常也應(yīng)該降低。在這種情況下,量化和控制電路值仍非常重要。

原文標題:給SiC FET設(shè)計PCB有哪些注意事項?

文章出處:【微信公眾號:Qorvo半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

Qorvo

+關(guān)注

關(guān)注

17文章

729瀏覽量

80569

原文標題:給SiC FET設(shè)計PCB有哪些注意事項?

文章出處:【微信號:Qorvo_Inc,微信公眾號:Qorvo半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

三防漆怎么使用?有什么注意事項?

梳理三防漆從前期準備到最終固化的操作流程,幫助您掌握三防漆的使用方法。三防漆怎么使用?有什么注意事項?一、施工前的預(yù)處理在使用三防漆前,充分的準備是成功施工的基礎(chǔ),

驅(qū)動板PCB布線的注意事項

PCB Layout 注意事項

1)布局注意事項:

●● 整體布局遵循功率回路與小信號控制回路分開布局原則,功率部分和控制部分的 GND 分開回流到輸入

GND。

●● 芯片的放置方向優(yōu)先考慮驅(qū)動

發(fā)表于 12-02 07:40

CW32R031射頻板LAYOUT注意事項有哪些?

CW32R031射頻板LAYOUT注意事項有哪些?目前433MHz發(fā)射時單片機偶爾死機,天線距離MCU只有2cm,需要做特別隔離嗎?

發(fā)表于 11-19 08:09

L083最低功耗是多少,應(yīng)該如何進行低功耗設(shè)計?有哪些注意事項?

L083最低功耗是多少,應(yīng)該如何進行低功耗設(shè)計?有哪些注意事項?

發(fā)表于 11-12 07:29

PCB扇孔設(shè)計必知:原則與注意事項,讓設(shè)計更高效!

一站式PCBA加工廠家今天為大家講講PCB扇孔的作用及優(yōu)點有哪些?PCB扇孔設(shè)計的原則及注意事項。在PCB設(shè)計中,扇孔設(shè)計是一項重要技術(shù),常

SiC MOSFET并聯(lián)運行實現(xiàn)靜態(tài)均流的基本要求和注意事項

通過并聯(lián)SiC MOSFET功率器件,可以獲得更高輸出電流,滿足更大功率系統(tǒng)的要求。本章節(jié)主要介紹了SiC MOSFET并聯(lián)運行實現(xiàn)靜態(tài)均流的基本要求和注意事項。

設(shè)置射頻網(wǎng)絡(luò)分析儀的測試條件有哪些注意事項

射頻網(wǎng)絡(luò)分析儀(VNA)的測試條件設(shè)置直接影響測量結(jié)果的準確性和可靠性。以下從儀器配置、被測器件(DUT)特性、環(huán)境干擾、校準與驗證四個維度,系統(tǒng)梳理關(guān)鍵注意事項及解決方案。一、儀器配置與參數(shù)設(shè)置

發(fā)表于 05-06 16:02

SiC MOSFET驅(qū)動電路設(shè)計注意事項

柵極驅(qū)動器是保證SiC MOSFET安全運行的關(guān)鍵,設(shè)計柵極驅(qū)動電路的關(guān)鍵點包括柵極電阻、柵極電壓和布線方式等,本章節(jié)帶你了解SiC MOSFET驅(qū)動電路設(shè)計、驅(qū)動電阻選擇、死區(qū)時間等注意事項。

錐齒輪減速機的使用安裝和維護維修注意事項

錐齒輪減速機的使用、安裝和維護維修注意事項涵蓋了多個方面,以下是對這些注意事項的詳細歸納: 一、使用注意事項 1. 確認規(guī)格與設(shè)計相符:在使用減速機前,請先行確認購買的規(guī)格與設(shè)計規(guī)格是否相符。 2.

直流有刷電機驅(qū)動PCB設(shè)計注意事項講解(可下載)

一、 項目名稱:《直流電機驅(qū)動器設(shè)計》二、 直流有刷電機驅(qū)動 PCB 設(shè)計注意事項講解大家好,經(jīng)過前面文章的分享,原理圖我們已經(jīng)全部設(shè)計完畢了,接下來需 要繪制 PCB 了在繪制

發(fā)表于 03-11 14:43

?1次下載

給SiC FET設(shè)計PCB有哪些注意事項?

給SiC FET設(shè)計PCB有哪些注意事項?

評論