1.為什么需要debug時鐘頻率

在芯片設計中,為了便于定位故障,有時候需要確認部分時鐘頻率是否正確,需要部分debug手段。常見的方式是:將時鐘信號引到芯片管腳,通過儀器測量。這類方式必須要測量儀器,并且需要熟練使用,耗時較長。還有一種簡單的方式,通過時鐘計數的方式判斷時鐘頻率是否正確。

2.Debug時鐘頻率原理

本文以serdes用戶側并行接口的恢復時鐘為例,說明一下如何判斷serdes恢復時鐘頻率是否正常。

本文以host_clk(100MHz)時鐘為基準時鐘,進行判斷。host_clk為100MHz,以serdes_clk為830.078125MHz進行分析

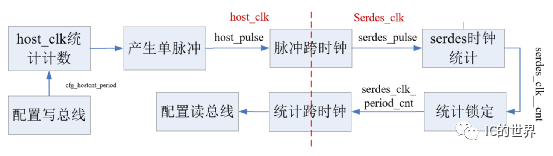

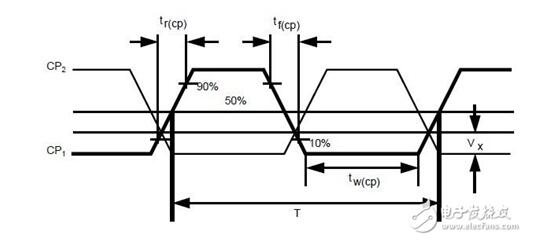

配置cfg_host_cnt_period為10000(10進制),則在10000個host_clk周期里,serdes_clk應該跳變了8300781次。首先在host_clk時鐘域下,存在遞增循環計數host_clk_cnt,host_clk_cnt在0~cfg_hostcnt_period-1范圍內遞增,不斷循環。在serdes_clk時鐘域下,存在計數serdes_clk_cnt,serdes_clk_cnt不斷遞增,直到存在有效脈沖serdes_pulse則清零。

每次host_clk_cnt計數到cfg_hostcnt_period-1,則產生一個有效脈沖host_pulse。host_pulse通過脈沖跨時鐘模塊輸出serdes_pulse。serdes_pulse下一個周期將serdes_clk_cnt清零,并且將serdes_clk_cnt當前值鎖存到serdes_clk_period_cnt,serdes_clk_period_cnt通過跨時鐘模塊同步到host_clk時鐘域并且送到host_clk下的配置讀總線(配置讀寫總線通常是一個模塊)。

此方法的精度雖然有限,但是卻能很方便地判斷時鐘頻率是否穩定,能夠判斷目標時鐘頻率范圍。

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

9520瀏覽量

157021 -

時鐘頻率

+關注

關注

0文章

73瀏覽量

21093 -

時鐘信號

+關注

關注

4文章

504瀏覽量

29967 -

DEBUG

+關注

關注

3文章

95瀏覽量

21379

原文標題:verilog 定位:debug時鐘頻率

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

時鐘和debug配置

分析引起較高時鐘頻率仿真失敗的原因

基于SERDES時鐘的頻率跟隨的設計

什么是時鐘頻率_時鐘頻率詳解和編程

cpu時鐘頻率計算公式_CPU頻率計算方法詳解

cpu時鐘頻率的單位是什么

如何修改時鐘頻率

關于外部時鐘晶振頻率選擇

51/時鐘周期、時鐘頻率、狀態周期、機器周期

為什么需要debug時鐘頻率 Debug時鐘頻率原理詳解

為什么需要debug時鐘頻率 Debug時鐘頻率原理詳解

評論