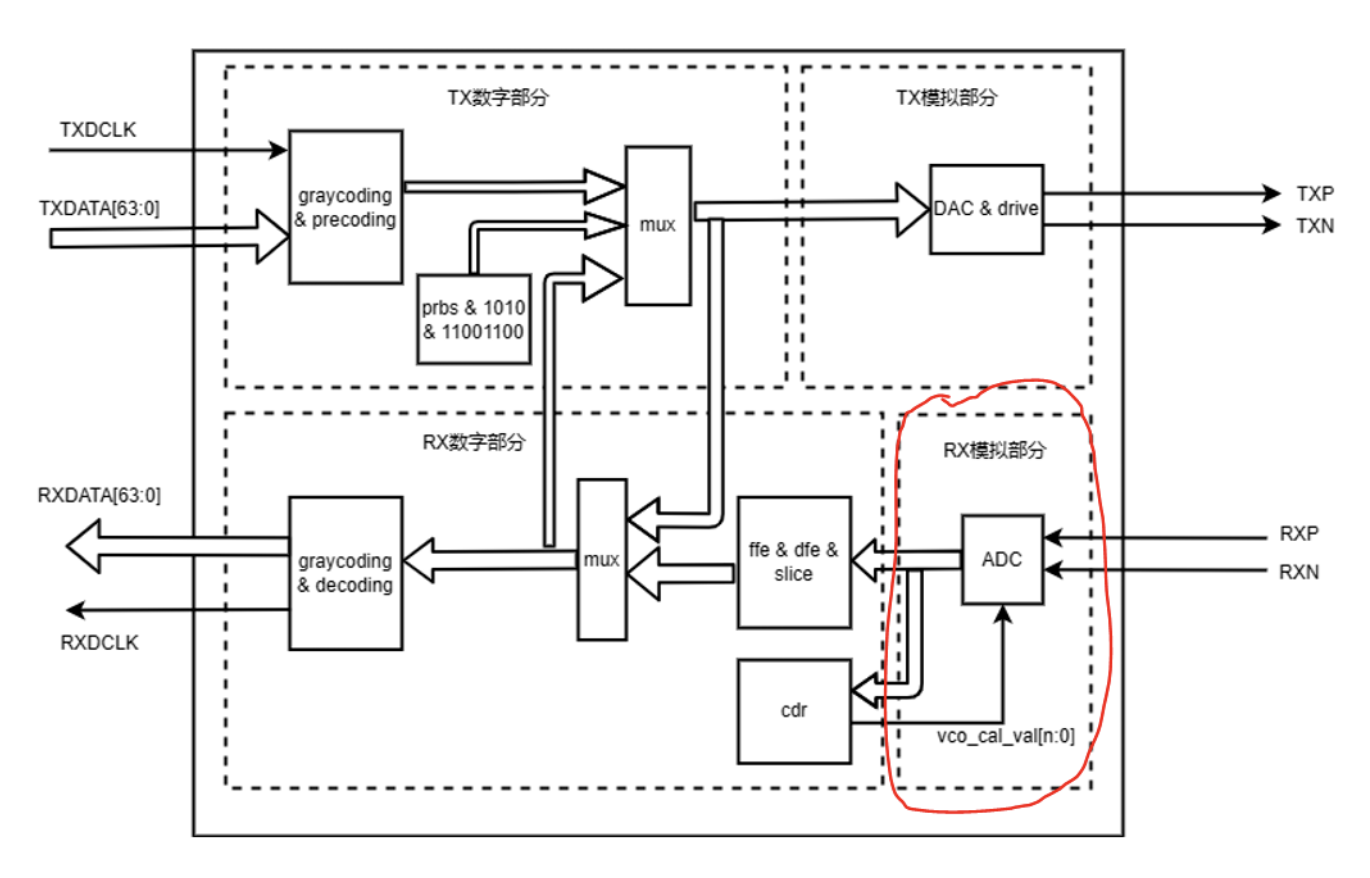

對于圖1所示TX/RX模擬部分的實現方式,大家是不是一直有這樣的疑問: Serdes在將并行data通過DAC串行發出去的時候,或者在接收端通過ADC進行串行data采樣的時候,是怎么實現的?比如56G的serdes就是用56G的ADC和DAC嗎?

答案是肯定不是,沒有那么高頻的ADC和DAC,通常ADC和DAC最大可以工作在1G頻率左右,再大的頻率無法實現精度的。所以采用多個ADC/DAC分時工作的模式。

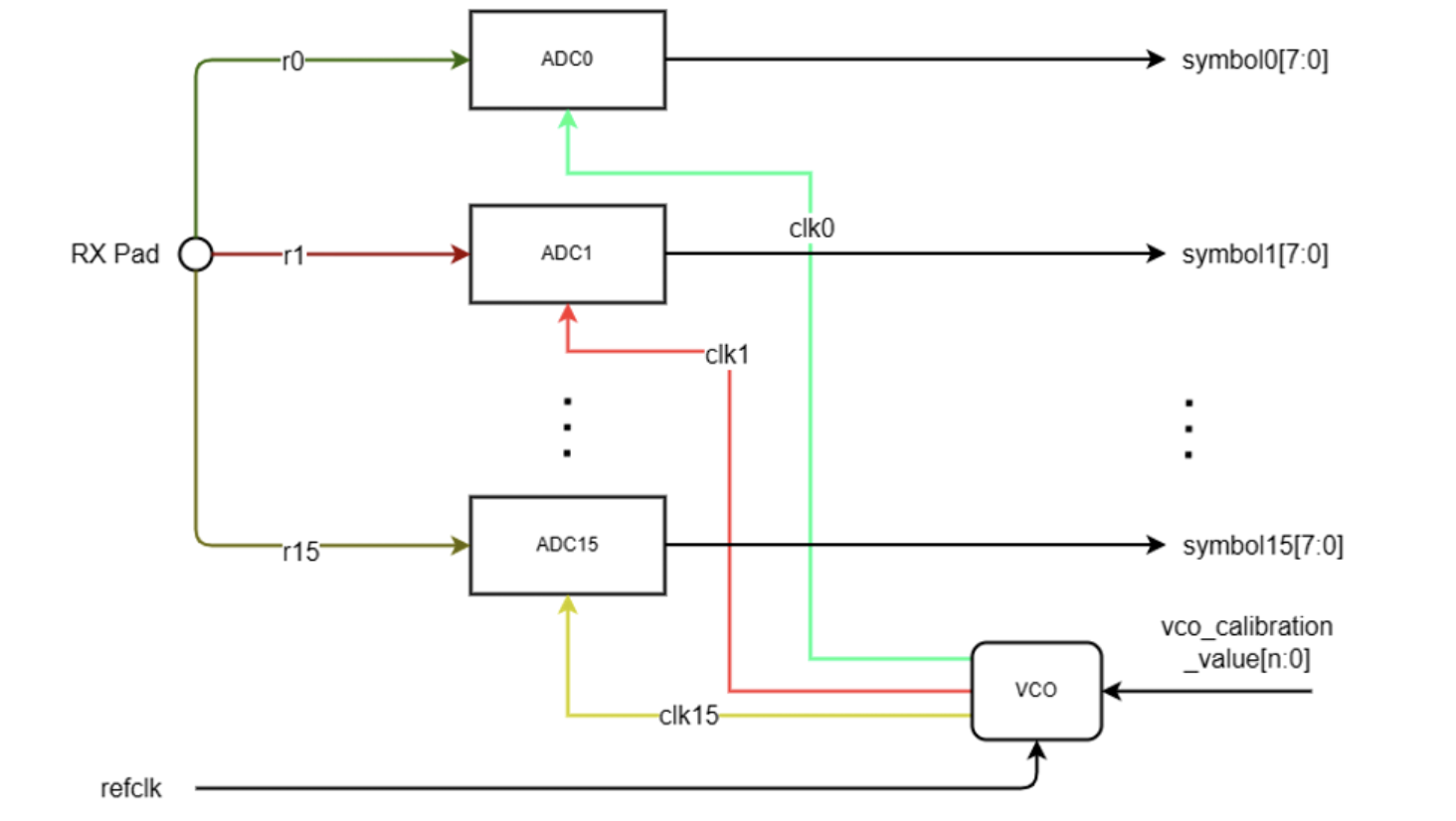

RX接收端采樣方式如下圖2,RX Pad連接到16個ADC上,后端要嚴格約束Pad到不同ADC之間的走線一樣長,可以通過繞線方式實現。

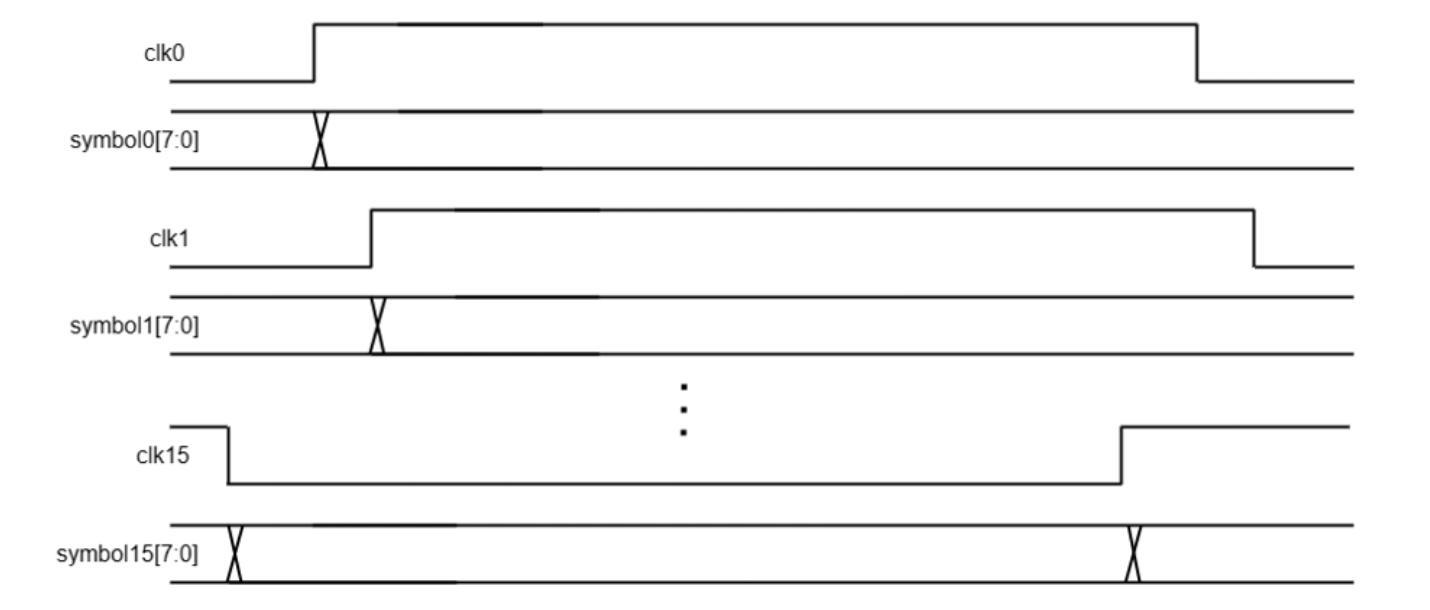

CDR的數字邏輯輸出vco_calibration_value[n:0]到模擬VCO實現相位調整。VCO輸出多路時鐘到多個ADC,如圖3所示,比如通過16個ADC分時采樣,VCO輸出的相鄰時鐘差90°/16。

ADC在時鐘上升沿進行采樣,然后模擬通過clk15將16個采樣symbol[7:0] pipe到數字邏輯,然后進行均衡判決。TX端的DAC發送端是相同的方式進行的。

圖1:serdes架構框圖

圖2:RX ADC采樣框圖

圖3:RX ADC采樣時鐘圖示

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

接收機

+關注

關注

9文章

1247瀏覽量

56357 -

adc

+關注

關注

100文章

7623瀏覽量

556552 -

時鐘信號

+關注

關注

4文章

508瀏覽量

30045 -

ADC采樣

+關注

關注

0文章

134瀏覽量

13601 -

VCO設計

+關注

關注

0文章

2瀏覽量

3594 -

SERDES接口

+關注

關注

0文章

28瀏覽量

3371

發布評論請先 登錄

相關推薦

熱點推薦

從SerDes到SoC,全場景適配的FCom差分晶振設計全解

芯片匹配方案

在差分晶體振蕩器的系統設計中,確保時鐘信號與接收芯片的電氣特性完美匹配,是保證整體時序穩定與抖動抑制的關鍵。FCom在長期產品應用過程中,歸納出覆蓋SerDes、高速ADC/DA

發表于 05-30 11:53

SERDES接口電路設計

通信,該SERDES接口方案具有成本低、靈活性高、研發周期短等特點。 1 硬件接口: 硬件的接口如上圖所示,主要包括發送與接收模塊。 發送模塊包括8b/10b編碼器,并串轉換器

發表于 05-29 17:52

FPGA SERDES接口電路怎么實現?

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES

發表于 10-23 07:16

SERDES傳輸和引腳關聯

親愛的Xilinx論壇,我正在實現基于SERDES協議的序列化傳輸。我需要在Kintex7上接收8個差分對,這些差分對承載由另一個Kintex7串行化的64位字,主時鐘為100MHz。

發表于 03-17 09:53

SerDes是怎么工作的

FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是標配了。從PCI到PCI Express, 從ATA到SATA,從并行ADC接口到JESD204, 從RIO

發表于 07-28 07:02

基于SERDES時鐘的頻率跟隨的設計

在很多無線或者有線的系統應用中,都需要器件的接收端能夠和鏈路的發送端的頻率做跟隨。通常的實現方案都是通過將SERDES的恢復時鐘引到芯片外部,然后通過一個cleanup PLL過濾抖動

發表于 11-18 12:08

?8206次閱讀

如何使用FPGA實現SERDES協議

速度的并行總線傳輸串行化的數據。一個實例是用單個PCI-Express 通道,替代傳統的32 位、64MHz PCI 總線(可達到2.112Gb/s) ,僅用4 條線(運行在2.5GHz) ,可達到4Gb/s總數據率。簡言之, SERD

發表于 10-09 17:25

?20次下載

單通道56G的SERDES,參考時鐘如何選取?

為滿足目前的56GPAM-4 SerDes技術,以支持更高帶寬的100G+以太網和光網絡設計。硬件開發人員通常需要100fs(典型值)以下RMS相位抖動規范的時鐘。這些設計通常需要與CPU和系統時鐘等其他頻率時鐘混用。

SERDES的優勢 SERDES演變的看法

,另一個優勢是能夠通過一對差分對信號引腳(而不是8、16、32或N個數據引腳和一個時鐘引腳)發送數據。在串行傳輸這個方面得益于更小的數據包和更密集的pcb而節省了成本。具體取決于晶片成本、封裝成本、PCB成本和PCB擁塞等因素。 距離優勢 在過去的十年里,

serdes串行發送和接收是怎么實現的?serdes就是用56G的ADC和DAC嗎?

serdes串行發送和接收是怎么實現的?serdes就是用56G的ADC和DAC嗎?

評論