pcb設(shè)計常見問題和改善措施

隨著現(xiàn)代電子技術(shù)的不斷發(fā)展,硬件設(shè)計的要求也越來越高。作為硬件設(shè)計的基礎(chǔ),PCB設(shè)計在整個電子產(chǎn)品的生產(chǎn)過程中占據(jù)著至關(guān)重要的地位。然而,在實際的PCB設(shè)計過程中,由于各種原因,往往會出現(xiàn)一些常見問題。本文將詳細(xì)介紹PCB設(shè)計中常見問題以及可能的改善措施。

一、符號庫不統(tǒng)一

在PCB設(shè)計的初期,通常需要進(jìn)行原理圖設(shè)計,而符號庫是原理圖設(shè)計的基礎(chǔ)。常見的符號庫不統(tǒng)一問題,指的是在一個項目中,使用了不同的符號庫,這將會給后期的工程帶來很多麻煩。

解決方法:

1.建立公司內(nèi)部統(tǒng)一的符號庫,方便在不同項目中共用。

2.在PCB設(shè)計的初期,對每個符號庫進(jìn)行校驗,避免不同符號庫之間的沖突。

二、走線費(fèi)用高

在PCB設(shè)計中,電路的復(fù)雜性會影響到電路布局和走線。如果走線不合理,可能會導(dǎo)致走線費(fèi)用高,影響電路的可靠性和穩(wěn)定性。

解決方法:

1.在電路布局時,應(yīng)優(yōu)先考慮電路結(jié)構(gòu)的簡單性和可靠性,盡可能減少走線數(shù)量,降低走線費(fèi)用。

2.對于需要用到大量走線的電路,考慮采用多層印制板的設(shè)計方式,這樣可以通過布線的方式降低走線費(fèi)用。

三、電源噪聲干擾

在PCB設(shè)計中,電源噪聲干擾是常見問題。這種噪聲干擾可能會對電路的穩(wěn)定性和可靠性造成不良影響,甚至?xí)?dǎo)致電路的失效。

解決方法:

1.在PCB設(shè)計時,應(yīng)盡可能避免電源線與信號線的交叉,以減少電源噪聲干擾。

2.對于需要保證電路穩(wěn)定性和可靠性的應(yīng)用,可以采用多個電源濾波器,降低電源噪聲干擾。

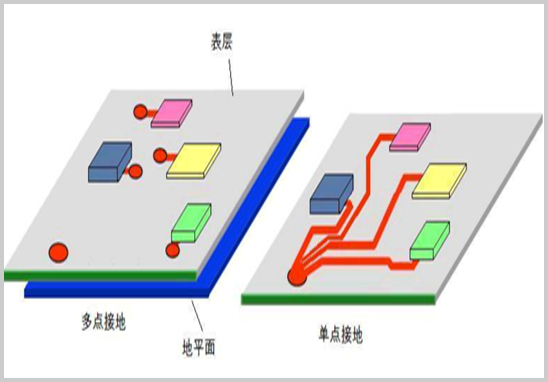

四、電磁兼容問題

電磁兼容問題在PCB設(shè)計中也是一個常見的問題。電磁干擾可能會導(dǎo)致噪聲干擾、信號的截斷、通信的失效等問題。

解決方法:

1.在PCB設(shè)計時,應(yīng)使用正確的電磁屏蔽材料和方法,以減少電磁干擾。

2.通過合適的電磁兼容測試,判斷電路是否符合相關(guān)的電磁兼容標(biāo)準(zhǔn)。

五、分立器件與集成器件混用

在PCB設(shè)計中,一些設(shè)計師會將分立器件和集成器件混用,這可能會導(dǎo)致電路的復(fù)雜性增加,而且還可能會導(dǎo)致電路的靈敏性和可靠性降低。

解決方法:

1.設(shè)計師應(yīng)盡可能使用集成器件,這樣可以降低電路的復(fù)雜性和可靠性問題。

2.使用分立器件時,應(yīng)注意其電流、電壓等參數(shù)的匹配,以充分保障電路的穩(wěn)定性和可靠性。

六、封裝與布局不匹配

PCB設(shè)計中,封裝與布局不匹配是一個常見的問題。這可能會導(dǎo)致電路的異常或修改不便等問題。

解決方法:

1.設(shè)計師應(yīng)對封裝進(jìn)行校驗和建立工具庫,以保證封裝與布局的匹配。

2.在PCB設(shè)計之前,應(yīng)對封裝進(jìn)行認(rèn)真的檢查和轉(zhuǎn)換,保證其正確性和一致性。

七、壘層規(guī)劃不合理

在多層PCB設(shè)計中,壘層規(guī)劃不合理會導(dǎo)致電路寄生電容和電磁干擾等問題,從而影響電路的穩(wěn)定性和可靠性。

解決方法:

1.在多層PCB設(shè)計中,壘層規(guī)劃應(yīng)從電磁兼容性、信號完整性、電源序列性等方面進(jìn)行全面考慮。

2.設(shè)計師應(yīng)盡可能避免層間跨越、信號走線何層與電源走線何層、壘層順序等問題,保證壘層規(guī)劃的合理性。

八、未考慮高速信號的影響

在高速信號的傳輸中,電路板上的微小變化和電容差異可能會導(dǎo)致極其顯著的神奇信號失真。

解決方法:

1.要避免不必要的線長和布線拐角,減少導(dǎo)致信號失真的電磁干擾。

2.盡可能地使用微帶和同軸布線,以減少信號失真。

綜上所述,PCB設(shè)計中,常見問題包括符號庫不統(tǒng)一、走線費(fèi)用高、電源噪聲干擾、電磁兼容問題、分立器件與集成器件混用、封裝與布局不匹配、壘層規(guī)劃不合理、未考慮高速信號的影響等。在解決這些問題時,應(yīng)從不同的方面進(jìn)行考慮,比如符號庫的統(tǒng)一、電路布局的簡單性和可靠性、電路的穩(wěn)定性和可靠性等。只有采取科學(xué)的解決方法,PCB設(shè)計的質(zhì)量才能得到有效的保障,從而讓電子產(chǎn)品更加穩(wěn)定和可靠。

-

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4927瀏覽量

95575 -

信號完整性

+關(guān)注

關(guān)注

68文章

1488瀏覽量

98180 -

信號失真

+關(guān)注

關(guān)注

0文章

75瀏覽量

11862 -

電源干擾

+關(guān)注

關(guān)注

0文章

36瀏覽量

4222

發(fā)布評論請先 登錄

三防漆的常見問題匯總

CW32系統(tǒng)有哪些常見問題?

改善EMC的PCB設(shè)計原理

PCB設(shè)計中單點(diǎn)接地與多點(diǎn)接地的區(qū)別與設(shè)計要點(diǎn)

深度解讀PCB設(shè)計布局準(zhǔn)則

ZYNQ UltraScalePlus RFSOC QSPI Flash固化常見問題說明

上海圖元軟件國產(chǎn)高端PCB設(shè)計解決方案

PCBA代工避坑指南:常見問題+解決方案全解析

PCB設(shè)計,輕松歸檔,效率倍增!

原理圖和PCB設(shè)計中的常見錯誤

deepin 25系統(tǒng)安裝常見問題

pcb設(shè)計常見問題和改善措施

pcb設(shè)計常見問題和改善措施

評論