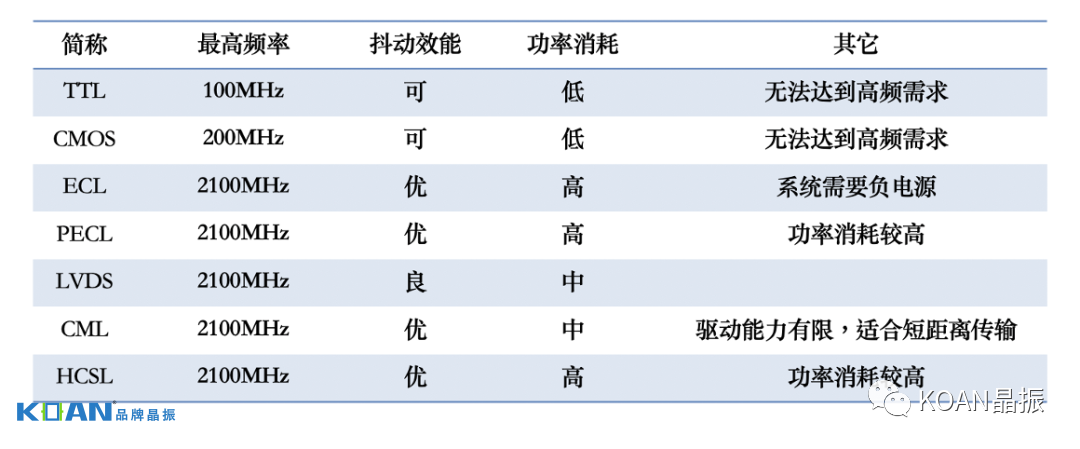

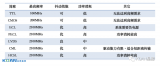

晶振的輸出波形為單端輸出(Sine/Clipped Sine, CMOS/TTL)和差分輸出(LVPECL, LVDS, HCSL)。差分輸出可以滿足高速數據傳輸,應用于高速計算機,數字通信系統,雷達,測量儀器,頻率合成器等。

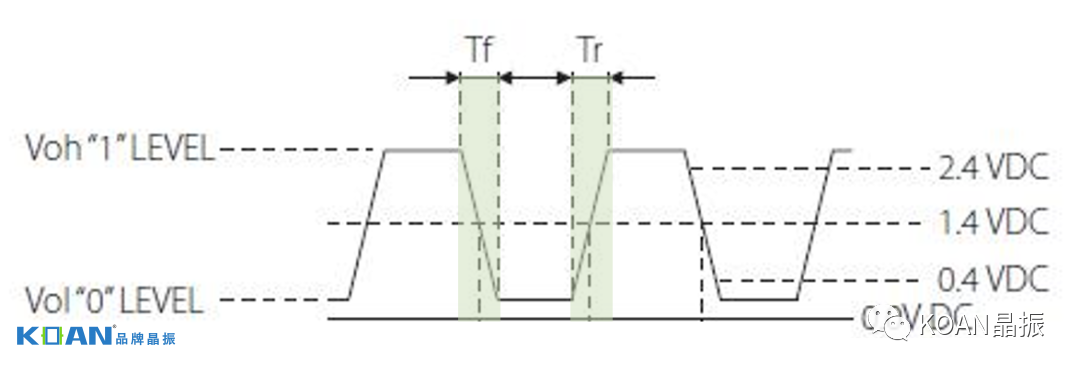

波形的上升和下降時間是有源晶振的一個主要電氣參數,單位為ns。

從CMOS輸出的波形圖來看,上升時間(Tr)指的從波形的10%處上升到波形的90%處所需要的時間(也有從20%處上升到80%的時間進行計算的)。下降時間(Tf)指的是從高值到低值所需要的時間。

KOAN有源晶振的規格書中(KS506T為例)可以看到上升下降時間的范圍值。具體電性能參數需要通過S&A280B進行測量。

我們的優勢

KOAN晶振公司配備了E5052B信號分析儀器(測量相位噪聲和抖動)、S&A280B、S&A250B測試儀器,以及高低溫箱,抗沖擊試驗設備。我們能夠檢測在溫度、負載和功率電壓變化條件下的頻率穩定性。

我們可以快速高水平滿足客戶的需求、精準化匹配、快速故障分析。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

有源晶振

+關注

關注

1文章

994瀏覽量

22807 -

晶振

+關注

關注

35文章

3564瀏覽量

73452 -

計算機

+關注

關注

19文章

7807瀏覽量

93204 -

波形

+關注

關注

3文章

407瀏覽量

33083 -

測量儀器

+關注

關注

3文章

903瀏覽量

46281

發布評論請先 登錄

相關推薦

熱點推薦

【轉帖】如何用示波器測試有源晶振波形

接入晶振,再有兩個電容分別接到晶振的兩端,每個電容的另一端再接地,這兩個電容串聯的容量值等于負載電容,請注意一般IC的引腳都有等效輸入電容,這個不能忽略。

發表于 05-25 14:32

斯巴達6上升時間下降時間怎么減少

嗨,我試圖減少上升時間和下降時間,包括在spartan 6中IO引腳的過沖。我沒有應用約束tr = 2.5nstf = 2.5ns過沖= 11%我應用了6mA的驅動約束.....為此我得到了新的結果

發表于 04-10 13:18

如何確定峰值信號的上升/下降時間?

大家好,我開發了一個用于Spartan 3e套件的VHDL PWM生成算法,一切都是預期的。但我想了解這個信號的上升/下降時間,模擬顯示理想的行為,但在范圍上我看到的東西不同。從理論上講,如何確定

發表于 07-09 05:36

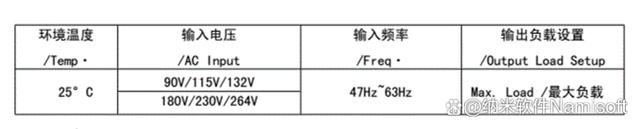

納米軟件電源模塊測試之啟動延遲和上升/下降時間

電源模塊的啟動延遲指從施加啟動輸入電壓到輸出電壓達到電壓額定值時所需的時間,上升時間是指電源模塊從歸零待機狀態到啟動狀態所需的時間,下降時間指的是電源模塊從工作狀態到歸零待機狀態所需的

有源晶振的電氣參數:波形上升下降時間

有源晶振的電氣參數:波形上升下降時間

評論