摘要

本文介紹了瑞薩在早期設計階段針對自動駕駛(AD)和高級駕駛輔助系統(tǒng)(ADAS)的SoC中用于AI處理的深度神經(jīng)網(wǎng)絡(DNN)加速器的性能、電路尺寸和功耗的工作內(nèi)容。

Yuji Obayashi

Principal Software Engineer

背景

近年,隨著深度學習(DeepLearning)人工智能(AI)技術(shù)的進步,我們的生活中出現(xiàn)了許多直接有益的應用場景,例如自動翻譯精度的提升和根據(jù)消費者喜好的個性化推薦。截至2023年,AI在某些領域已經(jīng)成為產(chǎn)品和服務中不可或缺的應用,其中之一就是自動駕駛(AD)和先進駕駛輔助系統(tǒng)(ADAS)。

以深度神經(jīng)網(wǎng)絡(DNN)為代表的最新人工智能模型的處理需要大規(guī)模的并行計算,因此在PC開發(fā)中通常使用通用的GPU進行并行計算。另一方面,用于AD和ADAS的SoC多數(shù)搭載了專用電路(以下簡稱加速器),實現(xiàn)了低功耗和高性能的DNN處理。然而,在SoC開發(fā)的早期階段,確認搭載的加速器能否在實際所需的DNN中提供足夠的性能通常并不容易。性能比較的指標常常使用加速器設計上的最大計算性能TOPS(Tera Operations Per Second)值,或者其與運行時消耗的功率相除得到的TOPS/W值。然而,由于加速器是針對特定處理的專用設計(*1),即使TOPS值足夠高,在實際所需的DNN中也可能由于存在無法高效處理的計算或數(shù)據(jù)傳輸帶寬不足等問題而無法提供足夠的性能。此外,加速器的功率增加可能導致整個SoC的功耗超過可接受的范圍。

(*1)專用設計:雖然使用通用GPU作為加速器也是可能的,但處理特定任務的硬件,可以在較小的電路規(guī)模和功耗下獲得更高的處理性能。例如瑞薩的車載SoC R-Car V3H、R-Car V3M和R-Car V4H搭載的加速器具有專為處理DNN中使用卷積操作進行特征提取的卷積神經(jīng)網(wǎng)絡(CNN)任務而設計的結(jié)構(gòu)。

隨著SoC開發(fā)的深入,由于性能不足或功耗過大等原因而進行設計變更的難度普遍增加,對SoC開發(fā)進度和開發(fā)成本的影響也隨之增加。因此,在開發(fā)面向車載AI設備的SoC時,確認搭載的加速器能否在實際顧客產(chǎn)品中所需的DNN中提供足夠的性能,并且功耗是否在可接受范圍內(nèi),已成為迫切的問題。

面向AD/ADAS的一般AI開發(fā)流程

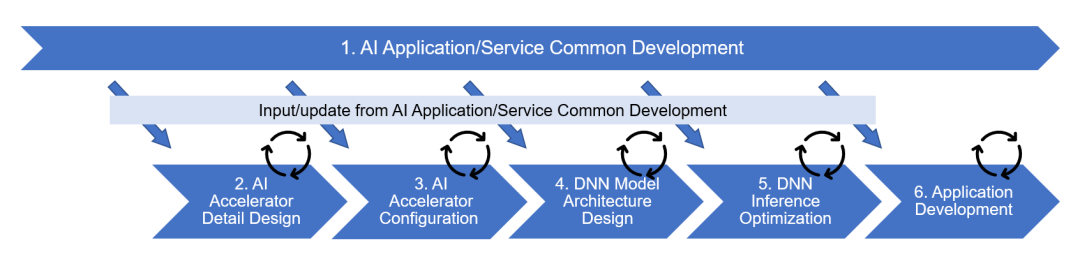

在解釋如何解決上述問題之前,先簡單介紹一下AD/ADAS的AI開發(fā)流程。下面的圖1展示了在AD/ADAS中以軟件為核心,并包括部分SoC開發(fā)的AI開發(fā)流程的示例。

圖1:AD/ADAS中AI開發(fā)流程的例子

圖1將整個開發(fā)工作分為六個階段,其中第2和第3階段為SoC電路設計,其他第1和第4-6階段為軟件開發(fā)。下面給出了每個階段的工作概述。

第一階段 AI Application/Service Common Development

利用PC和云環(huán)境,以應對市場需求和技術(shù)趨勢,開發(fā)面向AD/ADAS的AI應用程序和服務。

第二階段 AI Accelerator Detail Design

涵蓋了構(gòu)成加速器硬件的部件設計,如計算單元、內(nèi)部存儲器和數(shù)據(jù)傳輸單元。

第三階段 AI Accelerator Configuration

在第三階段中,第二階段中設計的組件被組合起來,以優(yōu)化面積、功率和性能之間的權(quán)衡,同時確定加速器在SoC中的配置以實現(xiàn)各自的設計目標。

第四階段 DNN Model Architecture Design

在第三階段中確定的加速器配置被用來優(yōu)化每個用于客戶產(chǎn)品的DNN網(wǎng)絡的結(jié)構(gòu)。

第五階段 DNN Inference Optimization

將針對經(jīng)過第四階段結(jié)構(gòu)優(yōu)化的每個網(wǎng)絡進行適用于加速器的代碼生成,并進行精度和處理時間的詳細評估。同時,將對代碼和模型數(shù)據(jù)進行優(yōu)化,以提高性能。

第六階段 Application Development

將使用第五階段中優(yōu)化的代碼和模型數(shù)據(jù),將AI處理部分嵌入到實際的自動駕駛等處理中,并進行應用的實現(xiàn)和評估。

瑞薩的工作

在上一節(jié)所示的AD/ADAS中的AI開發(fā)流程中,判斷實際使用的DNN是否能夠在所配備的加速器上提供足夠的性能,通常需要在決定加速器配置的第三階段AI Accelerator Configuration中進行決策。

傳統(tǒng)上,在這一階段的決策是通過使用類似加速器的現(xiàn)有SoC進行的基準測試結(jié)果來估計的,但對于因增加或改變功能而與現(xiàn)有SoC規(guī)格不同的部分,無法獲得基準測試結(jié)果,因此無法通過高度精確的估計來確定是否能達到設計目標。

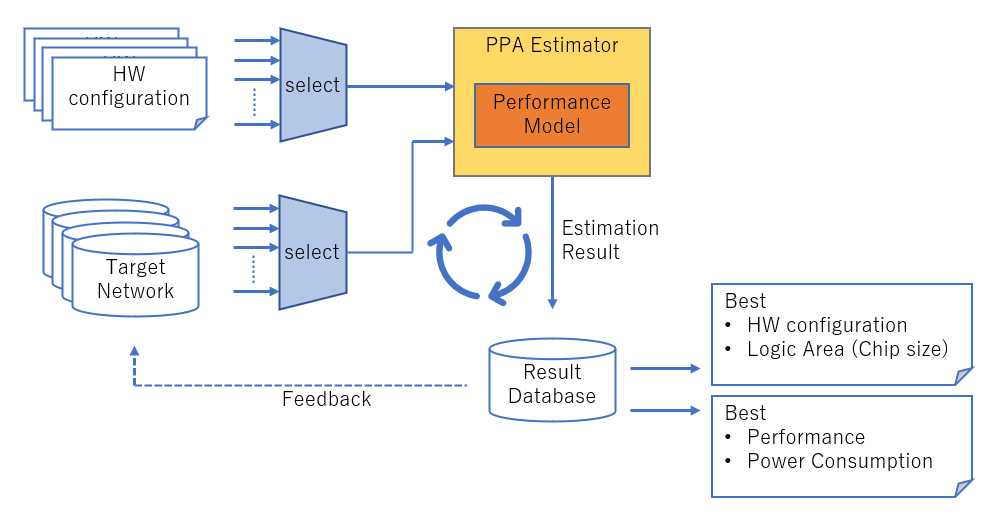

瑞薩通過使用PPA Estimator(PPA:Performance,Power,Area)而不是現(xiàn)有的SoC基準測試來解決這個課題。PPA Estimator通過使用反映加速器每個組件設計的性能和功率計算模型,使性能和功耗在加速器配置最終確定之前得到估算。具體來說,列出可能的加速器配置(可改變的加速器參數(shù)的組合,如處理單元的數(shù)量和內(nèi)部存儲器的容量)進行評估,選擇其中一個配置并與要評估的一個DNN一起輸入PPA Estimator中,以獲得所需的執(zhí)行時間和功耗。然后,可以針對所需評估的加速器配置和DNN的數(shù)量進行重復操作,收集數(shù)據(jù),并找到最佳的加速器配置。如此,不僅可以確定一個特定的加速器配置和DNN組合是否有足夠的性能,而且還可以收集廣泛的數(shù)據(jù)并從中選擇最佳加速器配置。

此外,為了使第三階段AI Accelerator Configuration更加有效,瑞薩還通過將從PPA Estimator執(zhí)行結(jié)果中獲得的信息反饋給目標DNN的網(wǎng)絡模型,并行改進軟件方面的工作,也就是進行硬件-軟件聯(lián)合設計(co-design)。AI Accelerator Configuration階段的工作流程如下圖2所示。

圖2:AI Accelerator Configuration工作流程

瑞薩已開始將PPA Estimator應用于從2023年開始的一些帶有AI處理加速器的AD/ADAS的SoC的開發(fā)中,并計劃逐步擴大應用范圍。瑞薩將利用PPA Estimator的高度精確性能尋找最佳配置以開發(fā)高性能、低功耗的車載AI加速器。

點擊文末閱讀原文獲取更多有關(guān)瑞薩當前和最新的車載AI SoC產(chǎn)品的信息。

1

END

1

瑞薩電子 (TSE: 6723)

科技讓生活更輕松,致力于打造更安全、更智能、可持續(xù)發(fā)展的未來。作為全球微控制器供應商,瑞薩電子融合了在嵌入式處理、模擬、電源及連接方面的專業(yè)知識,提供完整的半導體解決方案。成功產(chǎn)品組合加速汽車、工業(yè)、基礎設施及物聯(lián)網(wǎng)應用上市,賦能數(shù)十億聯(lián)網(wǎng)智能設備改善人們的工作和生活方式。更多信息,敬請訪問renesas.com

原文標題:工程師說 | 面向AD/ADAS的SoC的AI性能優(yōu)化

文章出處:【微信公眾號:瑞薩電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

瑞薩

+關(guān)注

關(guān)注

37文章

22481瀏覽量

90876

原文標題:工程師說 | 面向AD/ADAS的SoC的AI性能優(yōu)化

文章出處:【微信號:瑞薩電子,微信公眾號:瑞薩電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

算法工程師需要具備哪些技能?

瑞薩電子R-Car V4H ADAS SoC已應用于豐田最新RAV4車型

使用NORDIC AI的好處

瑞芯微SOC智能視覺AI處理器

重磅合作!Quintauris 聯(lián)手 SiFive,加速 RISC-V 在嵌入式與 AI 領域落地

電子發(fā)燒友工程師看!電子領域評職稱,技術(shù)之路更扎實

AI 芯片浪潮下,職場晉升新契機?

AI的未來,屬于那些既能寫代碼,又能焊電路的“雙棲人才”

智能駕駛核心器件:三星ADAS SoC高性能MLCC解決方案

芯馳科技D9-Max:面向具身智能應用的高性能邊緣AI SoC

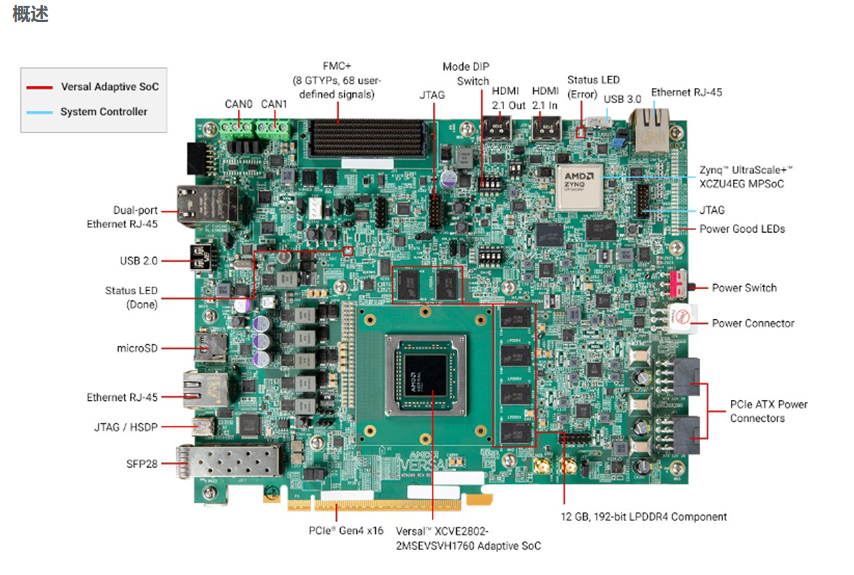

面向AI與機器學習應用的開發(fā)平臺 AMD/Xilinx Versal? AI Edge VEK280

AI眼鏡的未來:SoC芯片與SD NAND的協(xié)同優(yōu)化

電子工程師如何利用AI革新設計范式

ADAS1000 adi

工程師說 | 面向AD/ADAS的SoC的AI性能優(yōu)化

工程師說 | 面向AD/ADAS的SoC的AI性能優(yōu)化

評論