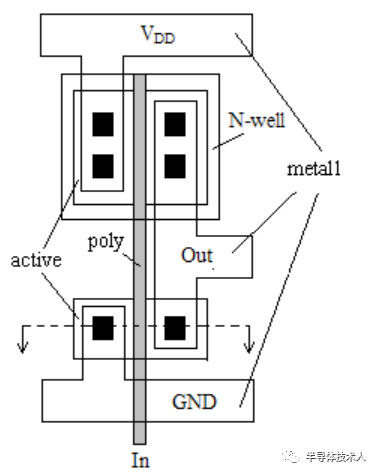

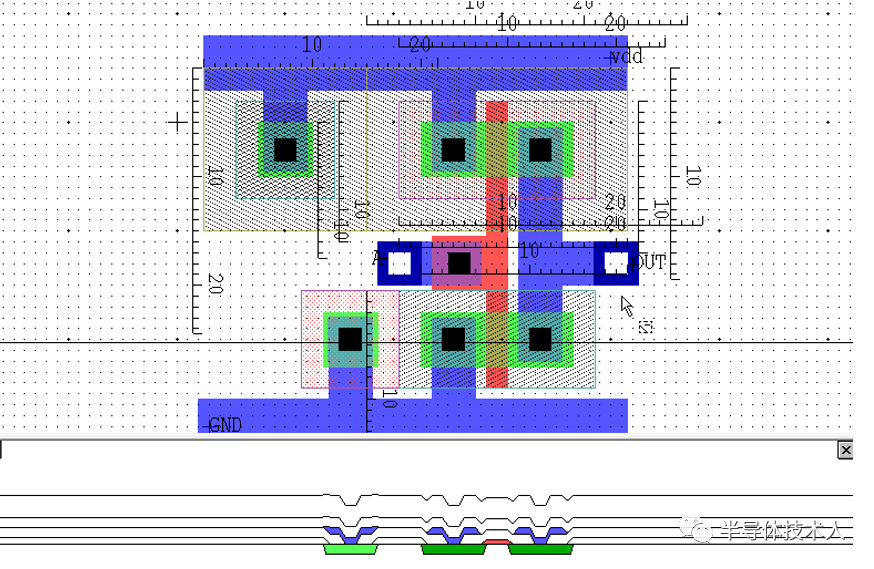

1 下圖為一個采用N阱CMOS工藝的版圖。

(1)從版圖中提取邏輯圖。

(2)此版圖中應用了哪幾種類型的設計規則?

設計規則:最小寬度,最小間距,最小包圍,最小延伸。

(3)畫出虛線處的剖面圖,并在圖中標出場氧和柵氧的位置。

CMOS工藝是在PMOS和NMOS工藝基礎上發展起來的。CMOS中的C表示“互補”,即將NMOS器件和PMOS器件同時制作在同一硅襯底上,制作CMOS集成電路。CMOS集成電路具有功耗低、速度快、抗干擾能力強、集成度高等眾多優點。CMOS工藝已成為當前大規模集成電路的主流工藝技術,絕大部分集成電路都是用CMOS工藝制造的。

CMOS中既包含NMOS晶體管也包含PMOS晶體管,NMOS晶體管是做在P型硅襯底上的,而PMOS晶體管是做在N型硅襯底上的,要將兩種晶體管都做在同一個硅襯底上,就需要在硅襯底上制作一塊反型區域,該區域被稱為“阱”。根據阱的不同,CMOS工藝分為P阱CMOS工藝、N阱CMOS工藝以及雙阱CMOS工藝。其中N阱CMOS工藝由于工藝簡單、電路性能較P阱CMOS工藝更優,從而獲得廣泛的應用。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

集成電路

+關注

關注

5452文章

12571瀏覽量

374523 -

晶體管

+關注

關注

78文章

10395瀏覽量

147730 -

CMOS工藝

+關注

關注

1文章

59瀏覽量

16125 -

NMOS管

+關注

關注

2文章

124瀏覽量

6316 -

PMOS管

+關注

關注

0文章

84瀏覽量

7495

發布評論請先 登錄

相關推薦

熱點推薦

13um應變補償多量子阱SLD臺面制作工藝的研究

13um應變補償多量子阱SLD臺面制作工藝的研究臺面制作工藝對1?3μm應變補償多量子阱SLD 的器件性能有重要的影響。根據外延結構,分析比較了兩種臺面制作的方法,即選擇性濕法腐蝕法和

發表于 10-06 09:52

版圖設計工程師-上海

、calibre等版圖工具的使用; 3、了解CMOS工藝、熟悉CMOS及高壓BCD設計規則; 4、能讀懂Command file文件; 5、具有良好的溝通能力和團隊合作精神。歡迎朋友自

發表于 03-06 15:07

版圖設計工程師-上海

、calibre等版圖工具的使用; 3、了解CMOS工藝、熟悉CMOS及高壓BCD設計規則; 4、能讀懂Command file文件; 5、具有良好的溝通能力和團隊合作精神。歡迎朋友自

發表于 03-14 15:49

版圖設計工程師-上海

、calibre等版圖工具的使用; 3、了解CMOS工藝、熟悉CMOS及高壓BCD設計規則; 4、能讀懂Command file文件; 5、具有良好的溝通能力和團隊合作精神。歡迎朋友自

發表于 03-18 17:14

版圖設計-上海

、calibre等版圖工具的使用; 3、了解CMOS工藝、熟悉CMOS及高壓BCD設計規則; 4、能讀懂Command file文件; 5、具有良好的溝通能力和團隊合作精神。歡迎朋友自

發表于 03-28 18:04

高薪誠聘IC版圖工程師

崗位職責: 1、根據項目要求熟悉相關代工廠的工藝設計規則及版圖相關要求; 2、根據設計工程師的要求完成芯片各電路的版圖設計; 3、參與模塊版圖會議,根據設計工程師的反饋意見修改

發表于 07-03 17:59

基于Cadence與Mentor的CMOS模擬集成電路版圖該如何去設計?

基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路版圖該如何去設計?怎樣去驗證一種基于Cadence virtuoso與Mentor Calibre的CMOS模擬集成電路

發表于 06-22 06:12

模塊工藝——雙阱工藝(Twin-well or Dual-Well)

CMOS 集成電路的基礎工藝之一就是雙阱工藝,它包括兩個區域,即n-MOS和p-MOS 有源區,分別對應p

基于CMOS工藝的RS422全工收發器芯片的原理及其電路版圖設計

電子發燒友網站提供《基于CMOS工藝的RS422全工收發器芯片的原理及其電路版圖設計.pdf》資料免費下載

發表于 11-17 16:40

?7次下載

雙阱工藝的制造過程

與亞微米工藝類似,雙阱工藝是指形成NW和PW的工藝,NMOS 是制造在PW里的,PMOS是制造在NW里的。它的目的是形成PN 結隔離,使器件之間形成電性隔離,優化晶體管的電學特性。

N阱CMOS工藝版圖

N阱CMOS工藝版圖

評論