01

testbench是什么

廢話不多說直接上干貨,testbench就是對寫的FPGA文件進行測試的文件,可以是verilog也可以是VHDL。

verilog和VHDL的國際標準里面有很多不能被綜合實現(xiàn)的語句,比如initial,forever,repeat,延時語句#1等等,這些語句就是用來測試的時候使用的。運行環(huán)境一般是ise或者vivado自帶的仿真工具,或者如modelsim一樣的第三方仿真工具。

02

testbench測試的機制是什么

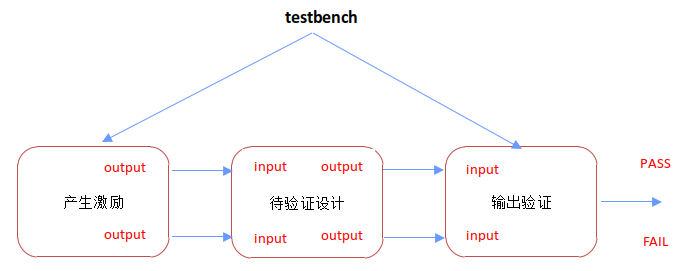

任何一個設(shè)計好的模塊(比如第一講的PWM產(chǎn)生模塊),都有輸入和輸出,此模塊是否滿足要求就是看給定滿足要求的輸入,是否能夠得到滿足要求的輸出。所以testbench的測試機制就是 :用各種verilog或者VHDL語法,產(chǎn)生滿足條件的激勵信號(也就是對被模塊的輸入),同時對模塊的輸出進行捕捉,測試輸出是否滿足要求 。如下圖,產(chǎn)生激勵輸出驗證模塊兩個模塊都屬于testbench,最好的輸出驗證模塊最終只需要給一個pass和fail的答案出來就可以了。不管是用一個信號表示pass和fail還是用$display()函數(shù)打印,最終簡單明了的給出過或者不過的信息就好了。請大家寫仿真文件的時候盡量做到這點。

03

testbench運行順序之謎

首先,跟大家解釋一點,所有testbench本質(zhì)上都是串行執(zhí)行,因為在CPU環(huán)境下,沒有可靠并行執(zhí)行的能力。所有并行的語句,比如兩個always模塊,fork join語句塊,都是軟件模擬并行執(zhí)行的。所以老一點的編譯器,信號定義要在initial語句前面,initial的信號要先有初始值后面的語句才能從給定初值開始執(zhí)行。所以大家寫testbench的時候,要注意,最好先定義信號,再寫initial語句,后面的語句交換順序不影響,軟件可以識別并按照IEEE標準的順序去執(zhí)行。

如果一個模塊里面想用并行執(zhí)行語句用fork join語句,順序執(zhí)行用begin end語句。initial語句可以寫多個,都是并行執(zhí)行的,當兩個信號在initial沖突的時候,會先執(zhí)行前面的initial的值。

04

常用testbench語句總結(jié)

時鐘產(chǎn)生——always begin clk = 0; #1 clk = 1; #1; end 。注意這里的always后面沒有@!沒有@的時候always代表永遠循環(huán)執(zhí)行begin end之間的語句,如果有@,后面一定要加時鐘,代表時鐘邊沿來到的時候順序執(zhí)行begin end里面的語句。沒有@的always語句不可綜合。

時間軸設(shè)置——'timescale 仿真時間單位/時間精度; 比如`timescale 1ns / 1ps;代表仿真的時間軸單位是1ns,仿真工具仿真的最大精度只到1ps內(nèi)的邏輯變化。

延時語句——#n; 代表延時n個時間軸單位。比如之前定義了`timescale 1ns / 1ps;如果后面寫 #3;就代表延時3ns而不是延時3ps。

初始化——initial begin a=0; #100; a=1; end。testbench在運行起來之后,第一個進入初始化語句,并且只執(zhí)行一次停在最后一句,然后才是后面的語句。由于begin end里面的語句是串行執(zhí)行的,所以這句話代表a低電平100ns后永遠為高。復(fù)位信號常常這樣產(chǎn)生。

系統(tǒng)函數(shù)——**stop;代表運行到這一句停止仿真,**dispaly("pass");代表在命令行顯示pass這串字符。

等待語句——wait(條件表達式) 語句/語句塊; 語句塊可以是串行塊(begin…end)或并行塊(fork…join)。當邏輯表達式為“真”時,語句塊立即得到執(zhí)行;否則,暫停進程并等待,直到邏輯表達式變?yōu)椤罢妗保匍_始執(zhí)行后面的語句。

關(guān)于verilog測試激勵的語法請打開,里面有所有的仿真激勵:

打開菜鳥教程——資料下載——選擇“verilog最經(jīng)典中文教程”

另外提一句:學verilog要知道verilog語句的執(zhí)行順序和機制,生成的對應(yīng)時序,哪些語句可綜合哪些不可綜合。這是最基礎(chǔ)的要求。

05

其實看了之前的鏈接大部分大家應(yīng)該都能看明白了,現(xiàn)在只揀之前沒講的代碼講。

-

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

431瀏覽量

28138 -

交換機

+關(guān)注

關(guān)注

23文章

2904瀏覽量

104466 -

VHDL語言

+關(guān)注

關(guān)注

1文章

113瀏覽量

19394 -

PWM模塊

+關(guān)注

關(guān)注

0文章

14瀏覽量

9673

發(fā)布評論請先 登錄

testbench設(shè)置的問題

LFSR testbench V1.2

Writing Testbench

testbench怎么寫_testbench經(jīng)典教程VHDL

簡單的Testbench設(shè)計

使用Matlab和Verilog實現(xiàn)fibonacci序列包括源代碼和testbench

典型的UVM Testbench架構(gòu)

Verilog Testbench怎么寫 Verilog Testbench文件的編寫要點

Testbench的基本組成和設(shè)計規(guī)則

Testbench自動化驗證方法介紹

編寫高效Testbench的指南和示例

testbench是什么? testbench測試的機制是什么?

testbench是什么? testbench測試的機制是什么?

評論