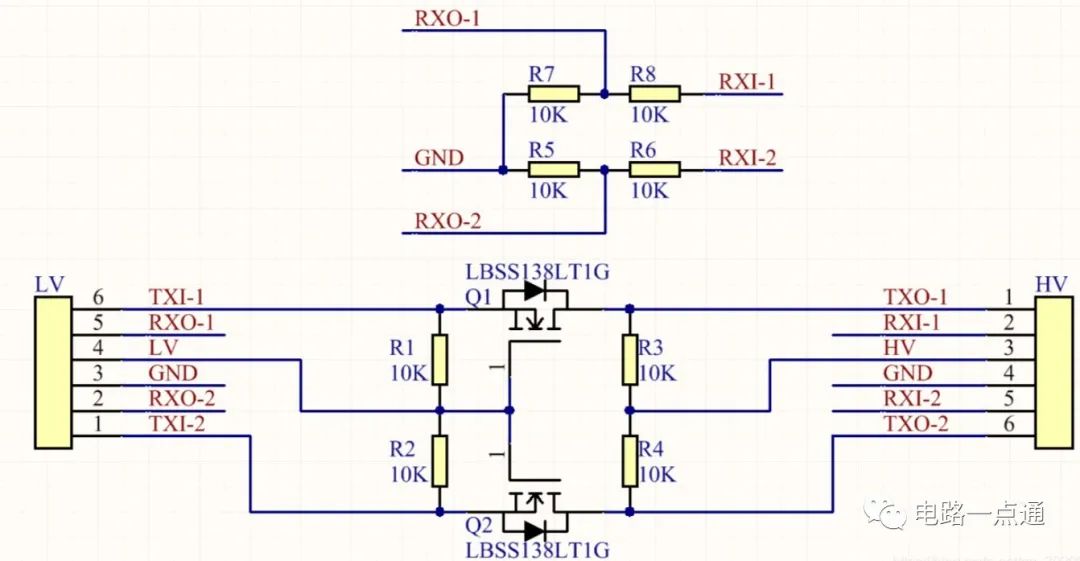

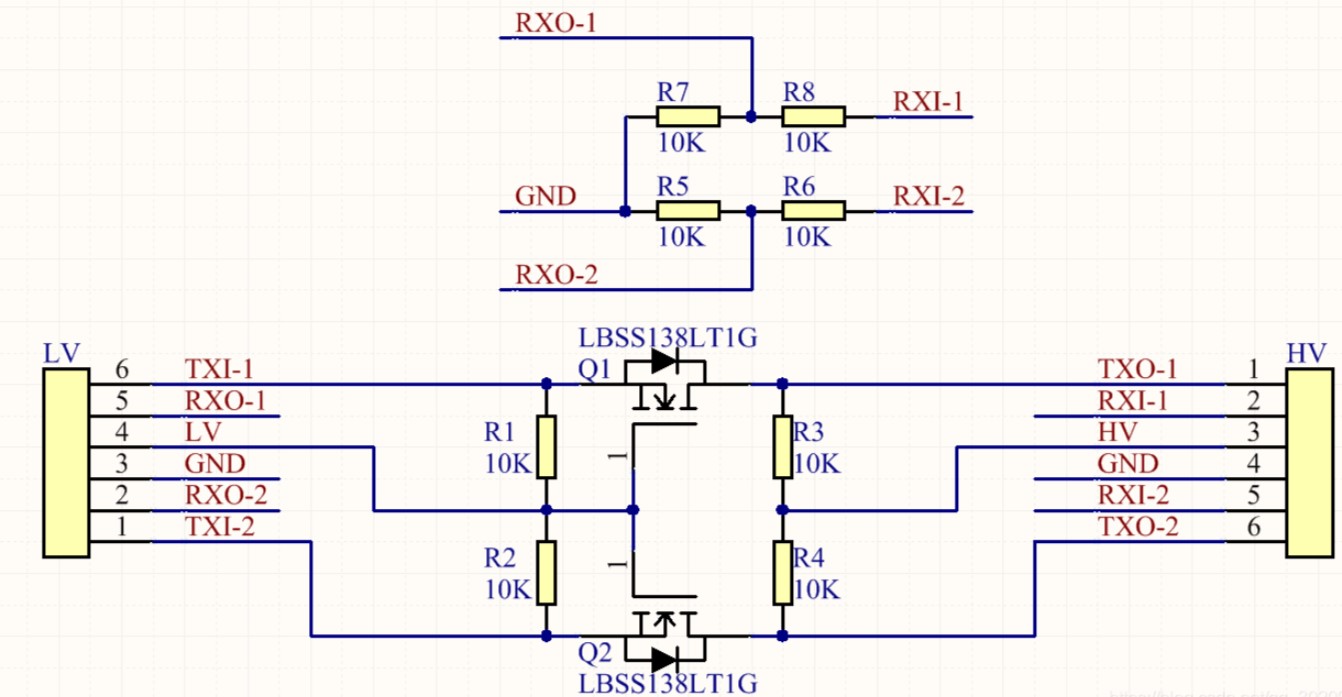

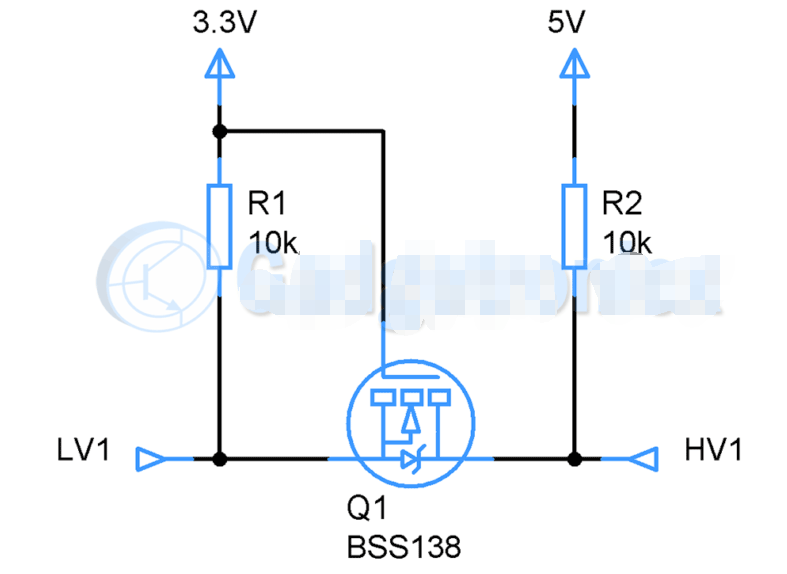

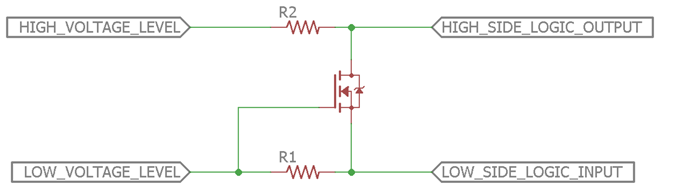

當(dāng)LV連接器的TXI-1為3V3高電平信號(LV排針接3V3,HV排針接5V)時,Q1 mos管的柵極和源極之間的壓降為0V(TXI-1與LV排針之間的電壓),此時Q1 mos管不導(dǎo)通,TXO-1被R3電阻拉高,輸出5V高電平。

當(dāng)LV連接器的TXI-1為0V低電平信號(LV排針接3V3,HV排針接5V)時,Q1 mos管的柵極和源極之間的壓降為3V3(TXI-1與LV排針之間的電壓),此時Q1 mos管導(dǎo)通,TXO-1與TXI-1電平相等,輸出0V低電平。

當(dāng)HV連接器的TXO-1為5V高電平信號(LV排針接3V3,HV排針接5V)時,Q1 mos管的柵極和源極之間的壓降為0V(TXI-1與LV排針之間的電壓),此時Q1 mos管不導(dǎo)通,TXI-1被R1電阻拉高,輸出3V3高電平。

當(dāng)HV連接器的TXO-1為0V低電平信號(LV排針接3V3,HV排針接5V)時,Q1 mos管的柵極和源極之間的壓降為0V(TXI-1與LV排針之間的電壓),此時Q1 mos管不導(dǎo)通,單是Q1 mos管的寄生二極管導(dǎo)通,壓降為0.3V,TXI-1電平為0.3V,輸出0.3V低電平(屬于低電平)。

發(fā)送二路

當(dāng)LV連接器的TXI-2為3V3高電平信號(LV排針接3V3,HV排針接5V)時,Q2 mos管的柵極和源極之間的壓降為0V(TXI-1與LV排針之間的電壓),此時Q2 mos管不導(dǎo)通,TXO-2被R4電阻拉高,輸出5V高電平。

當(dāng)LV連接器的TXI-2為0V低電平信號(LV排針接3V3,HV排針接5V)時,Q2 mos管的柵極和源極之間的壓降為3V3(TXI-1與LV排針之間的電壓),此時Q2 mos管導(dǎo)通,TXO-2與TXI-2電平相等,輸出0V低電平。

當(dāng)HV連接器的TXO-2為5V高電平信號(LV排針接3V3,HV排針接5V)時,Q2 mos管的柵極和源極之間的壓降為0V(TXI-2與LV排針之間的電壓),此時Q2 mos管不導(dǎo)通,TXI-2被R2電阻拉高,輸出3V3高電平。

當(dāng)HV連接器的TXO-2為0V低電平信號(LV排針接3V3,HV排針接5V)時,Q2 mos管的柵極和源極之間的壓降為0V(TXI-2與LV排針之間的電壓),此時Q2 mos管不導(dǎo)通,單是Q2 mos管的寄生二極管導(dǎo)通,壓降為0.3V,TXI-2電平為0.3V,輸出0.3V低電平(屬于低電平)

接收路

RX接收端只是簡單的用2個電阻分壓,將5V電平信號轉(zhuǎn)換為2.5V電平信號,因為2.5V在3.3V單片機系統(tǒng)的高電平電壓范圍內(nèi),會被識別為高電平,但是建議使用合適的電阻將電平分壓到3.3V。

審核編輯:湯梓紅

-

連接器

+關(guān)注

關(guān)注

104文章

16234瀏覽量

147560 -

MOS管

+關(guān)注

關(guān)注

111文章

2801瀏覽量

77478 -

邏輯電平

+關(guān)注

關(guān)注

0文章

205瀏覽量

15133 -

電平轉(zhuǎn)換電路

+關(guān)注

關(guān)注

1文章

47瀏覽量

14245

原文標(biāo)題:邏輯電平轉(zhuǎn)換電路原理講解

文章出處:【微信號:電路一點通,微信公眾號:電路一點通】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

邏輯電平轉(zhuǎn)換電路原理講解

邏輯電平轉(zhuǎn)換說明

邏輯電平轉(zhuǎn)換芯片的問題

邏輯電平轉(zhuǎn)換

電平轉(zhuǎn)換器,電平轉(zhuǎn)換器原理和相關(guān)電路分析

傳統(tǒng)邏輯電平轉(zhuǎn)換方法及其優(yōu)缺點

FPGA邏輯電平的互連電平轉(zhuǎn)換詳細說明

雙向電平轉(zhuǎn)換電路——AiP2206

邏輯電平轉(zhuǎn)換

將5v轉(zhuǎn)換為3.3v的邏輯電平轉(zhuǎn)換器電路

什么是邏輯電平?如何實現(xiàn)電平轉(zhuǎn)換?(原理講解+電路圖)

邏輯電平轉(zhuǎn)換電路原理講解

邏輯電平轉(zhuǎn)換電路原理講解

評論