PCB的阻焊層(solder mask),是指印刷電路板子上要上綠油的部分。阻焊開窗的位置是不上油墨的,露出來的銅做表面處理后焊接元器件的位置,不開窗的位置都是印上油墨的防止線路氧化、漏電。

PCB阻焊層開窗的三個原因

1.孔焊盤開窗:插件孔焊盤都需要開窗,開窗了才能焊接元器件,不開窗焊接的位置會被油墨蓋住,導(dǎo)致器件引腳無法焊接。

2.PAD焊盤開窗:開窗的位置就是貼片的位置,需要貼片焊接元器件,如果要焊接的位置不開窗,會被油墨蓋住,等于沒有焊盤。

3.大銅面開窗:有時候需要在不增加PCB走線寬度的情況下提高該走線通過大電流的能力,通常是在PCB走線上鍍錫,所以需要鍍錫的位置需要開窗處理。

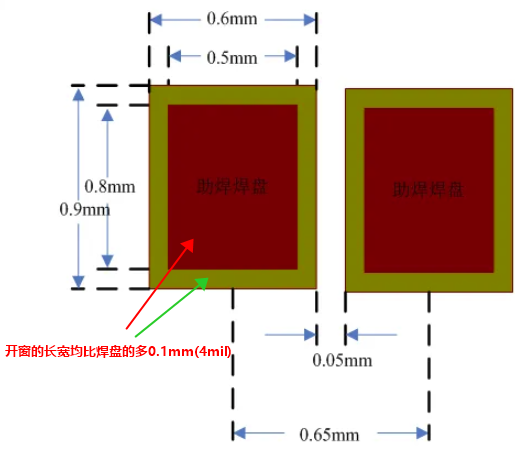

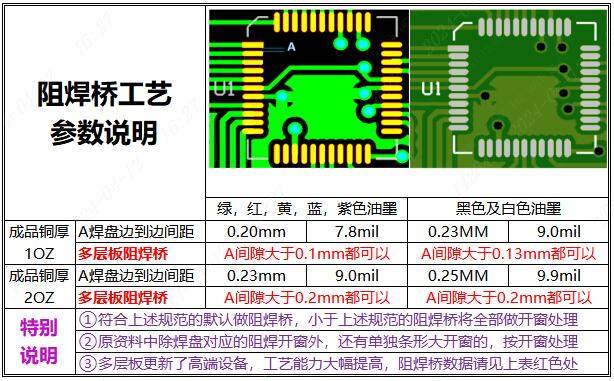

阻焊開窗為什么要比線路的PAD大

一般開窗比線路焊盤大,如果阻焊開窗區(qū)域面積跟焊盤一樣大,由于PCB生產(chǎn)制造的公差,就無法避免阻焊綠油覆蓋到焊盤上,所以一般為了兼顧板廠的工藝偏差,我們都要讓阻焊開窗區(qū)域比實際焊盤擴(kuò)大一定的尺寸,按照一般板廠的生產(chǎn)公差,建議大整體4-6mil(0.1-0.15mm)。

阻焊漏開窗的原因

01

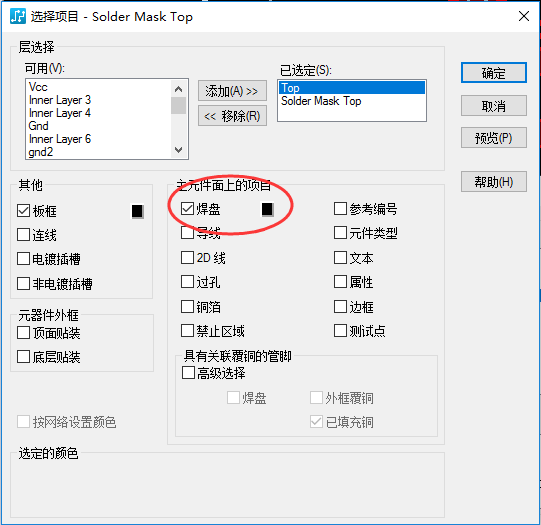

輸出Gerber漏開窗

在設(shè)計工程師layout過程中,誤操作或?qū)erber文件輸出設(shè)置有誤。阻焊層輸出時沒有勾選開窗焊盤,導(dǎo)致輸出Gerber阻焊層漏開窗。

02

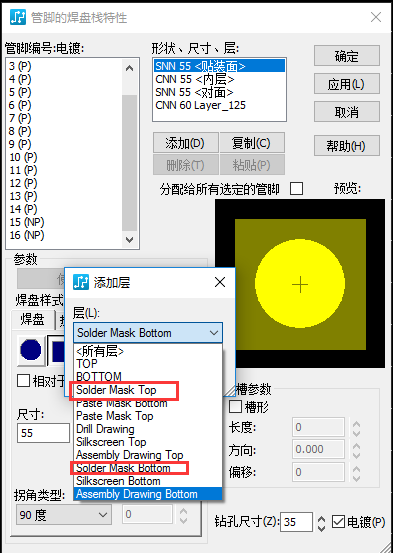

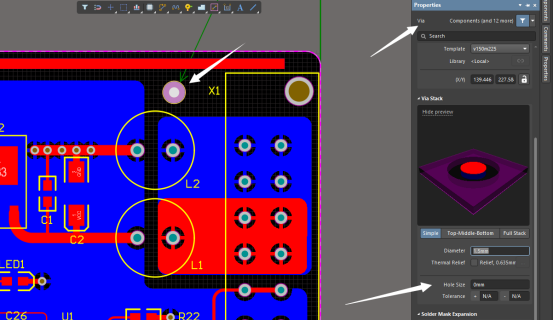

封裝設(shè)計阻焊層無開窗

在做pcb封裝時,設(shè)置錯誤的原因?qū)е吕L制的封裝沒有開窗。解決辦法是做好焊盤,只需要在焊盤棧特性對話框下的形狀、尺寸、層里點擊添加solder mask top(或者bottom),然后修改好solder mask的形狀,即實現(xiàn)了pad的開窗。

在做pcb封裝時,設(shè)置錯誤的原因?qū)е吕L制的封裝沒有開窗。解決辦法是做好焊盤,只需要在焊盤棧特性對話框下的形狀、尺寸、層里點擊添加solder mask top(或者bottom),然后修改好solder mask的形狀,即實現(xiàn)了pad的開窗。

03

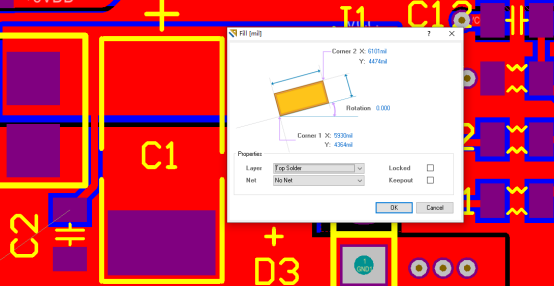

軟件版本兼容性導(dǎo)致漏開窗

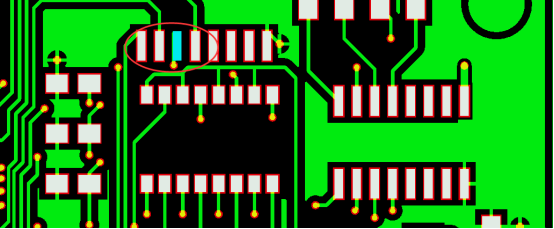

因EDA軟件的版本眾多,由于設(shè)計工程師layout時使用了高版本的AD軟件,焊盤是使用Track畫出來的,在傳統(tǒng)的低版本中是走線的意思,一般Track是不會有阻焊開窗的。但是在高版本AD中新增了一個功能,就是給予了Track特殊屬性,因此高版本輸出Gerber有開窗,低版本無開窗,導(dǎo)致輸出的Gerber文件漏開窗。

04

孔屬性錯誤導(dǎo)致漏開窗

在AD軟件里面添加焊盤時有PAD和VIA添加方式,PAD為焊盤,VIA為過孔。如果需要開窗焊接的使用VIA添加,在制版過程中過孔蓋油需取消開窗。此時,所有VIA屬性的開窗全部取消掉了,要開窗焊接的VIA屬性的就會漏開窗。

05

修改文件導(dǎo)致漏開窗

在更新迭代升級過程中經(jīng)過多次改版,或者某些抄板文件在通過圖片繪制過程中,可能會因為誤操作導(dǎo)致誤刪設(shè)計文件開窗,因此設(shè)計文件漏開窗無法焊接。

結(jié)語:綜上,為避免阻焊漏開窗現(xiàn)象的出現(xiàn),我們在PCB設(shè)計時嚴(yán)格執(zhí)行相關(guān)標(biāo)準(zhǔn),包括孔定義與器件放置規(guī)定等;同時,對于提供的設(shè)計文件,如Gerber文件,需進(jìn)行必要的檢查,避免文件出現(xiàn)問題。

當(dāng)然,更簡單的方法是用華秋DFM去分析我們設(shè)計的PCB文檔,不僅能快速檢測出漏開窗的問題,還能進(jìn)行全面的PCB裸板分析、阻抗計算、PCBA裝配分析、價格交期評估等,滿足工程師多場景需求。

華秋DFM軟件下載地址(復(fù)制到瀏覽器下載):https://dfm.elecfans.com/uploads/software/promoter/hqdfm_hqdl?.zip

領(lǐng)取后PC端打開可查看:http://url.elecfans.com/u/98df74a38c

領(lǐng)取后PC端打開可查看:http://url.elecfans.com/u/98df74a38c

-

pcb

+關(guān)注

關(guān)注

4412文章

23917瀏覽量

425494 -

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4929瀏覽量

95612

發(fā)布評論請先 登錄

03. 如何把 PCB 板上的線變成銅皮?| 芯巧Allegro PCB 設(shè)計小訣竅

過孔焊盤,你真的了解嗎?PCB設(shè)計中的“隱形殺手”揭秘

PCB設(shè)計避坑指南——孔/槽篇

PCB阻焊覆蓋的唯一依據(jù):Gerber文件

SMT漏印問題“終結(jié)指南”:手把手教你排查與解決

榮德PCB生產(chǎn)制造設(shè)備,阻焊油墨的高速自動噴涂線#pcb設(shè)計 #PCB生產(chǎn) #阻焊油墨 #噴涂設(shè)備

線路板阻焊工藝對PCB的可靠性有何影響?

什么是SMD&NSMD,怎么區(qū)分呢?

PCB設(shè)計中過孔為什么要錯開焊盤位置?

求教!BGA板子阻焊開窗怎么處理比較好?

PCB阻焊橋脫落與LDI工藝

Altium Designer中PCB設(shè)計規(guī)則設(shè)置

PCB設(shè)計時如何防止阻焊漏開窗?

PCB設(shè)計時如何防止阻焊漏開窗?

評論