PCB工程師layout一款產(chǎn)品,不僅僅是布局布線,內(nèi)層的電源平面、地平面的設(shè)計也非常重要。處理內(nèi)層不僅要考慮電源完整性、信號完整性、電磁兼容性,還需要考慮DFM可制造性。

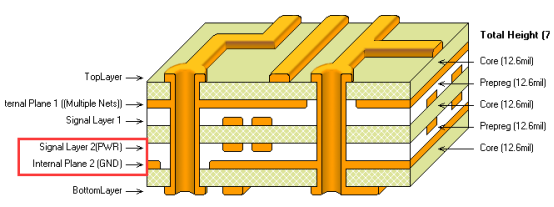

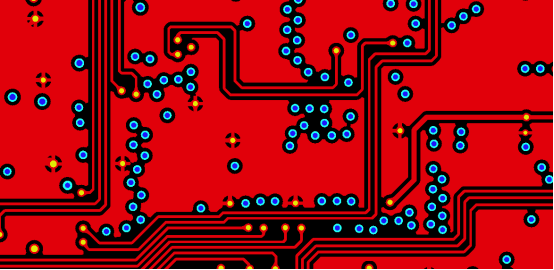

PCB內(nèi)層與表層的區(qū)別,表層是用來走線焊接元器件的,內(nèi)層則是規(guī)劃電源/接地層,該層僅用于多層板,主要用于布置電源線和接地線。我們稱之為雙層板、四層板和六層板,通常指信號層和內(nèi)部電源/接地層的數(shù)量。

內(nèi)層設(shè)計

在高速信號,試中信號,高頻信號等關(guān)鍵信號的下面設(shè)計地線層,這樣信號環(huán)路的路徑最短,輻射最小。

高速電路設(shè)計過程中必須考慮如何處理電源的輻射和對整個系統(tǒng)的干擾。一般情況要使電源層平面的面積小于地平面的面積,這樣可以對電源起屏蔽作用。一般要求電源平面比地平面縮進(jìn)2倍的介質(zhì)厚度。

層疊規(guī)劃

01

電源層平面與相應(yīng)的地平面相鄰。目的是形成耦合電容,并與PCB板上的去耦電容共同作用,降低電源平面阻抗,同時獲得較寬的濾波效果。

參考平面

02

參考層的選擇非常重要,理論上電源層和地平面層都能作為參考層,但是地平面層一般可以接地,屏蔽效果要比電源層好很多,所以一般優(yōu)先選擇地平面作為參考平面。

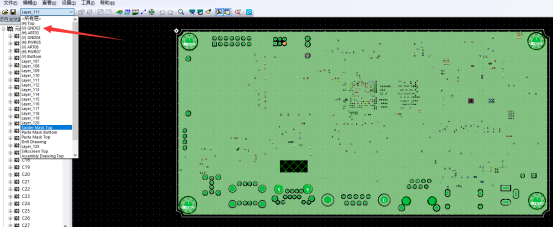

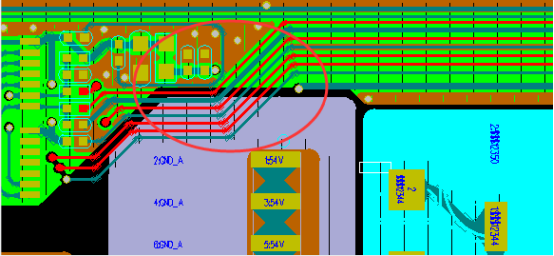

信號線不能跨區(qū)域走線

03

相鄰兩層的關(guān)鍵信號不能跨分割區(qū),否則會形成較大的信號環(huán)路,產(chǎn)生較強(qiáng)的輻射和耦合。

電源、地走線規(guī)劃

04

要保持地平面的完整性,不能在地平面走線,如果信號線密度太大,可以考慮在電源層的邊緣走線。

內(nèi)層制造

由于PCB制造復(fù)雜的工藝流程,內(nèi)層制造的工藝只是其中一部分,在生產(chǎn)內(nèi)層板時還需考慮其他工序的工藝影響內(nèi)層的制造能力。比如壓合公差、鉆孔公差都會影響內(nèi)層的品質(zhì)良率。

PCB的層數(shù)不同,可分為單面板、雙面板、多層板,這三種板子工藝流程也大不相同。尤其是多層板,生產(chǎn)工藝比單雙面板復(fù)雜許多。因此在設(shè)計多層板時,需考慮多層板復(fù)雜的工藝流程及DFM可制造性設(shè)計。

01

刪除獨(dú)立焊盤

獨(dú)立焊盤就是非功能性的PAD,在內(nèi)層不與任何網(wǎng)絡(luò)相連,在PCB制造過程中會取消獨(dú)立焊盤。因?yàn)榇霜?dú)立焊盤取消對產(chǎn)品的設(shè)計功能無影響,反而在制造時會影響品質(zhì)及生產(chǎn)效率。

02

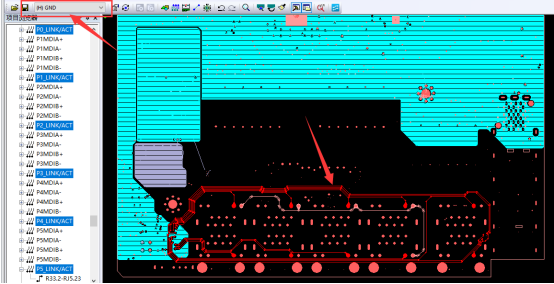

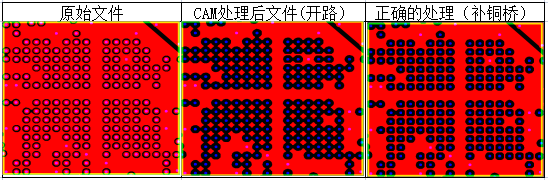

內(nèi)層BGA區(qū)域

BGA器件比較小,引腳非常多,因此扇出的過孔非常密集。在制造過程中鉆孔到走線、銅皮需要保留一定的間距,否則在壓合及鉆孔工序可能會短路。在保證鉆孔距銅皮、走線留一定的距離時,孔與孔中間的銅無法保留,會導(dǎo)致網(wǎng)絡(luò)開路。因此在CAM工程師處理BGA區(qū)域時需注意孔與孔中間的銅開路了需補(bǔ)銅橋,保證生產(chǎn)后網(wǎng)絡(luò)連接不斷開。

03

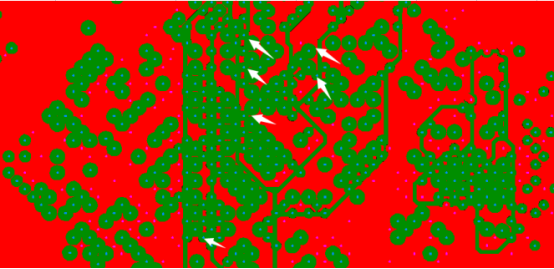

內(nèi)層設(shè)計異常

內(nèi)層負(fù)片的孔全部有孔環(huán),轉(zhuǎn)成正片圖形就是所有孔與銅皮不相連完全隔離。完全隔離就等于內(nèi)層沒有任何作用,不做內(nèi)層都可以。生產(chǎn)制造遇到此問題會跟設(shè)計工程師確認(rèn),是否設(shè)計異常,內(nèi)層銅皮沒有添加網(wǎng)絡(luò)導(dǎo)致完全隔離。

04

內(nèi)層負(fù)片瓶頸

在內(nèi)層設(shè)計電源層、地層分割時,由于過孔密集會出現(xiàn)網(wǎng)絡(luò)導(dǎo)通的瓶頸。電源網(wǎng)絡(luò)導(dǎo)通的銅橋?qū)挾炔粔颍瑫?dǎo)致過不了相匹配的電流,從而導(dǎo)致燒板。甚至有些瓶頸位置直接開路,導(dǎo)致產(chǎn)品設(shè)計失敗。

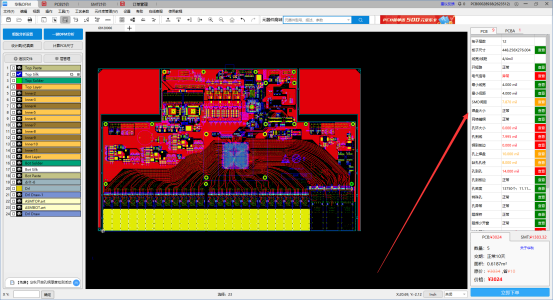

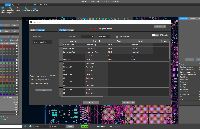

DFM內(nèi)層設(shè)計檢測

華秋DFM的檢測項(xiàng),對于上文提到的可制造性問題都能夠檢測出來,并提示存在的制造風(fēng)險,設(shè)計工程師使用華秋DFM可在制造前發(fā)現(xiàn)設(shè)計存在的缺陷。在制造前修改檢測的問題點(diǎn),避免設(shè)計的產(chǎn)品在制造過程中出現(xiàn)問題,從而提升產(chǎn)品的成功率,減少多次試樣的成本。

-

pcb

+關(guān)注

關(guān)注

4404文章

23877瀏覽量

424227 -

DFM

+關(guān)注

關(guān)注

8文章

490瀏覽量

31348

發(fā)布評論請先 登錄

射頻PCB的“隱形殺手”:90%的工程師都忽視的鋪銅細(xì)節(jié)!

開關(guān)電源平面變壓器的技術(shù)特性和制作注意事項(xiàng)

PCB接地設(shè)計實(shí)戰(zhàn)避坑指南:從“環(huán)路”到“干凈地”的進(jìn)階之路

什么是BSP工程師

到底DDR走線能不能參考電源層啊?

想成為硬件工程師?我教你啊!你得先學(xué)會這些...... #硬件工程師 #電子工程師 #電子愛好者 #電子行業(yè)

華秋DFM軟件丨操作教程——工具菜單-阻抗計算篇

降低adc在不同PCB上的噪聲,如何做到接近AD4134驗(yàn)證板噪聲水平?

PCB疊層設(shè)計避坑指南

PCB 裸板烘干除潮要求及形變(平面度)如何控制?

硬件工程師看了只會找個角落默默哭泣#硬件工程師 #MDD #MDD辰達(dá)半導(dǎo)體 #產(chǎn)品經(jīng)理 #軟件工程師

PCB的EMC設(shè)計(一):層的設(shè)置與排布原則

PCB工程師layout分享:內(nèi)層的電源平面、地平面的設(shè)計

PCB工程師layout分享:內(nèi)層的電源平面、地平面的設(shè)計

評論