Allegro和 Sigrity 軟件最新發(fā)布了一系列的產(chǎn)品更新(SPB17.4 QIR4 release)。我們將通過(guò)實(shí)例講解、視頻演示讓您深入了解 Allegro PCB Editor、Allegro System Capture、Allegro Package Designer Plus(本期內(nèi)容)、Sigrity Aurora(本期內(nèi)容)、Sigrity SystemSI、Sigrity SystemPI等產(chǎn)品的新功能及用法,助力提升設(shè)計(jì)質(zhì)量和設(shè)計(jì)效率。

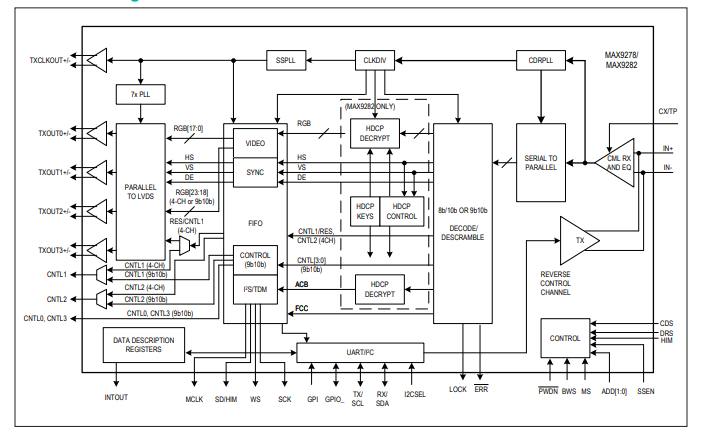

Cadence Sigrity Aurora 為 PCB 設(shè)計(jì)前、設(shè)計(jì)中和布局后提供傳統(tǒng)的信號(hào)和電源完整性 (SI/PI) 分析,結(jié)合 Cadence Allegro PCB 編輯和布線技術(shù),Sigrity Aurora用戶在設(shè)計(jì)初期就可以使用 “What-if” 探索環(huán)境進(jìn)行分析,從而獲得更準(zhǔn)確的設(shè)計(jì)約束并減少設(shè)計(jì)迭代。

Sigrity Aurora 直接讀寫 Allegro PCB 數(shù)據(jù)庫(kù),可快速準(zhǔn)確地整合設(shè)計(jì)和分析結(jié)果。它提供了一個(gè)基于 SPICE 仿真器和獲得專利的 Sigrity 嵌入式混合場(chǎng)求解器,用于二維和三維結(jié)構(gòu)提取。同時(shí)支持兼顧電源影響(Power-Aware)的 IBIS 模型,如需要還支持晶體管級(jí)別的模型。高速信號(hào)可以在布局階段中或布局階段后,對(duì)比備選方案進(jìn)行研究,以便對(duì)所有相關(guān)信號(hào)進(jìn)行全面分析。

在最新的 SPB 17.4 版本中,Cadence Sigrity Aurora 主要在以下幾個(gè)方面對(duì)互連建模的仿真功能進(jìn)行了更新:

支持對(duì)未布線網(wǎng)絡(luò)的拓?fù)涮崛〖敖#?/strong>支持布線前按照預(yù)拉線曼哈頓長(zhǎng)度拓?fù)涮崛。⑦M(jìn)行信號(hào)互連搭建,進(jìn)行信號(hào)完整性仿真分析。

支持 Clarity 3D Solver 和 Sigrity PowerSI 引擎直接集成:在 Aurora 環(huán)境中,可以通過(guò)選擇需要提取的網(wǎng)絡(luò)調(diào)用 Clarity3D Solver 和 Sigrity PowerSI 引擎進(jìn)行 S參數(shù) 的仿真建模。

IR Drop 直流電壓降仿真支持自動(dòng)剪切功能:自動(dòng)剪切功能,可以加快仿真的速度,針對(duì)大型 PCB 的區(qū)域分析及部分電路仿真提升仿真的速度。

新增生成同軸電纜和雙絞線電纜的模型:生成同軸電纜和雙絞線建模,支持框架及參數(shù)建模和自定義參數(shù)建模的辦法,通過(guò)修改編輯支持直接進(jìn)行信號(hào)互連拓?fù)浼靶盘?hào)互連仿真。

Sigrity Aurora

互連建模仿真亮點(diǎn)——

#4 新增生成同軸電纜和雙絞線電纜的模型

Aurora_TopWbench_SPB 17.4 更新之后,支持生成同軸電纜和雙絞線建模。同時(shí)支持同軸電纜和雙絞線建模的修改編輯以及進(jìn)行信號(hào)互連拓?fù)浼靶盘?hào)互連仿真。

1?

實(shí)例講解 · 視頻版

建議在WIFI環(huán)境下觀看,并注意調(diào)整音量

2?

實(shí)例講解 · 圖文版

1

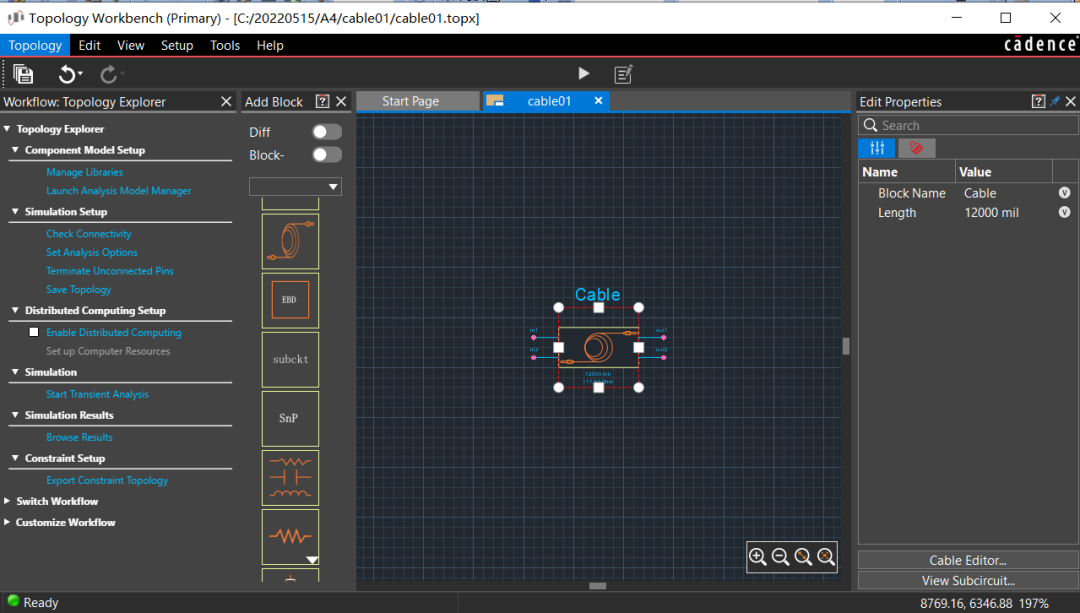

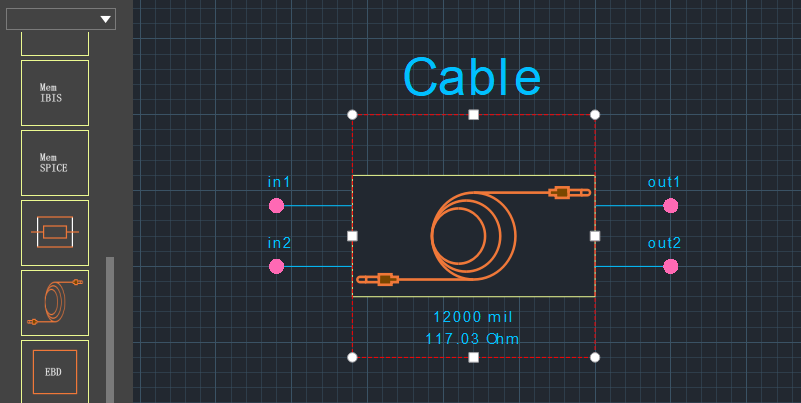

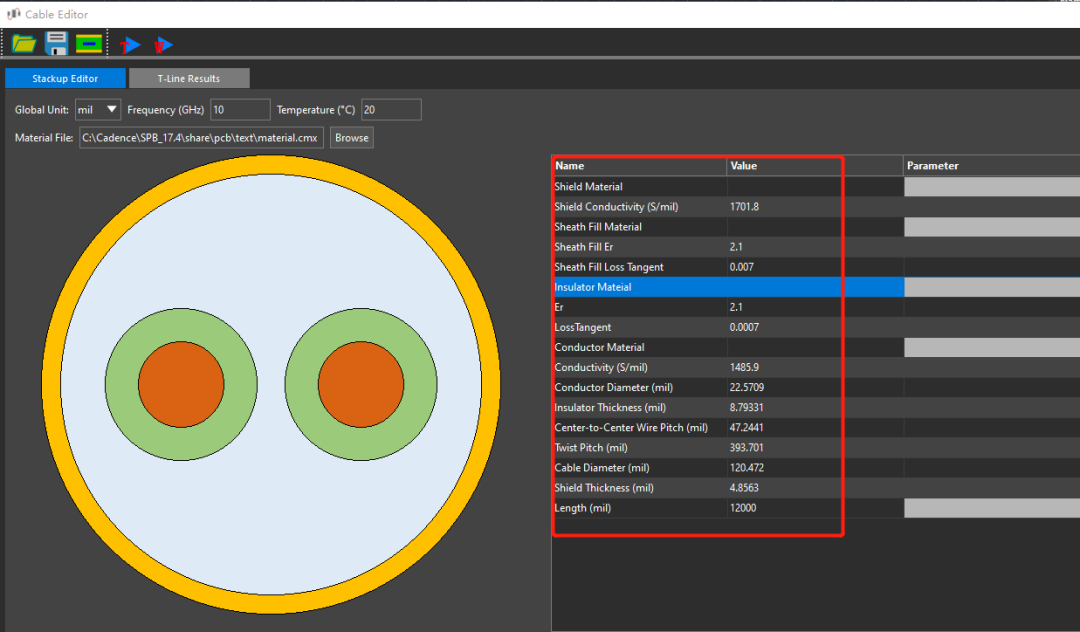

選擇Cable模型后,可以看到默認(rèn)的電纜模型參數(shù)。In1,In2,out1,out2 是模型默認(rèn)端口。1200mil 是電纜默認(rèn)的長(zhǎng)度數(shù)據(jù),117.03Ohm 是默認(rèn)的阻抗數(shù)據(jù)。

2

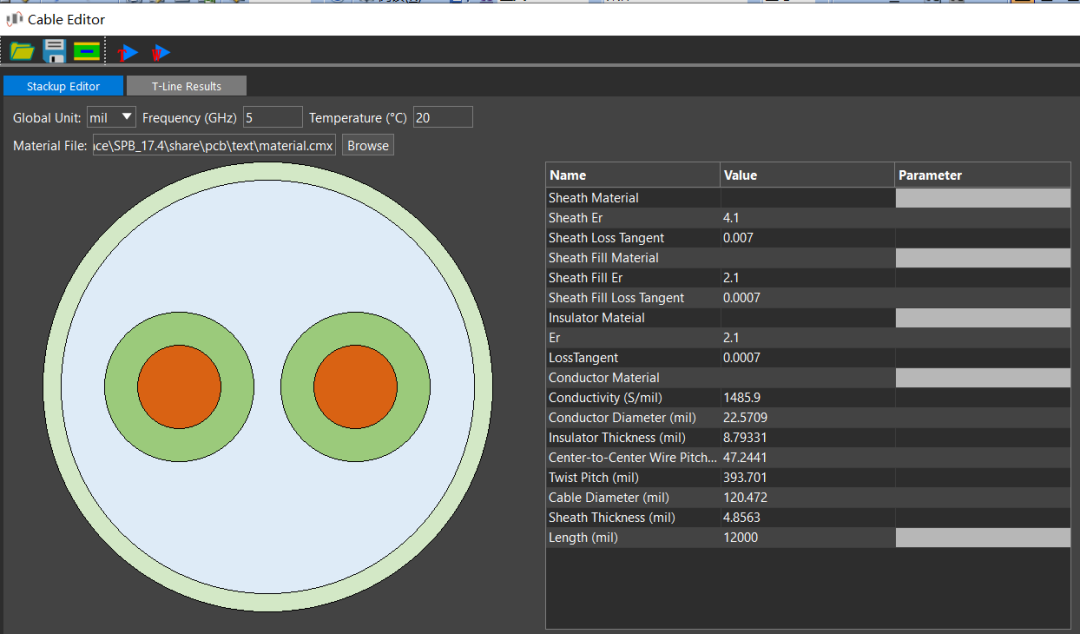

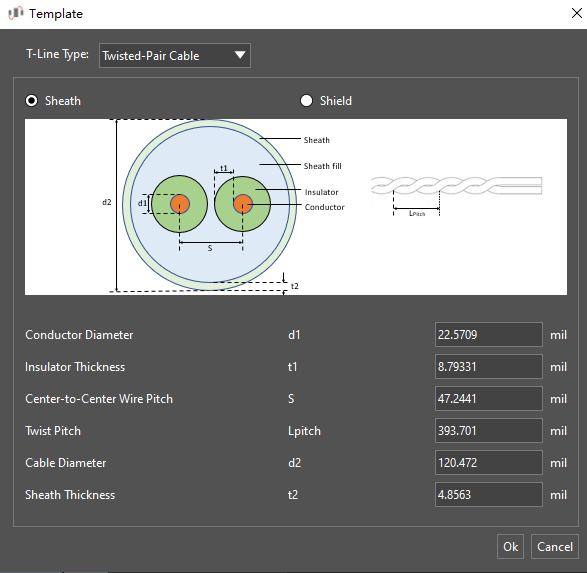

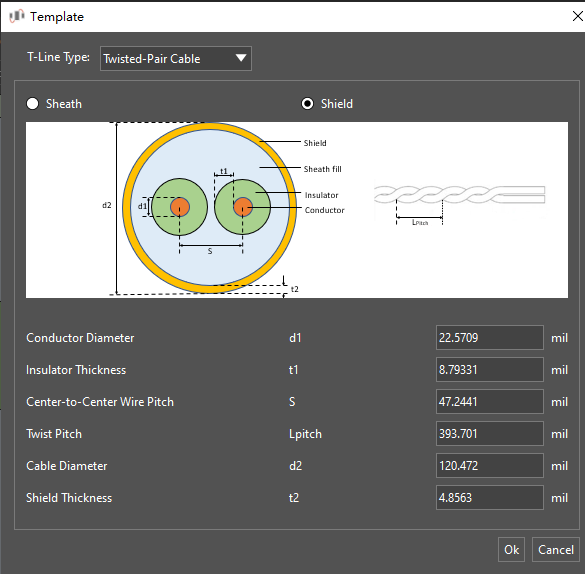

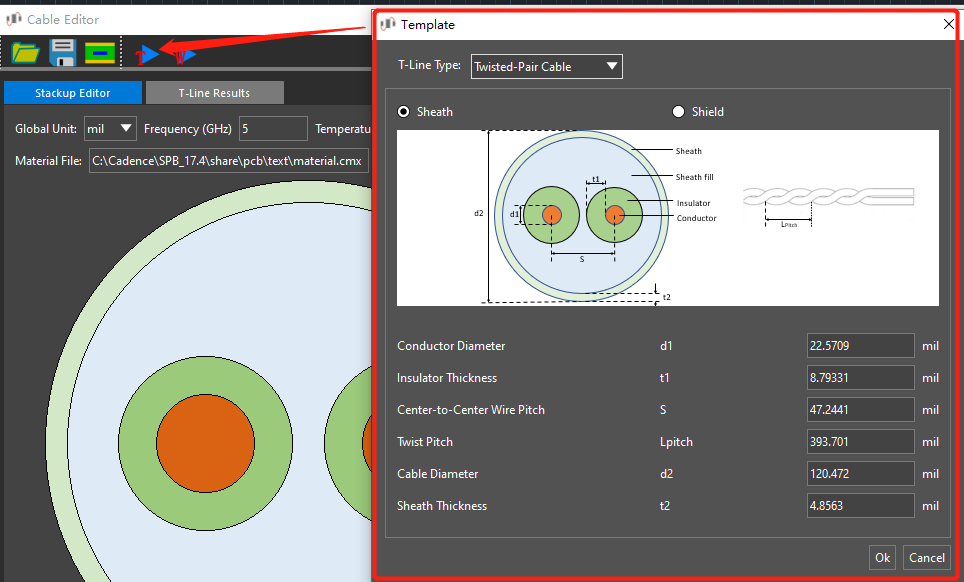

input for Template 是輸入電纜數(shù)據(jù)的模板文件。T-Line Type 是模型的類型設(shè)置,twisted pair cable 是我們常用的雙絞線模型。Sheath 是帶有保護(hù)層的雙絞線模型參數(shù)設(shè)置,Shield 是帶有屏蔽層的雙絞線模型參數(shù)設(shè)置。

3

從數(shù)據(jù)來(lái)看:

Conductor Diameter | 導(dǎo)體直徑 |

Insulator Thickness | 絕緣體厚度 |

Center-to-Center Wire Pitch | 中心到中心的導(dǎo)線間距 |

Twist Pitch | 電纜角線間距 |

Cable Diameter | 電纜的直徑 |

Sheath Thickness | 保護(hù)層的厚度 |

Shield Thickness | 屏蔽層的厚度 |

輸入數(shù)據(jù)完成以后,點(diǎn)擊 Calculate T-Line Parameters 命令查看數(shù)據(jù)。

4

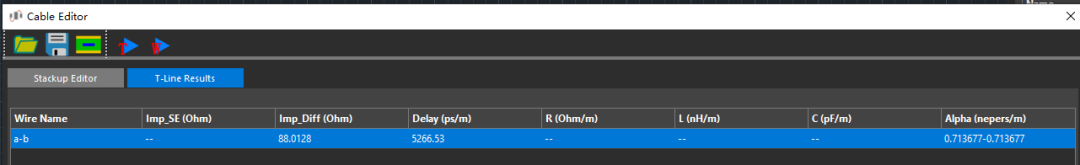

點(diǎn)擊 Calculate T-Line Parameters 命令會(huì)自動(dòng)轉(zhuǎn)到 T-Line Results 菜單顯示生成的參數(shù)列表。

5

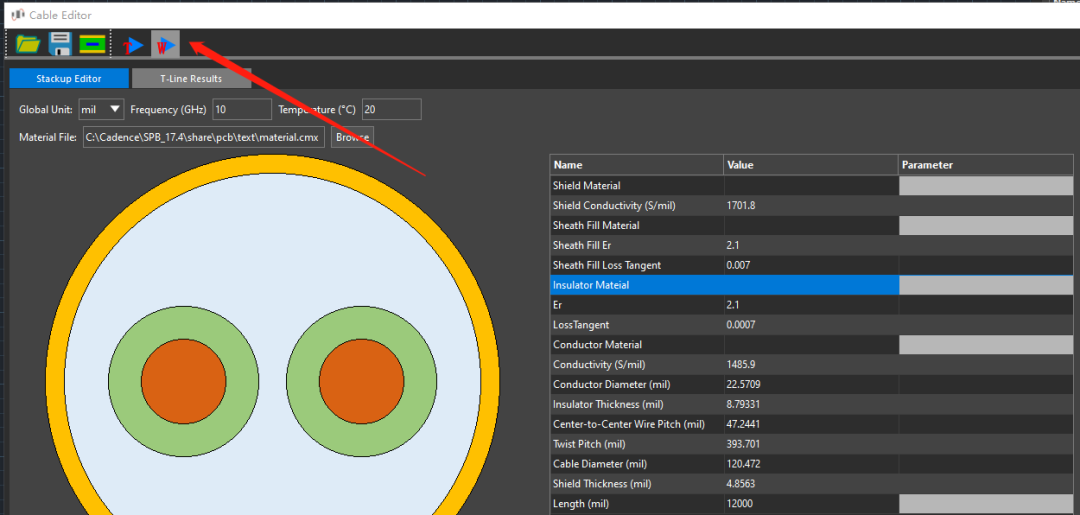

在 Stackup Editor 中可以修改層疊數(shù)據(jù),也可以設(shè)置頻率、溫度、電解常數(shù)、損耗、電導(dǎo)率及其他的電纜數(shù)據(jù)參數(shù)。

6

修改參數(shù)建模數(shù)據(jù)完成以后,點(diǎn)擊 Generate W-Element Model 可以針對(duì)修改參數(shù)后的電纜進(jìn)行模型的生成。

7

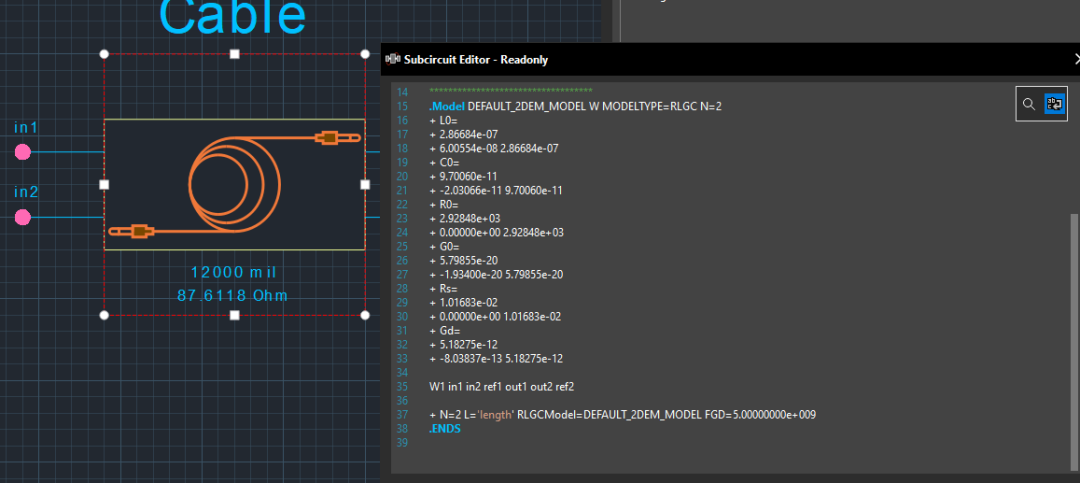

選擇 View Sub Circuit 菜單可以顯示建模后的模型參數(shù)和生成的模型數(shù)據(jù)。從模型數(shù)據(jù)可以看到電纜生成的是一個(gè) RLGC 的模型數(shù)據(jù)。

8

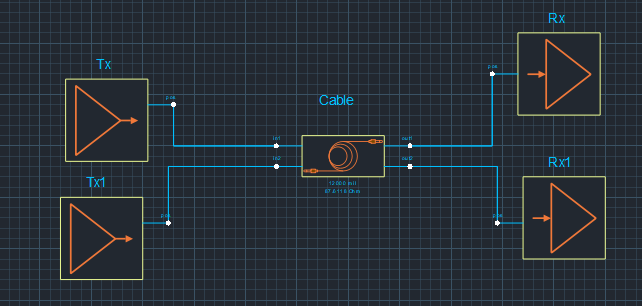

使用電纜模型,搭建信號(hào)的互連仿真鏈路模型。

9

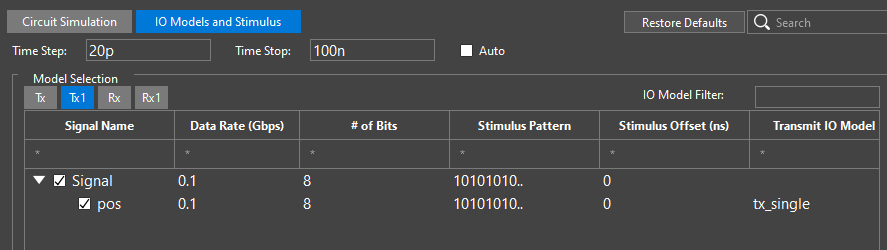

設(shè)置激勵(lì)的模型參數(shù)和波形數(shù)據(jù),信號(hào)的長(zhǎng)度和速度,進(jìn)行信號(hào)互連仿真分析仿真。

10

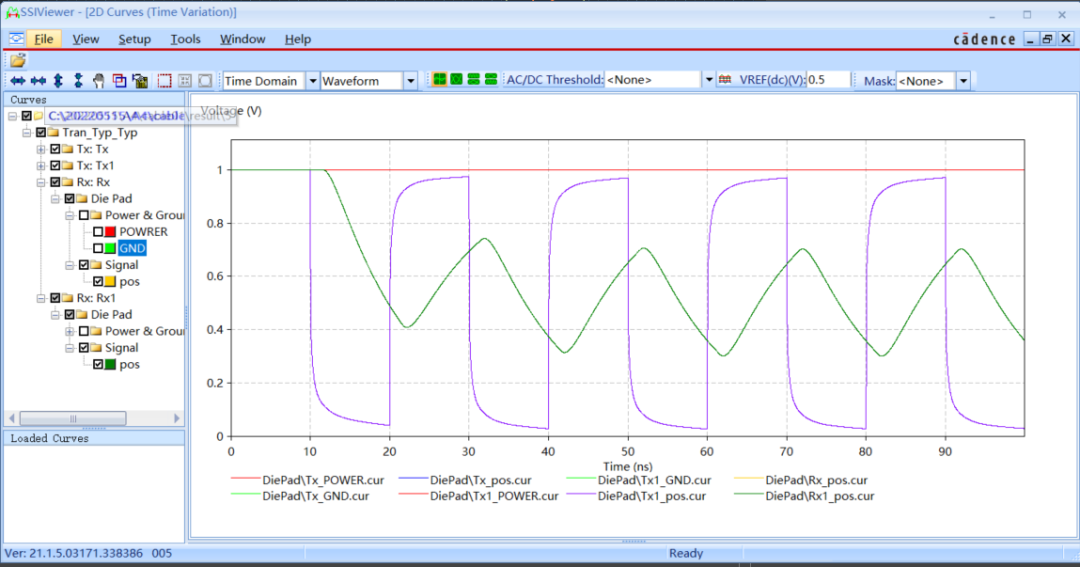

執(zhí)行仿真完成以后,就可以在 SSI Viewer 中看到使用電纜模型進(jìn)行仿真完成的波形結(jié)果。

-

仿真

+關(guān)注

關(guān)注

54文章

4487瀏覽量

138315

發(fā)布評(píng)論請(qǐng)先 登錄

TF-047 微同軸電纜:高密度應(yīng)用的理想之選

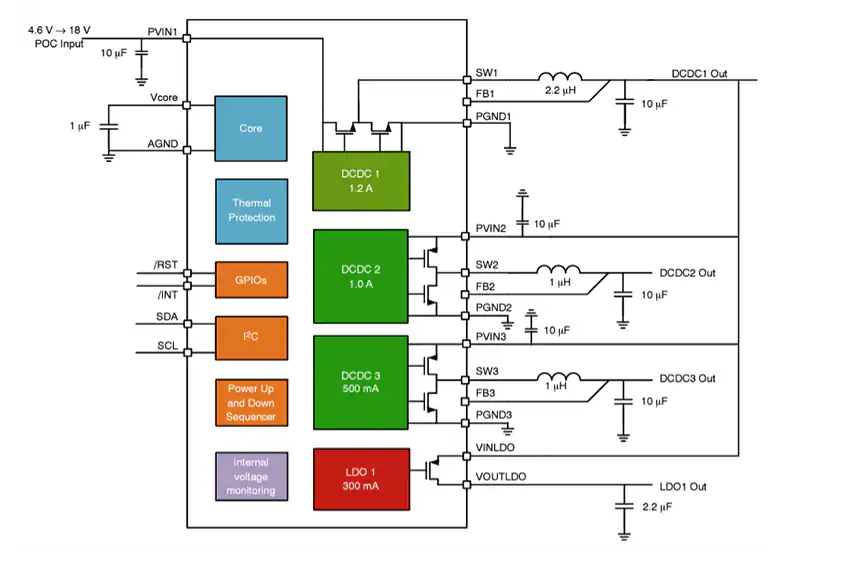

onsemi NCV92310汽車同軸電纜供電PMIC技術(shù)深度解析

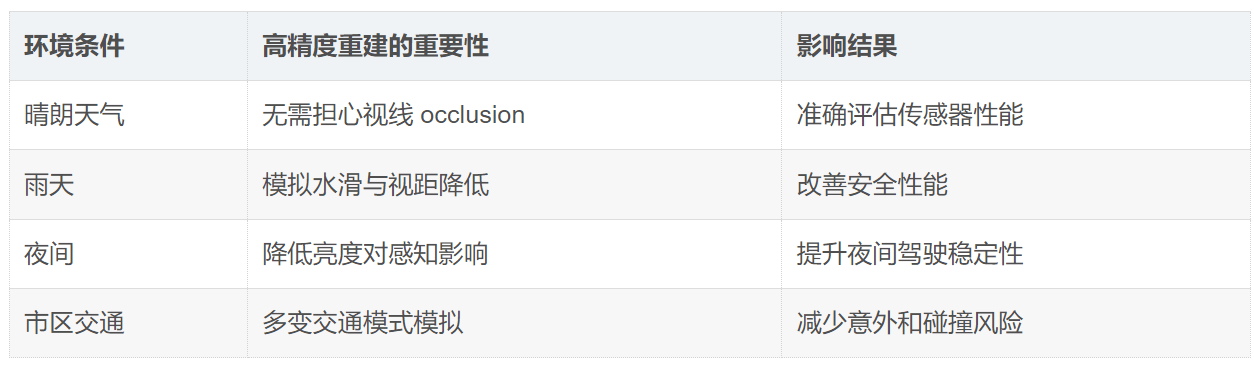

如何選擇適合的智駕仿真工具進(jìn)行場(chǎng)景生成和測(cè)試?

同軸電纜選型指南:從理論到實(shí)踐的綜合考量

Molex MLX同軸電纜技術(shù)解析與應(yīng)用指南

?U.FL同軸電纜組件技術(shù)解析與應(yīng)用指南

射頻同軸電纜的關(guān)鍵指標(biāo)說(shuō)明

雙絞線纜VS光纖VS同軸電纜——誰(shuí)才是網(wǎng)絡(luò)傳輸?shù)摹叭芡酢?/a>

MAX9275/MAX9279用于同軸電纜或STP輸出驅(qū)動(dòng)和并行輸入的3.12Gbps GMSL串行器技術(shù)手冊(cè)

MAX9277/MAX9281用于同軸電纜或STP輸出驅(qū)動(dòng)和LVDS輸入的3.12Gbps GMSL串行器技術(shù)手冊(cè)

MAX9278/MAX9282用于同軸電纜或STP輸入和LVDS輸出的3.12Gbps GMSL解串器技術(shù)手冊(cè)

MAX9288/MAX9290用于同軸或STP輸入和MIPI CSI-2輸出的3.12Gbps GMSL串行器技術(shù)手冊(cè)

MAX9272A用于同軸電纜或STP電纜的28位GMSL解串器技術(shù)手冊(cè)

MAX9240A用于同軸電纜或STP電纜的6.25MHz至100MHz、25位GMSL解串器技術(shù)手冊(cè)

精密校準(zhǔn):守護(hù)三同軸電纜測(cè)量精度的核心技術(shù)

2022 Sigrity Aurora SPB 17.4 版本更新 I 支持生成同軸電纜和雙絞線模型并進(jìn)行仿真

2022 Sigrity Aurora SPB 17.4 版本更新 I 支持生成同軸電纜和雙絞線模型并進(jìn)行仿真

評(píng)論