引言

在電路設(shè)計(jì)自動(dòng)化的時(shí)代,綜合工具的作用不言而喻,通過綜合,設(shè)計(jì)人員能夠獲得自己所設(shè)計(jì)模塊的規(guī)模、時(shí)序性能和關(guān)鍵路徑等有用信息,進(jìn)而指導(dǎo)自己優(yōu)化設(shè)計(jì)結(jié)構(gòu)。本文就來說說綜合工具DC工作的全流程,希望對設(shè)計(jì)人員和DC的初級使用者有所啟發(fā)。

DC (Design compiler) 是Synopsys 公司綜合核心工具,內(nèi)嵌六種工具:DC Explorer、HDL Compiler、Library Compiler 、Power Compiler,DFT Compiler and DFTMAX 和Design Vision,在綜合的不同階段DC調(diào)用相應(yīng)的工具實(shí)現(xiàn)所需的功能。DC包含以下功能技術(shù):DC Expert,DC Ultra 和DC Graphical。DC Expert 能夠進(jìn)行功耗、面積和時(shí)序的優(yōu)化,采用線性負(fù)載模型計(jì)算延時(shí);DC Ultra所采用的優(yōu)化算法也更先進(jìn),且DC Ultra提供拓計(jì)算技術(shù),即在拓?fù)淠J较虏徊捎镁€性負(fù)載模型而是采用Synopsys的布局優(yōu)化技術(shù),以保證綜合結(jié)果和最終物理設(shè)計(jì)更好的相關(guān)性;DC Graphical具有DC Expert和DC ultra 所有特性,并且能夠優(yōu)化multicorner-multimode 設(shè)計(jì)、減少布線擁堵和進(jìn)行初步floorplan。

DC Expert:啟動(dòng)命令dc_shell,綜合命令compile。

DC Ultra:拓?fù)淠J絾?dòng)命令dc_shell -topo,綜合命令complie_ultra。

DC Graphical:啟動(dòng)命令dc_shell -topo,綜合命令complie_ultra -spg。

Synopsys對綜合的定義十分形象Synthesis=Translation + Logic Optimization +Gate Mapping,這正好表示出使用DC綜合的過程,將RTL設(shè)計(jì)translate成GTECH門級網(wǎng)表,再根據(jù)施加的約束對電路優(yōu)化并向特定工藝庫映射。本文力求解釋清楚綜合過程,不涉及具體綜合腳本和施加約束方法。

DC是調(diào)用HDL Compiler來將讀取的設(shè)計(jì)轉(zhuǎn)換成不依賴于工藝的GTECH門級網(wǎng)表的。這里需要說明的是GTECH網(wǎng)表中不僅僅只有與非門、異或門這種門電路符號(hào),還有時(shí)序器件符號(hào)SEQGEN,如果設(shè)計(jì)中使用加、減、乘和比較等運(yùn)算,GTECH會(huì)將其提取出來并用以帶有OP標(biāo)識(shí)的符號(hào)表示,這方便后續(xù)進(jìn)行高級別電路優(yōu)化;另外,設(shè)計(jì)中避免不了使用選擇邏輯,如不特別聲明,DC在這一階段對選擇邏輯用SELECT_OP表示,且在后續(xù)的映射階段并不一定將SELECT_OP映射成多路選擇器,而是采用與非門電路來實(shí)現(xiàn)其功能,如果想要映射成多路選擇器,那么需要在RTL中聲明synopsys infer_mux。

接下來DC根據(jù)綜合人員設(shè)置的約束對GTECH網(wǎng)表進(jìn)行優(yōu)化,可分為組合優(yōu)化和時(shí)序優(yōu)化。

組合邏輯優(yōu)化是先對組合邏輯設(shè)計(jì)進(jìn)行工藝無關(guān)的邏輯級優(yōu)化,從GTECH門電路提取出布爾表達(dá)式集合,這樣可以對通過對布爾表達(dá)式的化簡和變形實(shí)現(xiàn)對電路結(jié)構(gòu)的化簡和變形;

再向工藝庫映射,映射的過程中根據(jù)速度和面積的目標(biāo)選擇適合的電路結(jié)構(gòu);

最后在對工藝依賴的門電路進(jìn)行門級優(yōu)化,這一階段DC主要進(jìn)行延時(shí)優(yōu)化、功耗優(yōu)化、DRC修正和面積優(yōu)化。

時(shí)序優(yōu)化分為兩步,第一步向工藝庫中的時(shí)序器件進(jìn)行映射,此時(shí)組合邏輯還沒有完成映射,也就沒有具體的延時(shí)信息,時(shí)序器件的選擇也不就不是最優(yōu)的,時(shí)序優(yōu)化是在映射后進(jìn)行的,且進(jìn)行時(shí)序器件替換時(shí)是將時(shí)序電路附近的組合邏輯一起考量的。

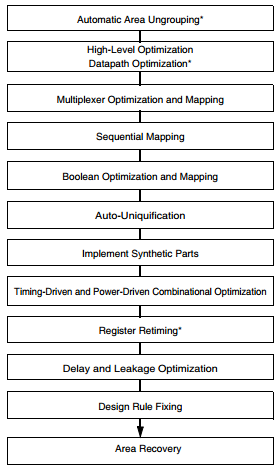

具體來說DC的優(yōu)化流程是如圖1所示的12步完成的,其中星號(hào)表示 DC Expert不支持。

1)如果使用compile_ ultra,默認(rèn)首先自動(dòng)進(jìn)行ungroup操作,ungroup操作會(huì)將設(shè)計(jì)展平,展平設(shè)計(jì)必然會(huì)對內(nèi)部信號(hào)重命名,這一操作會(huì)為后仿調(diào)試帶來困難,所以建議先關(guān)閉這一功能,首次綜合compile_ultra –no_auto_ungroup后,如果時(shí)序確實(shí)很緊張?jiān)俅蜷_這一功能,或者使用set_ungroup命令來實(shí)現(xiàn)局部ungroup操作。

2)high-level optimization是在時(shí)序和面積的約束下進(jìn)行的資源提取和共享。如果使用DC Ultra工具,那么還可以對 datapath進(jìn)行加減等運(yùn)算operator進(jìn)行提取優(yōu)化。

3)Multiplexer Mapping and Optimization,即將組合邏輯中多路選擇標(biāo)識(shí)首先映射成單個(gè)多路選擇器或者多路選擇樹,且為了能夠共享多路選擇樹、減少面積,DC會(huì)重新調(diào)整選擇信號(hào)的順序。

4)Sequential Mapping階段,DC將 SEQGEN代表的時(shí)序單元映射到 target Library中實(shí)際的時(shí)序器件。

5)Structuring and Mapping,即將設(shè)計(jì)中可以析出的子函數(shù)或者說子表達(dá)式作為中間變量,通過復(fù)用多次使用的中間變量可以減少面積,并將組合邏輯對工藝庫進(jìn)行映射。

6)Automatic uniquification,這個(gè)操作相當(dāng)于綜合人員使用了uniquify命令,該命令通過對多次例化的子設(shè)計(jì)進(jìn)行復(fù)制和重命名的方式,實(shí)現(xiàn)每一個(gè)instance都有唯一設(shè)計(jì)與之對應(yīng),從而解決同一子設(shè)計(jì)多次例化問題。

7)implementing Synthetic Parts,在高級別優(yōu)化階段,類似+或者*這樣的operator將其用一個(gè)抽象符號(hào)代表,稱為Synthetic Part,此時(shí)將這些 Synthetic Part映射為具體不同結(jié)構(gòu)的加法器或者乘法器等。

8)timing-driven combinational optimization,此步驟DC對關(guān)鍵路徑再次進(jìn)行重構(gòu),即增加總變量和復(fù)制中間變量等操作來提升速度,并且對關(guān)鍵路徑再次進(jìn)行operator的Implementing,比如將串行加法器替換為行波進(jìn)位加法器。

9)Register Retiming,該步驟僅DC Ultra支持,該操作簡單說就是對寄存器的移位、合并或者拆散復(fù)制等操作來減少違例。如果使用 optimize registers命令,那么寄存器的 retiming 更適合 pipelined designs;如果在 compile_ultra命令后帶- retime選項(xiàng),DC會(huì)自動(dòng)進(jìn)行局部 retiming操作,這更適合通用的non- pipeline design。

10)Delay and Leakage Optimization這一步驟,DC試圖修復(fù)延時(shí)違例,DC再次對關(guān)鍵路徑的電路結(jié)構(gòu)進(jìn)行評估,如果不滿足約束,那么再次進(jìn)行結(jié)構(gòu)選擇并進(jìn)行替換;至于leakage優(yōu)化,DC是將非關(guān)鍵路徑的庫單元替換為庫中l(wèi)eakage更低的單元,比如選擇庫中高閾值電壓單元。

11)Design Rule Fixing,DC 通過插入buffer或者 resize gate進(jìn)行設(shè)計(jì)規(guī)則違例修正。

12)Area Optimization,此過程DC 默認(rèn)是在不影響延時(shí)性能進(jìn)行的。如果使用DC Ultra工具,綜合人員可以使用 compile_ultra 命令后,再施加optimize_ netlist -area命令,在不影響時(shí)序性能的前提下進(jìn)一步提升面積優(yōu)化效果。

四、總結(jié)

另外,如果想要獲得更好的QoR,從RTL code中提取數(shù)據(jù)路徑塊是十分重要,設(shè)計(jì)人員可以在compile_ultra前使用analyze_datapath_extraction命令來查看設(shè)計(jì)中算術(shù)內(nèi)容并得到設(shè)計(jì)建議反饋。若想以html格式顯示報(bào)告,帶-html選項(xiàng)即可,HTML格式文件里面可以直接鏈接到RTL代碼,便于檢閱和修改。有時(shí)候觀測一下設(shè)計(jì)的最小面積和時(shí)序性能的極限很有意義,不加任何約束,compile_ultral會(huì)綜合出面積最小的情況;使用set_cost_priority -delay命令,將延時(shí)優(yōu)化的優(yōu)先級提前到DRC優(yōu)先級前,可觀測設(shè)計(jì)時(shí)序性能的極限。

審核編輯:湯梓紅

-

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6741文章

2700瀏覽量

219494 -

HDL

+關(guān)注

關(guān)注

8文章

332瀏覽量

48972 -

DC

+關(guān)注

關(guān)注

12文章

3692瀏覽量

686312 -

RTL

+關(guān)注

關(guān)注

1文章

394瀏覽量

62645 -

時(shí)序

+關(guān)注

關(guān)注

5文章

406瀏覽量

38853

原文標(biāo)題:一文讓你理解DC綜合全過程!

文章出處:【微信號(hào):芯司機(jī),微信公眾號(hào):芯司機(jī)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

幫忙分析下這個(gè)設(shè)計(jì)的工作流程

Simulink是什么?Simulink的工作流程是怎樣進(jìn)行的?

測試工程師工作流程有哪些

英特爾圖形性能分析器(GPA)的Windows DirectX工作流程分析

KiCad的工作流程解析

如何將機(jī)械設(shè)計(jì)工作流程集成到電氣設(shè)計(jì)工具中?

工作流程圖怎么用?有哪些繪制工作流程圖的軟件

淺談無刷電機(jī)的工作流程

NX CAD軟件:數(shù)字化工作流程解決方案(CAD工作流程)

淺談DC綜合工具的工作流程

淺談DC綜合工具的工作流程

評論