大俠好,歡迎來到FPGA技術江湖。本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有系統性學習的機會。

系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。后續會陸續更新 Xilinx 的 Vivado、ISE 及相關操作軟件的開發的相關內容,學習FPGA設計方法及設計思想的同時,實操結合各類操作軟件,會讓你在技術學習道路上無比的順暢,告別技術學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰應用,這種快樂試試你就會懂的。話不多說,上貨。

多路選擇器設計

多路選擇器是數據選擇器的別稱。在多路數據傳送過程中,能夠根據需要將其中任意一路選出來的電路,叫做數據選擇器,也稱多路選擇器或多路開關。

二選一多路選擇器

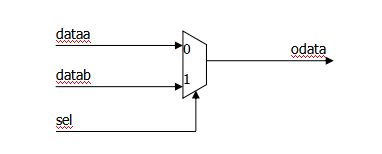

二選一多路選擇器的數據輸入有兩個,分別為dataa和datab。為了能夠確定選擇那一路數據能夠通過,還需要一個選擇端(sel)。因為輸入只有兩路數據,選擇端只要能夠表現出兩種狀態即可,因而選擇端位寬為1即可。

假設dataa和datab都是位寬為1的數據,當sel為0時,選擇dataa通過;當sel為1時,選擇datab通過;odata表示通過后的數據。

圖1 :二選一多路選擇器模型

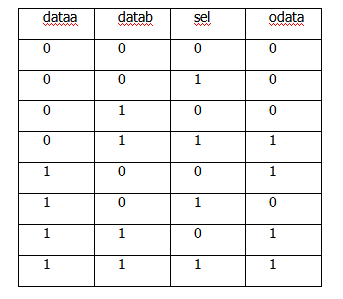

根據上述功能,列出真值表。

圖2 :二選一多路選擇器真值表

根據真值表,化簡得出布爾表達式:

odata = (dataa &(~sel)) | (datab & sel);

在verilog中,算術運算中,“&”表示算術(按位)與,“|”表示算術(按位)或,“~”表示算術(按位)取反。

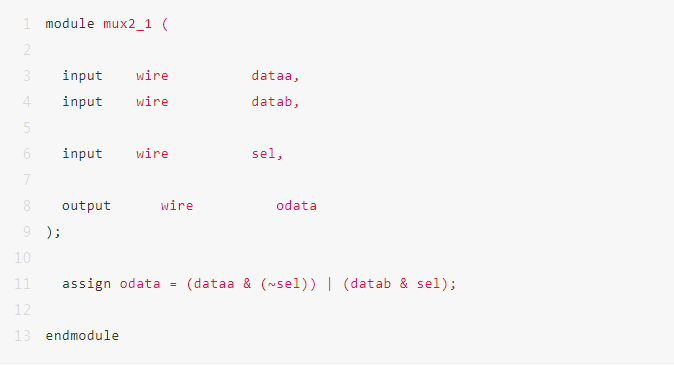

在數字電路基礎中,根據表達式,就可以得到電路圖。

現在我們要在FPGA中實現,二選一多路選擇命名為“mux2_1”,不要命名為mux21,mux21是quartus中默認器件庫中的名字,命名相同會出現錯誤。

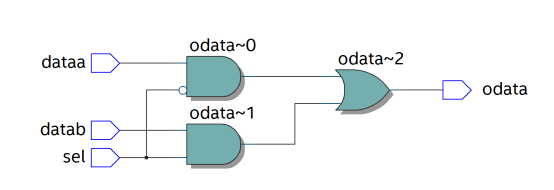

建立工程后,輸入如下設計代碼:(mux2_1代碼)

圖4 :mux2_1的RTL視圖

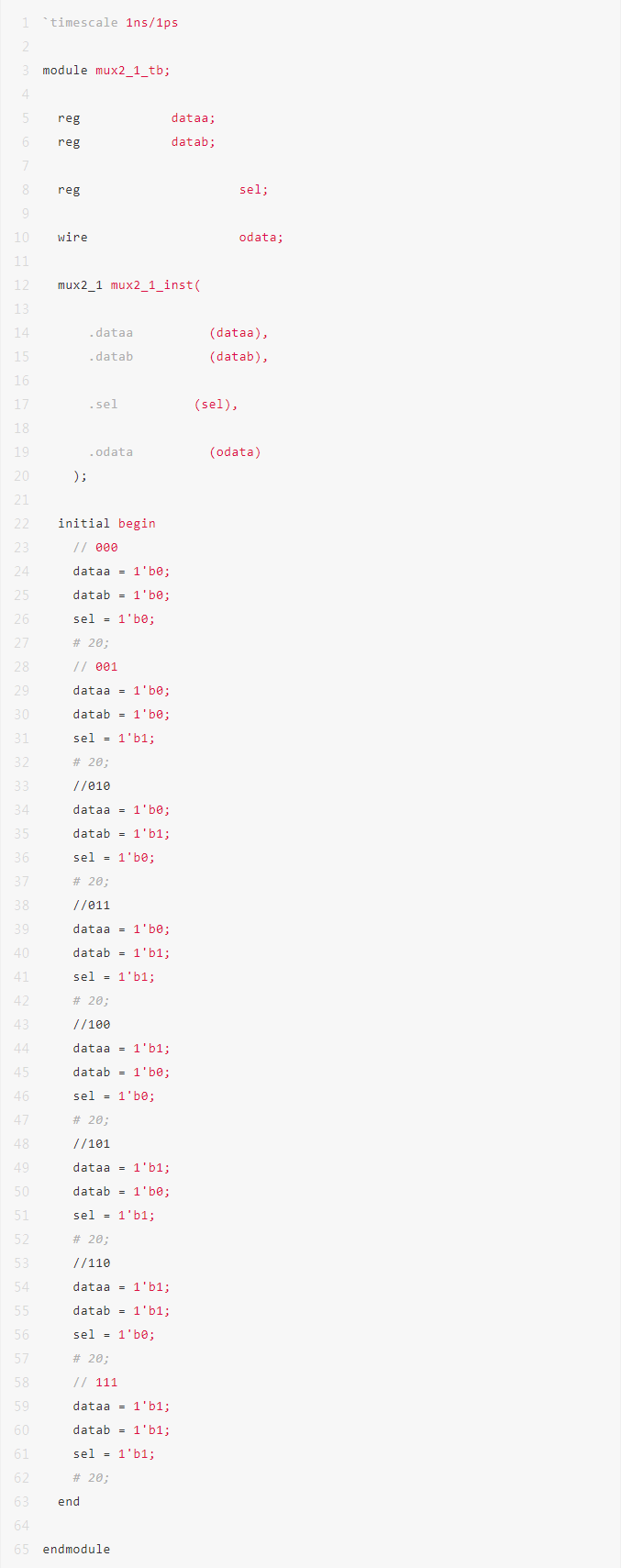

設計完成后,輸入如下testbench代碼:(mux2_1_tb代碼)

在verilog中,“//”表示本行被注釋,綜合器綜合時,自動略過。

在testbench中,連接線的名字可以隨意定義,建議和端口相同。

設置好testbench后,運行RTL 仿真。

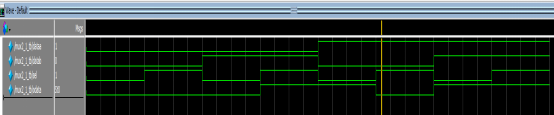

圖6 :RTL仿真波形

對比波形和真值表,設計正確。

四選一多路選擇器

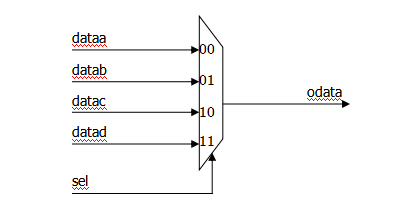

四選一多路選擇器的數據輸入有四個,分別為dataa、datab、datac和datad。為了能夠確定選擇那一路數據能夠通過,還需要一個選擇端(sel)。因為輸入四路數據,選擇端要求能夠表現出四種狀態,因而選擇端位寬為2。

假設dataa、 datab、datac和datad都是位寬為8的數據,當sel為00時,選擇dataa通過;當sel為01時,選擇datab通過;當sel為10時,選擇datac通過;當sel為11時,選擇datad通過;odata表示通過后的數據。

圖7 :四選一多路選擇器模型

根據組合邏輯設計規則,我們將所有的情況全部列出,得出真值表,進而得到布爾表達式。但是現在輸入的組合排列太多了(2的34次冪),不能夠直接得出真值表。

此時的設計有兩種方法。

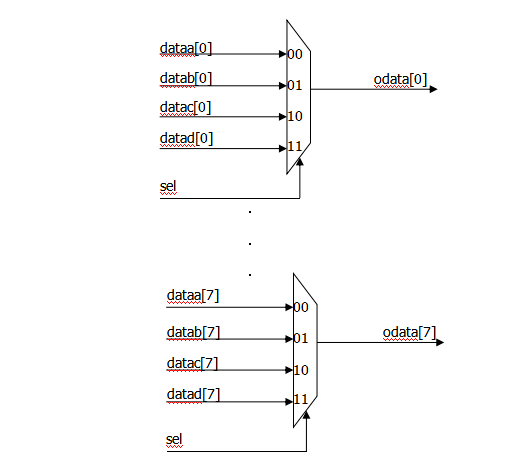

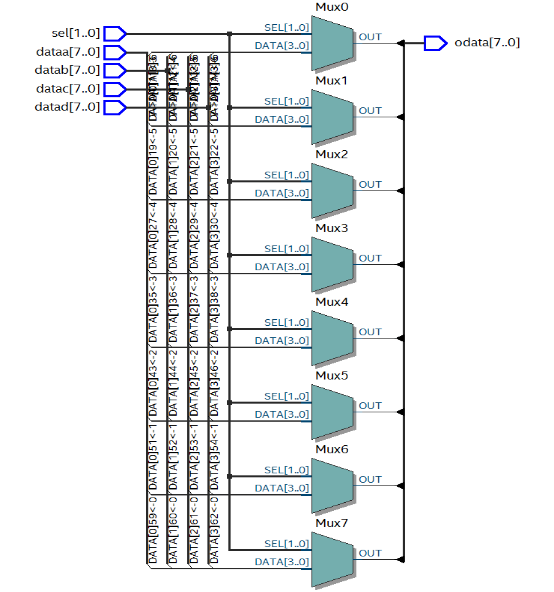

第一種方法,根據功能拆分邏輯。將輸入為8的四選一多路選擇器,拆分為8個位寬為1的四選一多路選擇器,首先列出位寬為1真值表,得出位寬為1的四選一多路選擇器。然后并接八個即可。

圖8 :8個位寬1多路選擇器構成位寬8的多路選擇器

這種設計方法,不在提供設計源碼,讀者可以自行討論設計。

第二種方法,根據verilog的設計規則,可以直接描述邏輯功能,而不用描述門電路。這種設計規則有利于將設計做的比較大。

位寬為8的四選一多路選擇器命名為“mux4_1”。

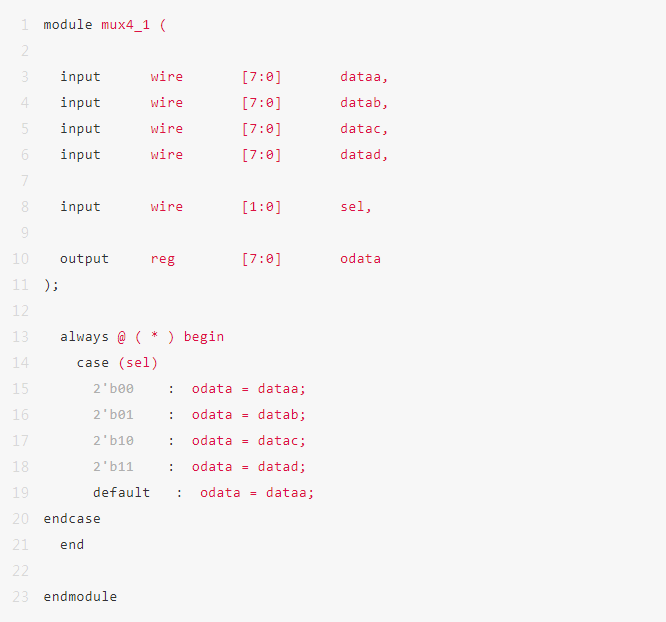

建立工程后,輸入設計代碼如下:(mux4_1代碼)

always 語句用來表示組合邏輯時,即可以采用門電路的描述方法,也可以采用功能性的描述語句。

“always @()”中()是信號敏感列表。中間可以寫入本模塊的所有的敏感信號,“*”可以表示所有的敏感信號。建議利用always語句描述組合邏輯時,用“*”表示所有信號。用“*”時,“()”可以省略。即:always@(*) 等效 always@*。

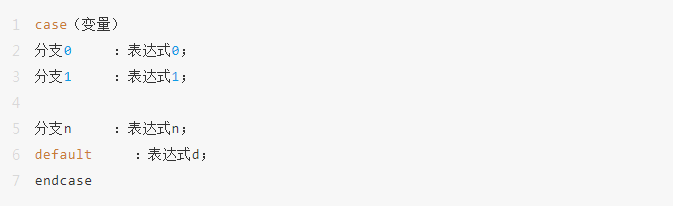

在case語句中,首先會判斷變量和那個分支相同,并且執行對應的表達式。當和所有的分支都不相同時,執行default后的表達式。

verilog規定,在always語句中被賦值的變量,應該定義為“reg”類型。

圖11 :mux4_1的RTL視圖

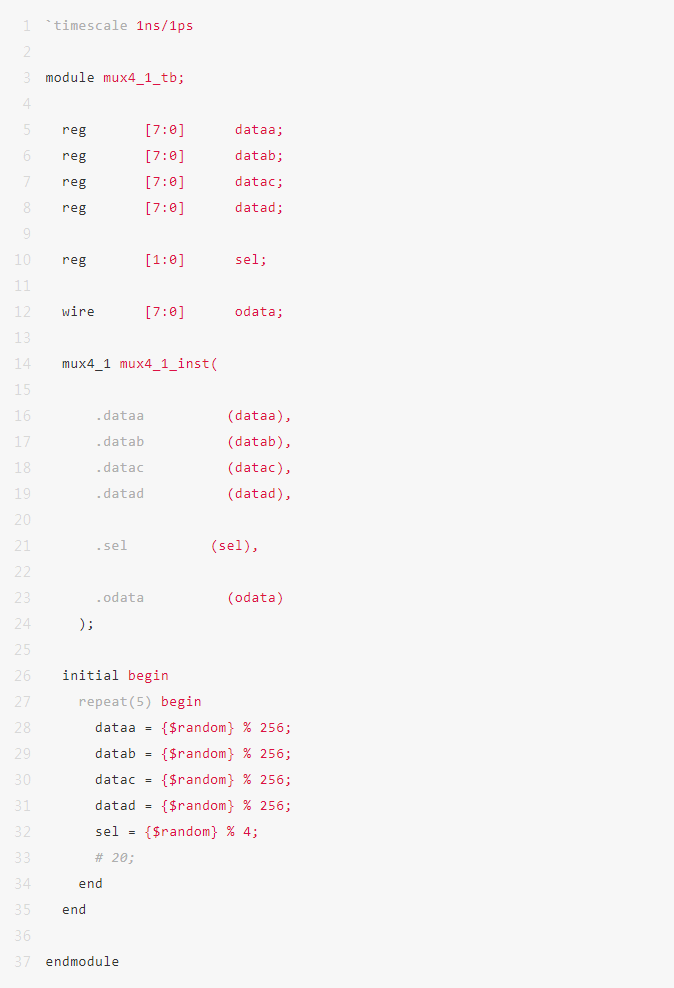

設計完成后,輸入testbench代碼。mux4_1_tb 代碼如下:

由于本次輸入的的組合太多,不能全覆蓋測試。故采用隨機數來進行測試。

$random是一個系統函數,調用時,可以返回一個隨機值。注意:這個系統函數只能出現testbench中,在設計中出現是不可綜合的。

“$random函數調用時返回一個32位的隨機數,它是一個帶符號的整形數...”。例:

reg[23:0] rand;

rand=$random % 60; //產生一個在 -59—59范圍的隨機數

產生0~59之間的隨機數,例:

reg[23:0] rand;

rand={$random} % 60; //通過{}產生0—59范圍的隨機數

產生在min, max之間隨機數,例:

reg[23:0] rand;

rand = min+{$random}%(max-min+1);

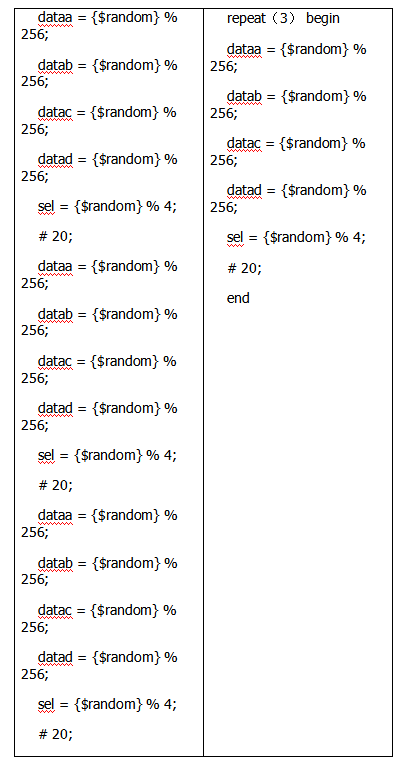

在testbench中,需要按照一定順序給輸入線賦值。在mux4_1_tb中,我們可以通過延遲賦值,然后再次延遲賦值,來完成賦值。因為賦值時采用隨機數,所以每次編寫的語句是相同的。verilog中提供了repeat語句,用來減少人工輸入。

圖13 :兩種等效的賦值方式

輸入testbench后,進行綜合分析。

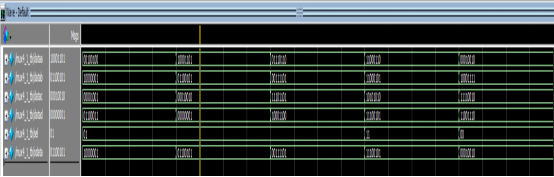

設置testbench,運行RTL仿真。

圖14:RTL仿真圖

經過分析,符合四選一多路選擇器的設計。

更多熱點文章閱讀

-

電子技術

+關注

關注

19文章

930瀏覽量

60036 -

電子發燒友論壇

+關注

關注

5文章

198瀏覽量

1665

原文標題:【教程分享】零基礎學習:基于FPGA的多路選擇器設計(附代碼)

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發燒友論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【教程分享】零基礎學習:基于FPGA的多路選擇器設計(附代碼)

【教程分享】零基礎學習:基于FPGA的多路選擇器設計(附代碼)

評論