高速先生成員:黃剛

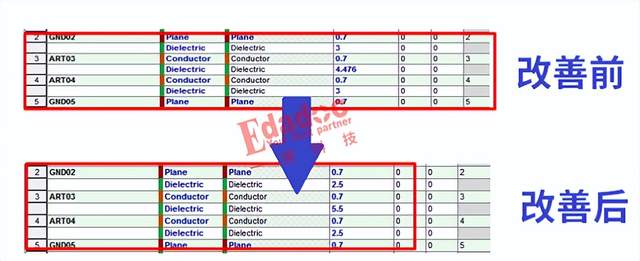

就在剛剛,雷豹把他對(duì)疊層的調(diào)整方式和改善后的仿真結(jié)果給師傅Chris看完后,Chris給雷豹點(diǎn)了個(gè)大大的贊,因?yàn)閮?yōu)化的方式其實(shí)不需要大改DDR的走線,只需要把相鄰層的信號(hào)最大限度的拉開(kāi),同時(shí)為了保證疊層厚度不變,就需要把信號(hào)和參考的地平面相應(yīng)的靠近。這個(gè)操作的好處是顯而易見(jiàn),信號(hào)與信號(hào)之間的距離變遠(yuǎn)的同時(shí),信號(hào)與參考地平面的距離又變近了,串?dāng)_肯定就能夠改善了啊!下面是雷豹想到的改善后的疊層方案。

信號(hào)與信號(hào)由之前的4.476mil拉大到了5.5mil,同時(shí)為了保持厚度不變,信號(hào)與地的距離從3mil減小到了2.5mil。這個(gè)時(shí)候會(huì)不會(huì)有粉絲問(wèn),為什么不再拉大一點(diǎn)呢,直接拉到6mil以上不更好了。呃,這個(gè)……只能回答你們,PCB設(shè)計(jì)是需要多種因素來(lái)權(quán)衡,拉到6mil的串?dāng)_肯定會(huì)更好,但是信號(hào)離地平面近了,線寬需要減小才能控到之前的阻抗,近到2mil壓根就控不到阻抗了,因?yàn)榫€忒細(xì)了。

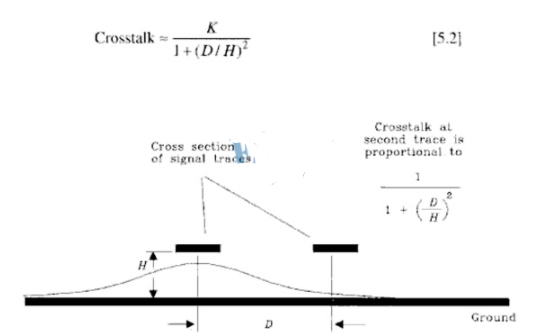

其實(shí)雷豹坦言,采取這個(gè)疊層調(diào)整的方案其實(shí)也主要是通過(guò)“憑感覺(jué)”來(lái)的,理論是知道的,就是信號(hào)之間遠(yuǎn)了,信號(hào)和地平面近了,電磁場(chǎng)在信號(hào)之間的交叉量就少了,因此串?dāng)_能夠改善。但是改善了多少,能不能通過(guò)其他指標(biāo)更清晰的量化出來(lái)呢,雷豹心里其實(shí)是打鼓的!

Chris看破不點(diǎn)破,決定親自來(lái)接手這個(gè)案例后續(xù)的串?dāng)_分析。我們知道,去衡量任何信號(hào)質(zhì)量的手段無(wú)非就兩種,要么是在時(shí)域上判斷,要么就是在頻域上去分析。時(shí)域的話,雷豹已經(jīng)在信號(hào)眼圖上有對(duì)比過(guò)了,那么想繼續(xù)分析這個(gè)串?dāng)_的改善的話,就有在頻域上去做文章了。

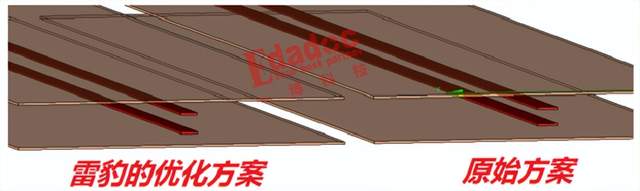

Chris對(duì)雷豹調(diào)整疊層前后的走線結(jié)構(gòu)進(jìn)行建模,利用cadence的3D clarity快速的建立了兩種結(jié)構(gòu)的模型,可以看到,雷豹的優(yōu)化方案就是把信號(hào)間距拉遠(yuǎn),信號(hào)與地間距拉近,同時(shí)減小一定的線寬來(lái)控制阻抗不變。

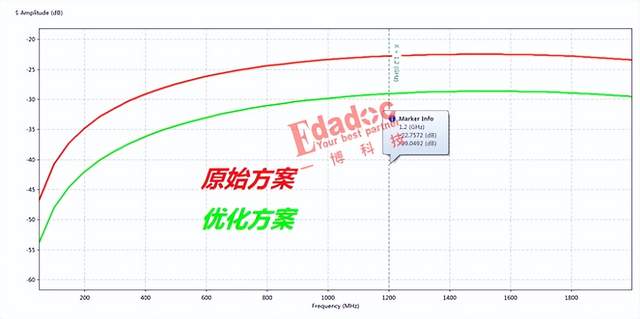

原始仿真模型版本中,我們把相鄰層的走線長(zhǎng)度定在1000mil,基本上和該案例的DDR走線的最大并行長(zhǎng)度接近,使得這個(gè)仿真模型更貼近該案例的真實(shí)情況。

分別對(duì)兩個(gè)模型進(jìn)行仿真,仿真后得到兩者的串?dāng)_參數(shù)的結(jié)果,Chris把它們擺在一起來(lái)看。

從對(duì)比結(jié)果可以看到,串?dāng)_在DDR運(yùn)行的頻率處從22db改善到29db,大家可不要小看這個(gè)7db的串?dāng)_改善,從db損耗反推回幅度的話,如果串?dāng)_源電壓是1V的話,基本上22db是80mV的串?dāng)_幅度,29db只有35mV左右,改善還是非常的大的,有興趣的粉絲后面可以自己算算哈!

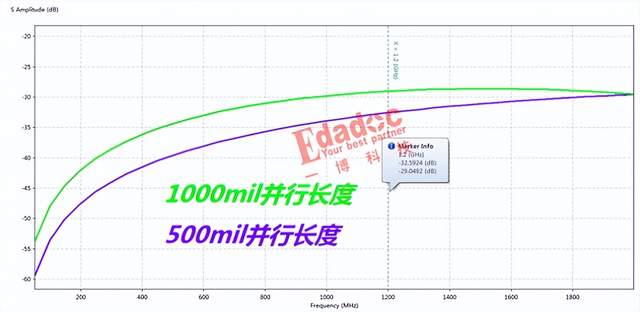

當(dāng)然,在雷豹驚呼很厲害的時(shí)候,Chris突然問(wèn)雷豹,那優(yōu)化了疊層之后,還有沒(méi)有什么辦法通過(guò)走線的變化進(jìn)一步優(yōu)化串?dāng)_呢?此時(shí)雷豹看著Chris的仿真模型,同時(shí)腦中不停的翻滾曾經(jīng)學(xué)過(guò)的串?dāng)_理論,duang的一聲,有啦!目前仿真模型是信號(hào)線并行長(zhǎng)度1000mil,如果能縮短到500mil呢,會(huì)不會(huì)使得串?dāng)_結(jié)果進(jìn)一步變好呢?Chris滿意的點(diǎn)了點(diǎn)頭,進(jìn)步很大的小伙子!只見(jiàn)Chris飛快的對(duì)模型上的信號(hào)走線縮短一半,只剩500mil的并行長(zhǎng)度,然后再次進(jìn)行仿真,結(jié)果令人滿意,串?dāng)_量級(jí)又改善了3個(gè)多db!

的確,從串?dāng)_產(chǎn)生的理論出發(fā)去尋找改善串?dāng)_的方案,的確是比較好的解決問(wèn)題的思路,于是雷豹在之前的疊層優(yōu)化建議之外,還加上了一條,盡量減小相鄰層并行的走線的長(zhǎng)度,這下這個(gè)案例的改板設(shè)計(jì)就更保險(xiǎn)了!正當(dāng)雷豹開(kāi)始暗爽的時(shí)候,突然Chris來(lái)了一句,那在這個(gè)case里,主控和DDR的布局位置都不變的時(shí)候,具體要怎么走線才能達(dá)到縮短并行長(zhǎng)度的目標(biāo)呢?雷豹?jiǎng)傞_(kāi)始楞了下,不過(guò)鎮(zhèn)定下來(lái)思考片刻后,作為PCB設(shè)計(jì)出身然后轉(zhuǎn)到我們高速先生團(tuán)隊(duì)的他還是想到了不少的辦法實(shí)現(xiàn)了!

審核編輯:湯梓紅

-

電路板

+關(guān)注

關(guān)注

140文章

5317瀏覽量

108173 -

DDR

+關(guān)注

關(guān)注

11文章

754瀏覽量

69125 -

信號(hào)

+關(guān)注

關(guān)注

12文章

2914瀏覽量

80138 -

串?dāng)_

+關(guān)注

關(guān)注

4文章

196瀏覽量

27837 -

PCB

+關(guān)注

關(guān)注

1文章

2308瀏覽量

13204

發(fā)布評(píng)論請(qǐng)先 登錄

常見(jiàn)信號(hào)完整性的問(wèn)題之PCB設(shè)計(jì)串擾的原因與Altium Designer中的串擾消除技術(shù)

信號(hào)的串擾介紹

PCB設(shè)計(jì)與串擾-真實(shí)世界的串擾(上)

基于高速PCB串擾分析及其最小化

串擾溯源是什么?

幾張圖讓你輕松理解DDR的串擾

“一秒”讀懂串擾對(duì)信號(hào)傳輸時(shí)延的影響

DDR跑不到速率,調(diào)整下PCB疊層就搞掂了?

DDR跑不到速率后續(xù)來(lái)了,相鄰層串擾深度分析!

pcb設(shè)計(jì)中的串擾—兩傳輸線相鄰太近

淺談層疊設(shè)計(jì)、同層串擾、層間串擾

如何解決EMC設(shè)計(jì)中的串擾問(wèn)題?

高速差分過(guò)孔間的串擾 差分過(guò)孔間串擾的仿真分析

嵌入式開(kāi)發(fā)中引起串擾的原因是什么?

DDR跑不到速率后續(xù)來(lái)了,相鄰層串?dāng)_深度分析!

DDR跑不到速率后續(xù)來(lái)了,相鄰層串?dāng)_深度分析!

評(píng)論