我用一個或多或少完整的NVMe VIP測試用例示例結(jié)束了我的上一篇博客文章,試圖展示從基本設(shè)置到執(zhí)行NVM寫入然后讀取的所有內(nèi)容。我們將在這里稍微改變一下,從 NVMe 命令轉(zhuǎn)移到一些可用于協(xié)助您測試的 VIP 功能。

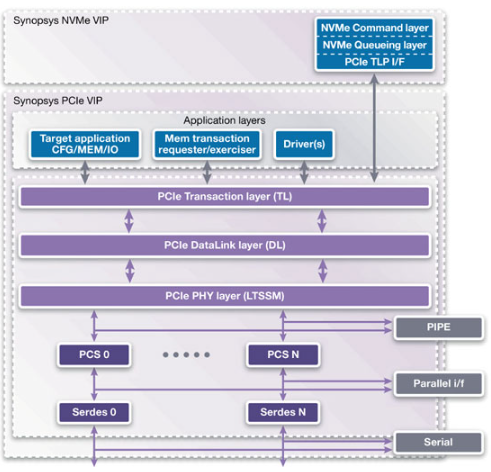

在這里,您可以了解有關(guān)適用于 NVMe 和 PCIe 的 Synopsys VC 驗證 IP 的更多信息。

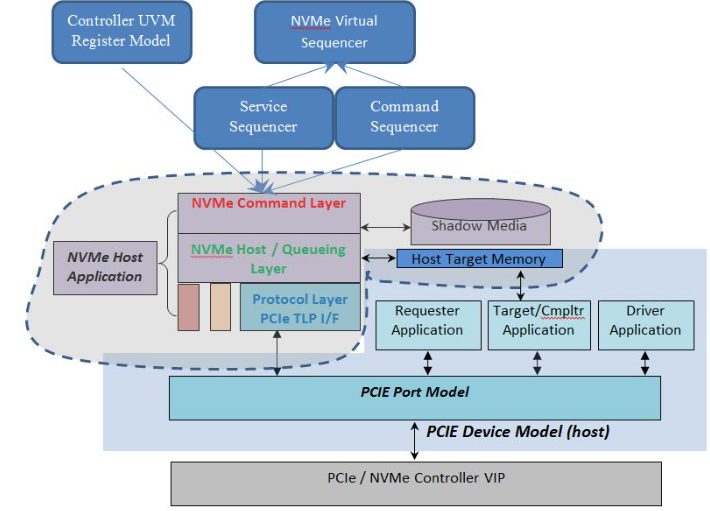

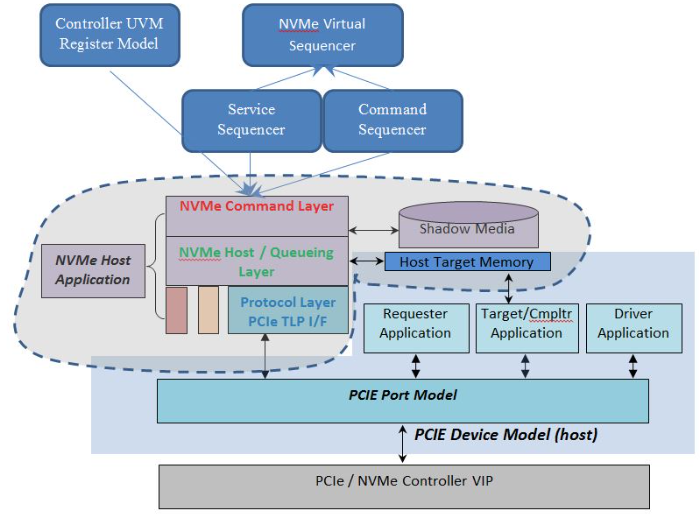

為了讓您保持新鮮感,我們將繼續(xù)參考此圖:

如前所述,NVMe VIP 提供了一組豐富的功能來幫助測試。

后臺流量

您將在上圖中注意到位于 PCIE 端口模型(請求者、目標(biāo)/cmpltr 和驅(qū)動程序)之上的幾個應(yīng)用程序。這些是可用于源(和接收)PCIe 流量(不是專門進出 NVMe)的 PCIe 應(yīng)用程序。特別:

驅(qū)動程序應(yīng)用程序 – 如果您想生成各種類型的TLP(例如CfgWr,IORd,MemWr),此應(yīng)用程序就是您的工具。TLP 的各個字段是可配置的,并且會檢查收到的完成(例如來自 MemRd 請求)的有效性和正確的數(shù)據(jù)。您還可以根據(jù)需要使用此工具配置或監(jiān)控 DUT。

目標(biāo)/完成者應(yīng)用程序 – 如果遠(yuǎn)程端點(例如控制器 DUT)將(非 NVMe)流量發(fā)送到此主機 VIP,Target 應(yīng)用程序?qū)?zhí)行該請求,將其轉(zhuǎn)過來并生成一個或多個(根據(jù)需要和/或配置)完成操作返回到端點。提供定時和數(shù)據(jù)包大小控制,以及用于詳細(xì) TLP 修改的多個回調(diào)。

請求者申請 – 此應(yīng)用程序會向目標(biāo)生成恒定的 TLP 負(fù)載。它可用于創(chuàng)建后臺流量,或在目標(biāo)上造成負(fù)載。流量速率、大小和類型都是可配置的。

錯誤注入

VIP 的一個重要且有用的功能是內(nèi)置錯誤注入。NVMe VIP 提供了一種簡單但非常強大的機制來導(dǎo)致錯誤注入,而不必使用回調(diào)和定向測試來導(dǎo)致錯誤。對于每個“腳本...”用戶可用的任務(wù)(有關(guān)詳細(xì)信息,請參閱以前的帖子),有一個“錯誤注入”參數(shù)。可以使用各種參數(shù)填充此參數(shù),以導(dǎo)致該 NVMe 命令發(fā)生特定的錯誤注入。對命令有效的特定錯誤注入由潛在錯誤條件控制(根據(jù) NVMe 規(guī)范)。

例如,檢查“創(chuàng)建 I/O 提交隊列”命令的規(guī)范會向我們顯示該命令可能導(dǎo)致的幾個錯誤,例如“完成隊列無效”、“隊列標(biāo)識符無效”和“超出最大隊列大小”。您只需要提供類似的錯誤注入代碼,然后會發(fā)生以下幾件事,而不是創(chuàng)建定向測試來導(dǎo)致這些情況:

VIP 將查找要生成的導(dǎo)致錯誤的相應(yīng)值。

這些值將被放置在適當(dāng)?shù)臄?shù)據(jù)結(jié)構(gòu)中(例如提交隊列條目)。

收到錯誤后,我們會自動禁止顯示可能以其他方式引起的任何警告(畢竟這是一個錯誤)。

如果預(yù)期的錯誤沒有到達,它將被標(biāo)記。

然后,系統(tǒng)已準(zhǔn)備好(如果需要)在沒有錯誤注入的情況下重新運行命令。

用戶無需進一步工作來測試錯誤 – 無需設(shè)置回調(diào),無需抑制錯誤。一切都處理得干凈透明。

除了 NVMe 層的注入錯誤之外,您還可以提供協(xié)議錯誤注入。例如,要在 PCIe DL 層導(dǎo)致 LCRC 錯誤,使用相同的過程:只需為該 LCRC 添加錯誤注入?yún)?shù),它就會發(fā)生,檢查、重試并重新檢查事務(wù)。所有這些都是在沒有任何用戶幫助的情況下發(fā)生的。

隊列圍欄

在主機內(nèi)存中創(chuàng)建隊列時,控制器可能會生成錯誤的內(nèi)存請求,并可能非法訪問隊列。這些訪問由主機的隊列屏蔽機制捕獲和標(biāo)記。主機了解哪些操作(即讀取或?qū)懭耄┮约澳男┑刂穼刂破髟L問有效,并將警惕地監(jiān)視控制器的訪問,以確保它不會嘗試(例如)從完成隊列讀取或?qū)懭胩峤魂犃小j犃泻完犃袟l目邊界的有效性同樣檢查。

卷影磁盤

主機 VIP 內(nèi)置的是一個卷影磁盤,用于跟蹤和記錄對各種控制器命名空間的塊數(shù)據(jù)寫入。一旦發(fā)生有效的寫入,它就會提交到影子,以后的讀取訪問將與影子數(shù)據(jù)進行比較。盡管VIP用戶肯定擁有可用的實際讀/寫數(shù)據(jù),但他們無需進行數(shù)據(jù)比較/檢查 - NVMe主機VIP會以靜默和自動的方式處理此問題。

控制器配置跟蹤

與卷影磁盤類似,主機還跟蹤連接到系統(tǒng)的控制器的配置。這有幾部分:

寄存器跟蹤 – 當(dāng)控制器 NVMe 寄存器被寫入時,主機會“窺探”此寫入,并將其存儲在本地“寄存器影子”中。VIP 的進一步操作可以參考此內(nèi)容,以確保操作對于控制器的當(dāng)前狀態(tài)有效和/或合理。

識別跟蹤 – 正如我們在示例中(在最近幾集中)中看到的那樣,NVMe 協(xié)議讓我們同時執(zhí)行“識別控制器”和“識別命名空間”命令來收集控制器信息。這些信息的相關(guān)部分也會保存以供VIP使用。

特征跟蹤 – “設(shè)置功能”命令用于配置控制器的各種元素——我們監(jiān)視并收集“設(shè)置”和“獲取功能”命令信息(根據(jù)需要),以完成主機VIP對控制器當(dāng)前配置和狀態(tài)的理解。

審核編輯:郭婷

-

控制器

+關(guān)注

關(guān)注

114文章

17791瀏覽量

193175 -

寄存器

+關(guān)注

關(guān)注

31文章

5608瀏覽量

129991 -

nvme

+關(guān)注

關(guān)注

0文章

299瀏覽量

23842

發(fā)布評論請先 登錄

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計18:UVM驗證平臺

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計23:UVM驗證平臺

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計33:初始化功能驗證與分析

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計34:初始化功能驗證與分析2

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計37:隊列管理功能驗證與分析1

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計40:隊列管理功能驗證與分析4

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計42:DMA 讀寫功能驗證與分析

如何使用Xilinx AXI VIP對自己的設(shè)計搭建仿真驗證環(huán)境的方法

Cadence推出15種新驗證 IP(VIP)解決方案

使用AXI VIP的幾個關(guān)鍵步驟及常見功能

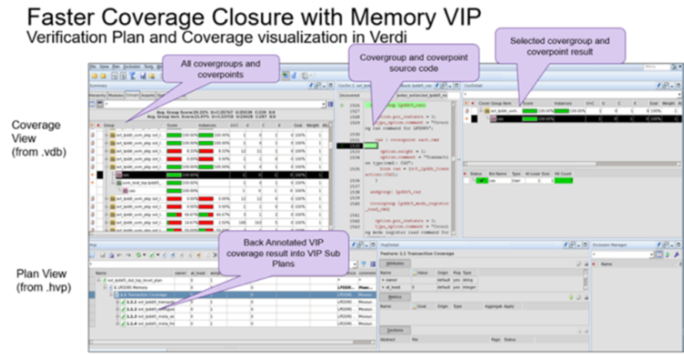

覆蓋模型 – 填補內(nèi)存VIP的漏洞

NVMe VIP架構(gòu):主機功能

新思科技NVMe VIP:高層次視圖

新思科技PCIe 7.0驗證IP(VIP)的特性

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計23:UVM驗證平臺

NVMe VIP:驗證功能

NVMe VIP:驗證功能

評論