FPGA 即 Field Programmable Gate Arrays,現場可編程門陣列。如果邏輯代數為數字世界的理論指導,那么邏輯門電路就是蓋起座座數字大廈的基本塊塊磚瓦,無論基本的數字電路還是現代的集成電路,無不構建在邏輯門之上,把邏輯門和時鐘組合起來,人們搭建起了加法器、選擇器、鎖存器、觸發器,進而的運算單元、可控制單元、RAM。按照聰明的工程師設計好的電路圖紙再將這些基本的數字電路原件組合起來,再設計成可以印刷的集成電路形式,就可以構成各種專用的集成電路(ASIC)或者通用計算機處理器(CPU)等。FPGA相對ASIC來說更靈活。ASIC相對來說量產后會更廉價、節能,性能也更好。

專用集成電路只在意輸入和輸出,中間的一切算法會被固化到硬件設計中;而通用CPU則同時接收數據流和指令流,按照軟件工程師的程序指令序列執行一些列計算任務(雖有人將CPU也歸為ASIC,但是我覺得這是在硬件角度上來說的,從計算任務的可編程性角度CPU實際上是最靈活通用的)。FPGA則介于ASIC和CPU之間,它并非將邏輯門組成的原件之間的連接形式固化,也非做成最有利通用計算的形式動態地接收軟件指令來調動片上已有的計算單元,而是可以通過重復硬件編程來改變它邏輯門所組成的基本功能單元和調整這些單元之間的連接關系。

1. 硬件架構介紹

1.1 Overview

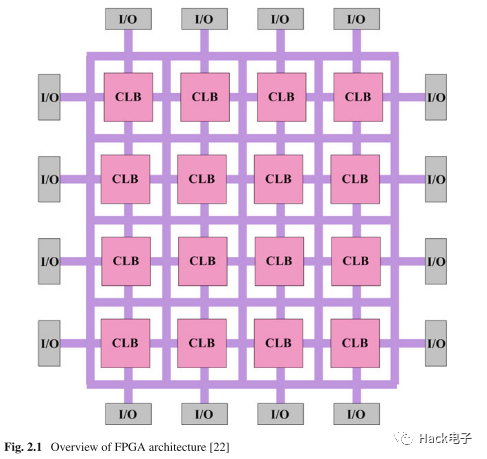

如下圖所示,邏輯上,FPGA主要由可編程的邏輯塊(programmable logic block, 主要是圖中CLB) 和 可編程互聯網絡 (programmable interconnect network / routing interconnect, 主要是圖中SB, CB和一些路由通道組成)。

+-----------+

| |

| LUT +-+

| | | +--------+ +-----------+

+-----------+ | | | | |

+----> BLE +----> CLB +----+

+-----------+ | | | | | |

| | | +--------+ +-----------+ |

| Flip-Flop +-+ |

| | +---------------------+ |

+-----------+ | | |

| Switch Box (SB) +----+

| | |

+---------------------+ |

+---> FPGA

+---------------------+ |

| | |

| Connection Box +----+

| (CB) | |

+---------------------+ |

|

+---------------------+ |

| | |

| I/O Block | |

| +----+

+---------------------+

空間布局上,可以簡單理解為下圖[1]:

- 按編程技術分類FPGA

FPGA的基礎,即可配置性依賴于存儲這些硬件門配置的介質,這種區別也成為FPGA的編程技術,按照這種硬件編程技術分類,FPGA分為三類: 基于SRAM的FPGA 、基于flash的FPGA和 基于反熔絲(antifuse)的FPGA [1]。

基于SRAM的FPGA是斷電易失的,所以需要在開機(startup)時通過JTAG編程,或者通過內置/外置的非易失存儲進行編程。

基于flash的FPGA的邏輯門本身就是非易失的。antifuse FPGA只能編程一次,不可逆。

1.2 組成單元

- Look-Up Table (SRAM based)

k-bound LUT或稱為LUT-k指的是有k個輸入、2^k個配置bits的布爾函數邏輯。如下圖[1]所示的basic logic element(BLE)由1個LUT-4和一個D型觸發器(Flip-Flop)構成,其中多個LUT-4有16個SRAM構成的配置位,通過這些配置為配置這些選擇器可以構成任意一個4輸入邏輯單元。

這個例子中,配置數據存在SRAM中,基于這種BLE的FPGA可以稱為基于SRAM(或說static memory)的FPGA。

- Switch Box (SRAM based)

如下圖[1]Switch Box中,分為雙向(a)和單向(b),一般后者更常用。這些switch都是基于pass transistor[3]的,每個pass transistor可以獨立地進行開關配置。

- 基于NAND Flash 的 FPGA 組件

同樣也有人提出基于NAND flash的FPGA,基于NAND flash相對基于SRAM,除了LUT、SB的配置形式需要重新設計外,NAND flash還具有NVM都有的非易失特點,可以減少外置flash存儲的使用,在上電后不用重新配置。

但是當今的主流FPGA技術還是SRAM,因為它和一般的CMOS集成電路技術分享技術,可以得到集成度、速度和功耗上的不斷提升。

一般的,要用Flash替代SRAM作為配置位,需要將SRAM cell替換為FMC(flash memory cell),如下圖以2-LUT為例[2],每個FMC都由2個flash晶體管Fp和Fq組成。當然論文[2]的作者也提出了針對NAND Flash的更高效替代方法。

1.3 IP核

FPGA的IP核(core)可以看做是軟件中的各種庫,避免了編程或設計人員重復造輪子。現代FPGA的可編程門陣列只占50%,其他大部分被硬IP核占據。

硬IP核是系統設計中一些常用的模塊,直接以模塊形式集成到FPGA的,比如memory block、calculating circuits,transceiver和protocol controller等,有些甚至加入了CPU、DSP等[6]。

2. 軟件流程

軟件流程也叫CAD(計算機輔助)流程,負責將人實現的上層應用邏輯映射到FPGA可編程硬件邏輯上,這個映射對最終的性能影響很大,所以這也是人們研究的一個重點。

這個過程將人寫的硬件描述語言HDL轉成可以最終編程到FPGA的比特流。這個過程大概分為5步: synthesis(綜合)、technology mapping, mapping, placement, routing。CAD 工具最后生成的就是bit流。軟件流程的框圖[1]如下:

-

Logic Synthesis 邏輯綜合 將VHDL/verilog這類硬件描述編程語言轉成布爾門、flip-flops。

-

Technology Mapping 將上一步的邏輯門轉成k-bound的LUT (lookup-table)。

-

Clustering/Packing 將多個LB(即k-bound LUT + flip-flop對,或稱BLE) 組成logic block clusters。主要有三種方法,各有利弊:

top-down:k路分割問題的基本的cost function 是 net cut,即partition間的邊數。

depth-optimal:用邏輯的重復換取更快的運行

bottom-up: FPGA CAD中用的比較多,因為運行快

-

Placement 主要決定logic block 的放到FPGA哪個logic block 位置,以最小的wiring 為主(wire length-driven placement)。或者平衡wiring 的密度(routability-driven placement);或者找到最快的電路速度(timing-driven placement)。常用partitioning或者模擬退火的方法

-

Routing 階段將網絡關聯到物理的routing網絡,當前state-of-the-art 算法是pathfinder。

在這些階段之后,還有時序分析階段和bitstream生成階段,最后的bitstream會真正的用于編程到SRAM存儲位來配置邏輯門。

3. Host FPGA管理系統的發展

[4] 提出了一種"FPGA操作系統", [5] 是對FPGA虛擬化的綜述。

[5]中的虛擬化其實是廣義的虛擬化,包括FPGA的 時分復用 、虛擬執行和 虛擬機 。

- 時分復用:任務大,單FPGA資源少(而非FPGA資源少、任務小而要一直進行切換FPGA配置)。

- 虛擬執行:將任務切分為多個需要通信的子任務(Petri-Net model),用一種運行時系統去管理它們。

- 虛擬機:有vFPGA支持的hypervisor,或者稱為shell。

FPGA虛擬化的目標和其他資源的虛擬化類似:單設備多租戶、資源管理、靈活性、隔離性、擴展性、虛擬化性能損失最小化、安全性、可靠性和易用性。

FPGA和CPU、GPU的根本區別是應用是硬件電路而非 匯編指令 。這帶來了大得多的切換開銷,不僅時間復用,空間也要復用。

...

對于FPGA相關工作的分類可以分為3種:resource level 、Node level 和 multi-node level。

3.1 Resource Level

分為可配置的(比如可以重新編程的邏輯陣列)和不可配置的(比如IP核)。

可配置overlays架構部分 :

Overlays架構的思路是將FPGA編譯(配置)階段分成兩部分,將CAD部分提前,只有硬件部分inline執行,來減少整體的重新配置時間。overlays的管理粒度可大可小,從軟核的虛擬化,到向量處理器,再到自定義處理單元(PE)再到細粒度的LUT單元。比較高層次的軟核、向量處理器對一般的軟件工程師更友好,不需要很多的硬件優化。而PE粒度(或稱coarse-grained reconfigurable arrays, CGRAs)以一個代數運算作為單元。又例如DRAGEN芯片專門針對DNA處理,overlay層允許生物領域專家能夠用FPGA加速運算。

overlay的二級制應用之于configuration bit 類似于 Java JVM的字節碼之于機器碼。所以像字節碼到原生機器碼的轉換一樣,overlay應用可以直接轉為overlay的FPGA配置。

不可配置的IO虛擬化部分 :

通常用來管理多個應用共享的IO資源,和其他虛擬化技術類似,虛擬化層可以用來提升安全/隔離性、隱藏IO操作的復雜性、監視資源占用和保證QoS,有時也可以提升性能(比如加buffer)等。從根本上,IO虛擬化的概念支持和CPU、軟件系統類似,只是具體實現不同。對于FOGA而言,控制邏輯可以在軟件層,也可以是硬件模塊,軟件層次用來實現更靈活的配置、硬件部分加速IO訪問和管理。

這里的總結主要指的是一些host的工作可以卸載到FPGA,比如FPGA輔助NIC[7]、輔助SSD[8],甚至用于加速memcached這種通用KV cache的網絡[9, 10]。

3.2 Node Level

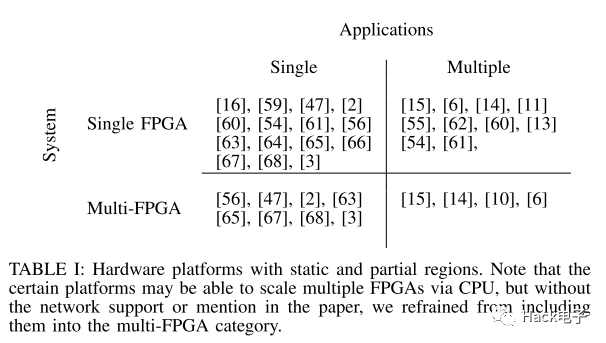

一般類似于虛擬機/多進程中的設備虛擬化,分為多/單應用組合上單/多FPGA四種[5]:

涉及到VMM、shell、調度等問題。

VMM型 將FPGA當成一種IO資源,像其他虛擬機一樣以CPU為主體,這種情況下FPGA就像GPU一樣用,對軟件開發者更友好。

Shell型 以FPGA自身,給出與host通信、與其他IO設備通信、應用管理等的設計。比如一種典型的設計是在FPGA的可配置部分,將管理部分和應用部分分開,利用FPGA的partial reconfiguration特性主要重新配置FPGA的應用部分,但這也會帶來很多開銷,包括讓長連線增加等。而且為實現多租戶增加的partial resion的數量也會導致更慢的運算速度,所以找到一個合適的partial regions 大小和數量很重要!

調度問題 在FPGA上和CPU不太一樣,因為上下文切換和partial重配置需要占的時間很長,所以搶占式調度當前不太現實。現在大多數方案基于非搶占調度,并且主要著眼時間的優化,最近也開始有工作研究空間的優化。

3.3 Multi-node Level

提供抽象,讓多個FPGA組合起來工作。大概架構分為3種[5]:

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636376 -

RAM

+關注

關注

8文章

1399瀏覽量

120575 -

可編程

+關注

關注

2文章

1325瀏覽量

41490 -

數字電路

+關注

關注

193文章

1651瀏覽量

83347

發布評論請先 登錄

深度剖析FPGA架構

深度剖析FPGA架構

評論