點擊上方藍字關注我們

基于ARM的FPGA嵌入式系統實現

ARM(Advanced RISC Machines)既可以認為是一個公司。也可以認為是對一類微處理器的統稱,還可以認為是一項技術。基于ARM技術的微處理器應用約占據了32位 RISC微處理器75%以上的市場份額,ARM技術正在逐步滲入到人們生活的各個方面[1]。到目前為止,ARM微處理器及技術已經廣泛應用到各個領域,包括工業控制領域、網絡應用、消費類電子產品、成像和安全產品等。

FPGA(Field Programmable Gate Array)是一種高密度現場可編程邏輯器件,其邏輯功能是通過把設計生成的數據文件配置到器件內部的靜態配置數據存儲器(SRAM)來實現的。FPGA具有可重復編程性,能靈活實現各種邏輯功能。

基于SRAM工藝的FPGA具有易失性。系統掉電以后其內部配置數據容易丟失,因此需要外接ROM保存其配置數據,系統上電后必須重新配置數據才能正常工作。目前有兩種方案可以實現,一種是使用專用的PROM,以Xilinx公司FPGA,XCFxx系列PROM為例,能夠提供FPGA的配置時序,上電時自動加載PROM中的配置數據到FPGA的SRAM中;另一種是在含有微處理器的系統(如嵌入式系統)中采用其他非易失性存儲器如E2PROM、 Flash存儲配置數據,微處理器模擬FPGA的配置時序將ROM中的數據置入FPGA。與種方案相比,該方案節省成本、縮小系統體積。適用于對成本和體積苛刻要求的系統。

在便攜式虛擬儀器設計中,使用嵌入式系統和FPGA實現系統功能。嵌入式微處理器采用Samsung公司的ARM7TDMI系列處理器 S3C44BOX:FPGA采用Xilinx公司的Spartan-3E系列XC3S100E,采用S3C44BOX完成對XC3S100E的配置。取得了良好效果。

2 從串配置的原理

2.1從串配置原理

Xilinx公司的Spartan-3E系列FPGA產品是采用90 nm工藝的2.5 V低電壓FPGA器

件,具有高性能、低功耗、可無限次編寫的特點。XC3S100E是Spartan-3E系列FPGA中的一款,總門數達10萬門,可采用從串、主串、從并、主并、JTAG等模式對其進行配置[2]。XC3S100E與從串配置模式相關的主要引腳功能如下:

M[2:0]:配置模式選擇。M2、M1、M0均接上拉電阻,即M[2:0]:111時為從串模式;

CCLK:配置時鐘,微處理器提供時鐘源,且上升沿有效:

DIN:串行配置數據輸入:

DOUT:串行數據輸出,用于菊花鏈式配置:

PROG_B:低電平異步復位FPGA內部邏輯,內部可配置:Memory完全復位后,該引腳指示高電平。

當此引腳為高時,才能配置FPGA:

INIT_B:由低電平到高電平跳變時,采樣配置模式,即M[2:0]的值確定配置方式;配置過程中若出現配置錯誤,INIT_B將呈現低電平;

DONE:復位時為低電平。若配置成功,則為高電平。

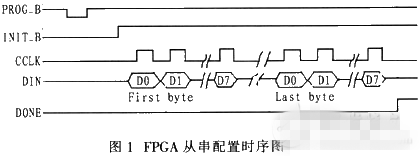

2.2微處理器從串配置:FPGA的時序

FPGA的配置過程如下:

系統上電后,將PROG_B拉低以復位FPGA內部邏輯重新配置FPGA,充分復位內部邏輯后(約100μs),將PROG_置高。

INIT_B為低電平,PROG_B拉高保持300 ns后,FPGA將INIT_B置高。在INIT_B由低向高跳變的瞬間,采樣配置模式M[2:0]。此系統采用從串配置模式。

在FPGA采樣配置模式后,微處理器就可以向FPGA配置時鐘CCLK和數據,在CCLK的上升沿,傳輸數據至DIN,數據字節先發送低位,再發送高位。配置過程中若發生錯誤,則INIT_B為低電平。

所有的配置數據傳送完成,CRC校驗無誤。則DONE為高電平,否則為低電平。

DONE為高電平,FPGA釋放全局三態(GTS),激活I/O引腳,釋放全部置位復位(GSR)和全局寫使能(GWE)有效,開始執行配置區的邏輯。

微處理器從串配置FPGA的時序如圖1所示。

2.3 配置文件的產生方法

利用Xilinx公司提供的開發工具ISE8.1,經過綜合、映射、布局布線后可產生編程文件,編程文件含有.bit、.bin、.mcs、.tek、.hex等格式。其中,.bit格式用于JTAG,其他幾種格式用于專用PROM編程。首先按照產生專用 PROM編程文件的方法來產生.bin文件.然后將該.bin文件轉換成ASCⅡ碼文件的存儲形式,并且各個字節之間用逗號分隔。再將該配置數據存放在系統程序的一個頭文件的數組config_data_array[]中,作為系統程序源代碼的一部分,并和其他程序一起編譯。

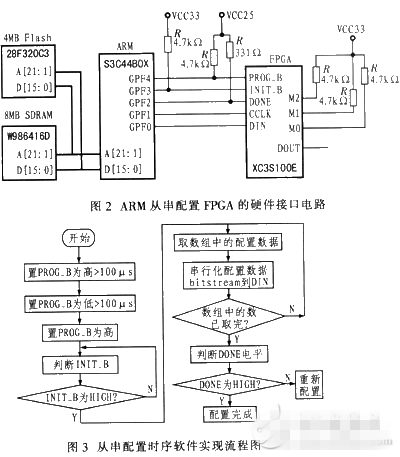

3 硬件設計

嵌入式微處理器S3C44BOX內置ARM7TDMI核,集成了豐富的外圍功能模塊,內部8 kB Cache大大提高了性能。S3C44BOX可訪問256MB的地址空間,工作頻率達66 MHz 。采用4 MB Flash作為程序存儲器,可用于存放系統運行的代碼。XC3S100E從串配置程序和配置文件都固化于其中保存,該Flash支持低電壓(1.65 V~3.3 V)寫操作。8 MB的SDRAM是程序的運行空間,直接運行Flash中的代碼,但速度非常慢。通常是將Flash中的代碼移至SDRAM中。S3C44BOX與 XC3S100E主要通過PROG_B、INIT_B、DONE、CCLK、DIN 5根信號線連接,如圖2所示。其中VCC33表示3.3 V,VCC25表示2.5 V。

4 軟件設計

軟件設計流程如圖3所示。配置軟件的編程要確保ARM完全按照配置信號的時序工作,關鍵問題

是采用S3C44BOX的通用I/O口GPF0、GPF1、GPF2、GPF3、GPF4模擬DIN、CCLK、DONE、INIT_B、PROG_B的時序。

在S3C44BOX中,大多數引腳都是多功能引腳,可以通過端口配置寄存器選擇相應的引腳功能。

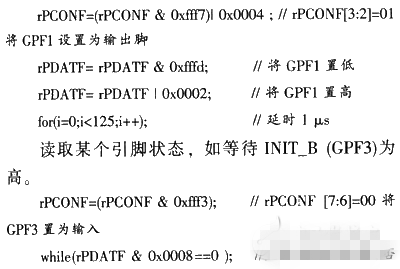

以端口F為例,控制寄存器rPCONF用作設定引腳的輸入、輸出或特殊功能;數據寄存器rPDATF[0:8]對應于GPF0~GPF8引腳上的數據。讀寫寄存器rPDATF的各個位對應于引腳的讀或寫。例如,CCLK上升沿時序是向GPF1先寫0,再寫1得到,延時程序則由for循環實現。

則一直循環等待

CCLK在每個上升沿把1 bit的數據置入DIN中,先將GPF1置低,在GPF0準備好1 bit數據,再將GPF1置高即可,以此循環將config_data_array[]中的每個字節按先低位再高位的次序寫入FPGA。

Xilinx的FPGA配置文件大小相同,與FPGA內部邏輯設計的復雜度無關。以Spartan_3E系列的10萬門FPGA XC3S100E為例,它的配置文件固定為581 344 bit,若CCLK的時鐘周期置為2μs,配置時間約為1.2 s。

5 實驗結果驗證

驗證環境:硬件采用自行開發的實驗板和武漢創維特公司的:JTAG硬件仿真器;軟件則使用Xilinx公司的開發工具ISE8.1和武漢創維特公司的集成開發環境ADT 1000(支持ARM7,ARM9)。

利用Verilog HDL編寫程序led.v在七段數碼管上循環顯示0~F,采用:ISE8.1編譯、綜合、映射、布局布線。生成用于編程專用PROM的led.bin文件。用一個簡單的C程序將.bin文件轉換成ASCⅡ碼文件,再將ASCⅡ碼文件復制到配置數據數組config_data_array[]中,然后在 ADT環境下編譯配置程序、配置數據和系統程序,將生成的.bin文件通過JTAG口燒寫到Flash中。重新上電后,FPGA配置正常,實驗結果與預設相一致。

6 結束語

基于ARM的FPGA從串配置方案結構簡單、接線容易、軟件編程簡單,非常適用于嵌入式系統設計。雖然該控制電路是為Xilinx公司 Spartan-3E系列的FPGA設計的,但稍加修改也可用于其他系列FPGA器件,故具有一定的通用性。另外,由于FPGA具有可重復配置的靈活性,在嵌入式系統中可通過串口、網口遠程燒寫Flash,重構系統功能,這種在線重構技術為設備的智能化在線維護、功能重組和在線升級等提供了可能,而且靈活性很強。本文提出的方案對數字系統設計具有借鑒意義,有著廣闊的應用前景。

往期推薦

往期推薦

掃碼二維碼

獲取更多精彩

FPGA設計論壇

原文標題:基于ARM的FPGA嵌入式系統實現

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636247

原文標題:基于ARM的FPGA嵌入式系統實現

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

arm嵌入式主板優缺點

從小白到大牛:Linux嵌入式系統開發的完整指南

什么是嵌入式操作系統?

高云半導體助力2025全國大學生嵌入式與系統設計大賽FPGA賽段圓滿落幕

ARM嵌入式這樣學

嵌入式與FPGA的區別

嵌入式系統的定義和應用領域

怎么結合嵌入式,Linux,和FPGA三個方向達到一個均衡發展?

嵌入式開發入門指南:從零開始學習嵌入式

嵌入式開發:高門檻的系統性工程與 996 的行業困局

基于ARM的FPGA嵌入式系統實現

基于ARM的FPGA嵌入式系統實現

評論