在SpinalHDL中使用之前已有的Verilog等代碼的時候需要將這些代碼包在一個BlackBox里面,但是如果這些代碼里面有時鐘和復位,我們需要怎么將時鐘和復位端口和SpinalHDL中已有的時鐘域連接起來呢?

當BlackBox中只有一個時鐘的時候可以直接使用mapClockDomain完成時鐘信號和復位信號的賦值。在mapClockDomain中如果沒有指定時鐘域的話就采用的是默認時鐘域。

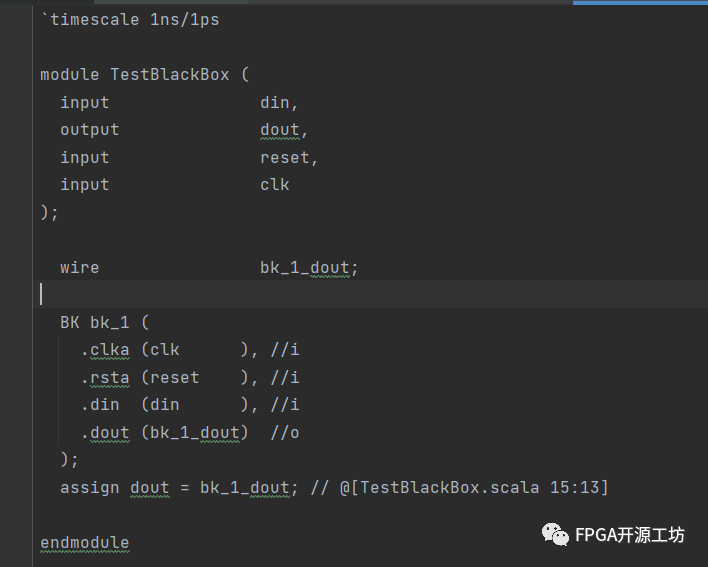

import spinal.core._ import spinal.lib._ class BK extends BlackBox{ val clka = in Bool() val rsta = in Bool() val din = in Bool() val dout = out Bool() mapClockDomain(clock = clka, reset = rsta) } class TestBlackBox extends Component { val din = in Bool() val dout = out Bool() val bk = new BK bk.din <> din bk.dout <> dout } object TestBlackBox extends App{ SpinalVerilog(new TestBlackBox) }

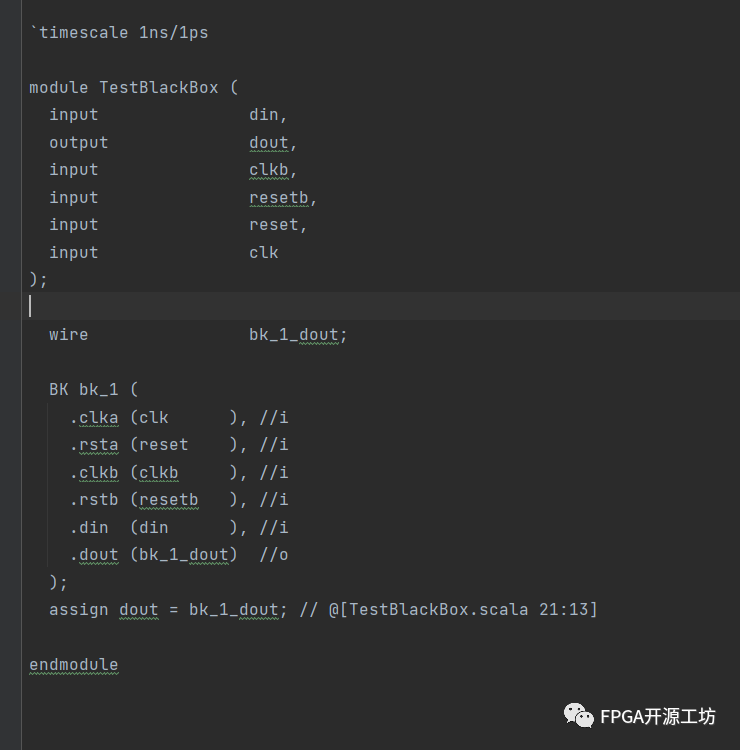

當有兩個時鐘域的時候,就需要把時鐘域給指定一下了,在下面代碼中將時鐘域通過參數的方式傳了進來。

import spinal.core._

import spinal.lib._

class BK(clockDomaina: ClockDomain, clockDomainb: ClockDomain) extends BlackBox{

val clka = in Bool()

val rsta = in Bool()

val clkb = in Bool()

val rstb = in Bool()

val din = in Bool()

val dout = out Bool()

mapClockDomain(clockDomaina,clock = clka, reset = rsta)

mapClockDomain(clockDomainb,clock = clkb, reset = rstb)

}

class TestBlackBox extends Component {

val din = in Bool()

val dout = out Bool()

val clkb = in Bool()

val resetb = in Bool()

val clockDomainb = ClockDomain(clock = clkb,reset = resetb)

val bk = new BK(this.clockDomain,clockDomainb)//默認時鐘域和新建的時鐘域b

bk.din <> din

bk.dout <> dout

}

object TestBlackBox extends App{

SpinalVerilog(new TestBlackBox)

}

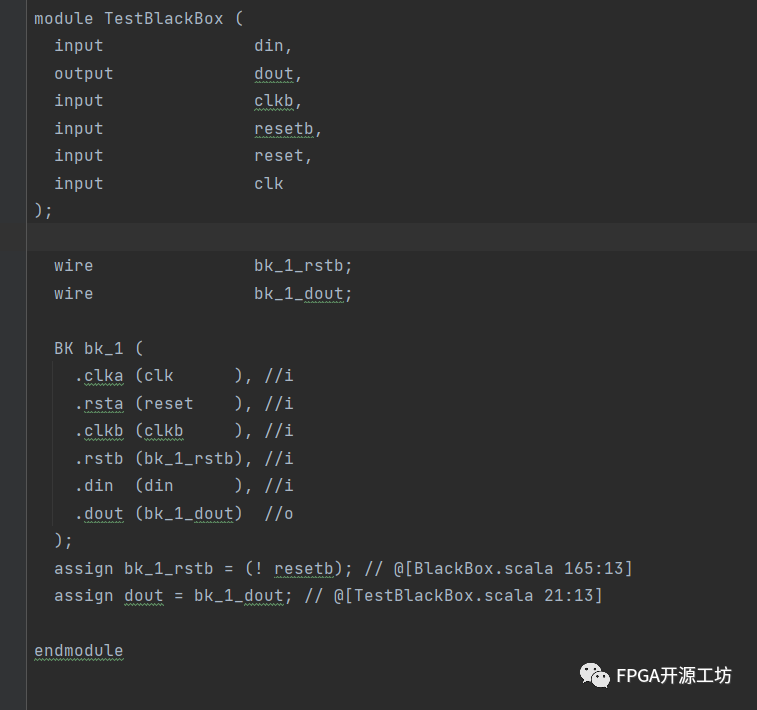

因為在SpinalHDL中默認時鐘域是高復位的,但是我們已有的IP可能是低復位的,這個時候就需要在mapClockDomain中指定一下復位信號是HIGH還是LOW。在下面代碼中就將時鐘域b下面的復位指定為低復位。

import spinal.core._

import spinal.lib._

class BK(clockDomaina: ClockDomain, clockDomainb: ClockDomain) extends BlackBox{

val clka = in Bool()

val rsta = in Bool()

val clkb = in Bool()

val rstb = in Bool()

val din = in Bool()

val dout = out Bool()

mapClockDomain(clockDomaina,clock = clka, reset = rsta)

mapClockDomain(clockDomainb,clock = clkb, reset = rstb, resetActiveLevel = LOW)

}

class TestBlackBox extends Component {

val din = in Bool()

val dout = out Bool()

val clkb = in Bool()

val resetb = in Bool()

val clockDomainb = ClockDomain(clock = clkb,reset = resetb)

val bk = new BK(this.clockDomain,clockDomainb)

bk.din <> din

bk.dout <> dout

}

object TestBlackBox extends App{

SpinalVerilog(new TestBlackBox)

}

以上三種情況應該足夠應對一般情況下BlackBox的時鐘域的賦值了。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

30文章

1374瀏覽量

114522 -

時鐘

+關注

關注

11文章

1971瀏覽量

134986 -

HDL

+關注

關注

8文章

332瀏覽量

48973 -

復位

+關注

關注

0文章

179瀏覽量

25045 -

時鐘信號

+關注

關注

4文章

504瀏覽量

29965

原文標題:SpinalHDL BlackBox時鐘與復位

文章出處:【微信號:FPGA開源工坊,微信公眾號:FPGA開源工坊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

在SpinalHDL里實現優雅的添加待跟蹤波形信號

波形跟蹤信號。在SpinalHDL里,我們可以借助blackBox及scala語言本身實現在SpinalHDL環境里實現對ILA的集成。上面的代碼實現了用于添加ILa單元實現波形追蹤的代碼,在調用

發表于 06-22 14:37

在SpinalHDL的設計中集成現有RTL設計(IP)的渠道——BlackBox

在集成IP時需顯示映射IP的時鐘與復位信號,SpinalHDL提供了mapClockDomain、mapCurrentClockDomain兩個函數用于時鐘映射,mapClockDom

發表于 06-22 14:59

關于SpinalHDL仿真中信號驅動那點事兒

到時鐘信號從低電平到高電平變化完成之后才推出。那么我們在隨后對dataIn的賦值其實是發生在clk上升沿到來后的0+時間才發生的。 從這里代碼分析我們可以看出,在SpinalHDL的仿真里:復位信號會

發表于 06-24 16:34

聊一聊SpinalHDL 1.6.1引入的blackbox inline功能

BlackBox在之前的文章中,曾介紹過如何封裝兼容別人的RTL代碼:SpinalHDL——集成你的RTL代碼整體的思路還是簡潔明了的,相信讀完后照著做很快就能上手。這對于保持設計的兼容性及混合

發表于 06-29 16:02

談談SpinalHDL中StreamCCByToggle組件設計不足的地方

模塊設計很巧妙,從原理分析的角度來講挺完美的。但是,百密一疏,這個模塊在設計時,對于兩側時鐘域復位信號的處理,作者并未有妥善的考慮。 現象分析 先來看下面這個example和其測試代碼

發表于 06-30 15:11

如何在SpinalHDL里啟動一個仿真

withConfig(config: SpinalConfig)函數進行配置。這里的配置常用的是對時鐘域的配置,包含時鐘有效邊沿、復位信號類型、時鐘頻率等。如下例所示:而DUT的編譯則

發表于 07-26 16:59

記錄一個在使用BlackBox中parameter踩到的坑

SpinalHDL doc里面也曾提到,在創建BlackBox時,關于原始RTL代碼中的parameter的處理方式為:嗯,看起來很簡單,我們照貓畫虎就好了,最近在寫代碼時偶然間踩到了一個坑,這里用下面的代碼來說

發表于 08-31 14:58

SpinalHDL設計錯誤總結相關資料分享

設計。以下是SpinalHDL檢查的簡要概括: 重復賦值 時鐘域交叉 層次化違例 組合邏輯環路 Latch 未驅動的信號 位寬不匹配 得不到的switch生命 在每個SpinalHDL

發表于 10-24 15:37

SpinalHDL里時鐘域中的定制與命名

聊一聊在SpinalHDL里時鐘域中時鐘的定制與命名。 相較于Verilog,在SpinalHDL里,其對時鐘域有著更細致的描述,從而也能夠

STM32電源管理、復位、時鐘

第二篇文章——STM32電源、復位、時鐘電源管理電源電壓調節器可編程電壓監測器(PVD: Programmable voltage detector )低功耗模式復位Cortex-M3的復位

發表于 01-05 14:25

?10次下載

SpinalHDL里用于跨時鐘域處理的一些手段方法

每一個做數字邏輯的都繞不開跨時鐘域處理,談一談SpinalHDL里用于跨時鐘域處理的一些手段方法。

原來SpinalHDL中BlackBox封裝數組接口如此簡單

當在SpinalHDL中調用別人的RTL代碼時,需要采用BlackBox進行封裝。對于大多數場景,想必小伙伴們都已輕車熟路。今天著重來看下當RTL代碼的接口中存在數組形式的接口時如何處理。

SpinalHDL BlackBox時鐘與復位

SpinalHDL BlackBox時鐘與復位

評論