外接電容越大?晶振起振越慢?

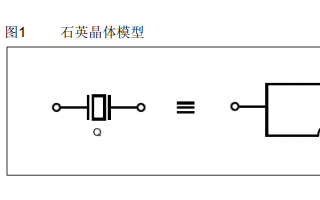

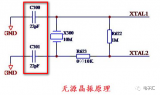

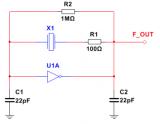

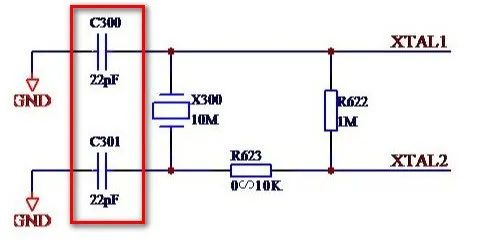

首先說明的是:但凡需要外接電容的晶振均為無源晶振。另外,注意區分外接電容C1和C2(接地電容,對地電容)并不等同于晶振負載電容(CL)。C1和C2是電路板和包括IC和晶振在內的組件的總電容值。

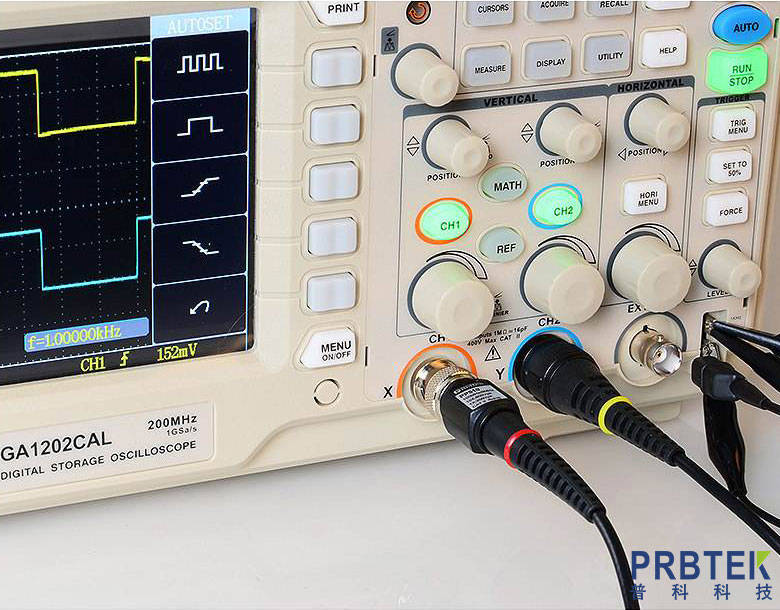

一般情況下,增大無源晶振的外接電容將會使晶振振蕩頻率下降,即偏負向。舉例,若無源晶振12MHz的外接電容為18PF,實際輸出頻率為12.002876MHz。更改外接電容為27PF之后,該晶振的實際輸出頻率會有所降低,如:11.9998923 MHz。

晶振的外接電容越大,晶振的振蕩越穩定,但是會增加起振時間,即晶振起振慢,其原理是外接電容會存儲更多電荷,即降低電流強度,從而降低電路提供給晶振起振的激勵功率。

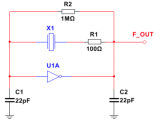

當無源晶振的輸出波形出現削峰、畸變時,這一般是由于電流過驅動(over drive)導致,可以嘗試通過串聯一顆電阻解決,電阻值一般在幾十kΩ~幾百kΩ。如果要穩定波形,則可嘗試并聯一顆1M反饋電阻。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

無源晶振

+關注

關注

1文章

888瀏覽量

17850 -

負載電容

+關注

關注

0文章

153瀏覽量

11144 -

反饋電阻器

+關注

關注

1文章

46瀏覽量

5599

原文標題:外接電容大小與晶振起振快慢關系

文章出處:【微信號:晶科鑫,微信公眾號:晶科鑫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

晶振的外接電容值選擇不當,會對電路產生什么影響?

如果晶振的外接電容值選擇不當,可能會對電路產生以下影響 :

1.頻率穩定性: 電容值過小可能導致頻率穩定性下降,容易受到外界因素的干擾。電容

發表于 03-04 11:33

如何正確計算并使用晶振的外接負載電容

的估算值為3pF到5pF。3. 計算實際外接電容:從CL值中減去雜散電容Cs。將結果乘以2,因為晶振通常需要兩個外接電容,它們是并聯的。示例

發表于 08-09 15:40

設計MCU時晶振不工作怎么辦?MCU如何選型?怎樣外接電容?

在設計MCU,會遇到晶振不工作,這個文檔的內容解釋MCU如何選型,以及怎樣外接電容。使晶振更好的工作,希望這個文檔內容可以幫助大家解決現有難

發表于 07-10 08:00

?10次下載

如何區分晶振的負載電容與外接電容

經常遇到有人把晶振的負載電容與外接電容混淆,甚至還有人誤以為這是指同樣的參數。這里需要特別指出的是:若你這樣想,就大錯特錯了。

外接電容越大晶振起振越慢嗎?

外接電容越大晶振起振越慢嗎?

評論