在進行PCB設計時,都必須使用到過孔,對走線進行換層處理。在走線進行打過孔之前,必須先要添加過孔,這樣在PCB布線時才可以使用過孔,具體操作的步驟如下所示;

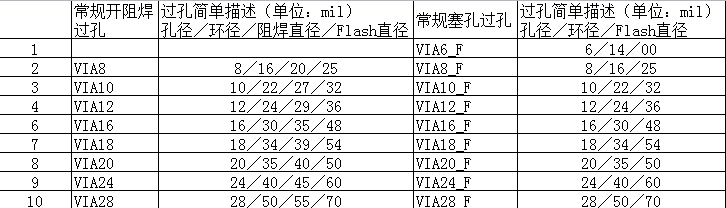

1)需要使用pad designer工具制作過孔,這個在前面的PCB封裝庫問答中已經詳細講述過,這里不再做贅述,我們在PCB常用的過孔有幾下幾種,如圖1所示:

圖1常用過孔類型示意圖

過孔制作完成之后,在PCB中將制作好的過孔的路徑指定在封裝庫路徑下,才可以在后面調用已經制作好的過孔。

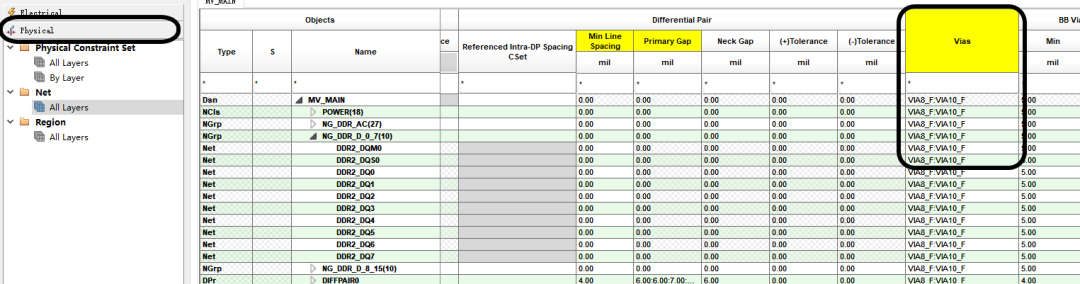

2)打開規則管理器,執行菜單命令Setup-Constraints-Constraints Manager,進入規則管理器,在左側邊欄中選擇Phyical物理規則,點擊all layer,然后在右側Vias這一欄,雙擊空白處,如圖2所示;

圖2添加過孔示意圖

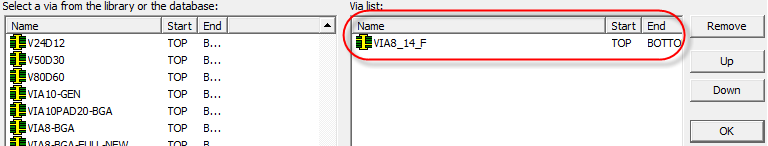

3)在彈出的過孔列表中,選擇過孔到過孔列表中,雙擊左側的過孔就可以添加到右側的PCB過孔列表中,點擊OK選項,過孔就添加成功了,如圖3所示;

圖3過孔選取示意圖

4)回到規則管理器中,在Vias哪一欄可以看到剛才選擇的過孔已經成功添加了,這樣在PCB布線中雙擊鼠標左鍵就可以打孔換層了。

聲明: 本文凡億教育原創文章,轉載請注明來源!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207往期文章 精彩回顧

Cadence Allegro飛線的隱藏關閉

嘉立創EDA專業版PCB絲印的快速調整方法

嘉立創EDA專業版尺寸標注操作教程

嘉立創EDA專業版PCB距離測量操作

嘉立創EDA PCB設計對齊與等間距操作

點擊“閱讀原文”查看更多干貨文章

原文標題:Cadence Allegro PCB過孔添加與設置

文章出處:【微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

-

pcb

+關注

關注

4412文章

23916瀏覽量

425459

原文標題:Cadence Allegro PCB過孔添加與設置

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

04. 如何在 Allegro 中設置淚滴?| 芯巧Allegro PCB 設計小訣竅

03. 如何把 PCB 板上的線變成銅皮?| 芯巧Allegro PCB 設計小訣竅

02. 如何在 Allegro 中快速自定義字體?| 芯巧Allegro PCB 設計小訣竅

01. 如何在 Allegro 中快速區別不同網絡?| 芯巧Allegro PCB 設計小訣竅

技術資訊 I Allegro設計中的過孔陣列設計

PCB設計中過孔為什么要錯開焊盤位置?

借助Cadence工具簡化PCB設計流程

凡億Allegro Skill字符功能-添加中文字符

Allegro Skill布線功能--過孔助手

Allegro Skill布線功能-改變過孔網絡介紹與演示

Allegro Skill布線功能-添加差分過孔禁布區

作為硬件工程師,你用那款PCB 設計軟件?超全EDA工具整理!

Cadence SPB OrCAD Allegro22.1安裝包

Cadence SPB OrCAD Allegro24.1安裝包

Cadence Allegro PCB過孔添加與設置

Cadence Allegro PCB過孔添加與設置

評論