隨著FPGA的不斷發展,FPGA本身自帶的PCIE硬核的數量越來越多,本文以ZU11EG為例介紹,如何進行對應的硬件引腳分配。

設計目標:ZU11EG FFVC1760封裝,掛載4組NVME,接口為PCIE X4 ,

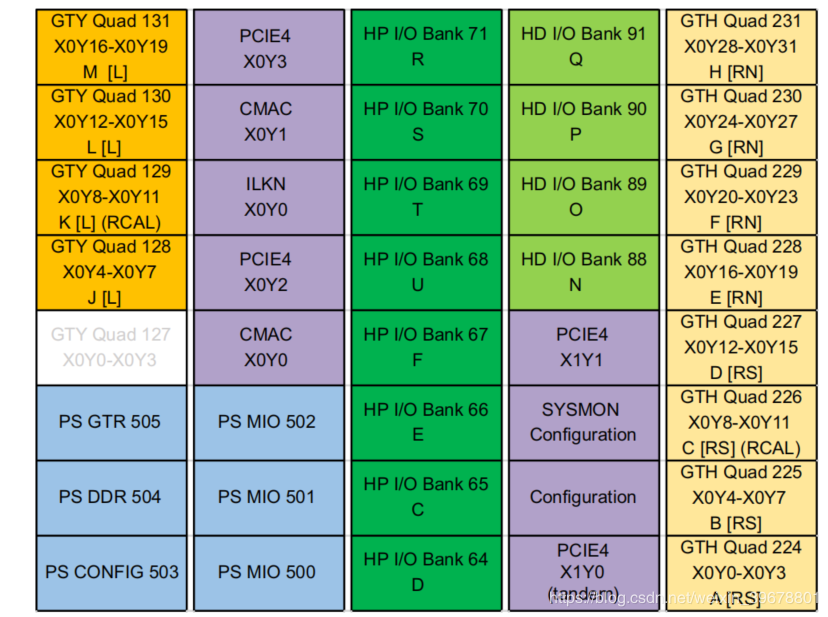

先我們先對ZU11EG的資源進行分析,在UG1075中我們可以清楚的看到其包含4個PCIE塊,分別位于X0Y2,X0Y3,XIY1,XIY0.

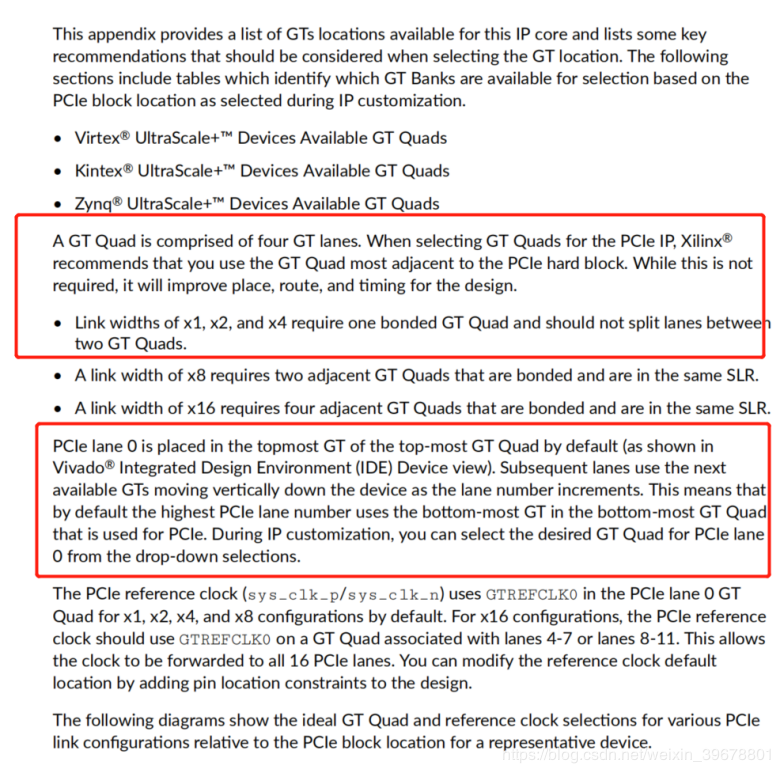

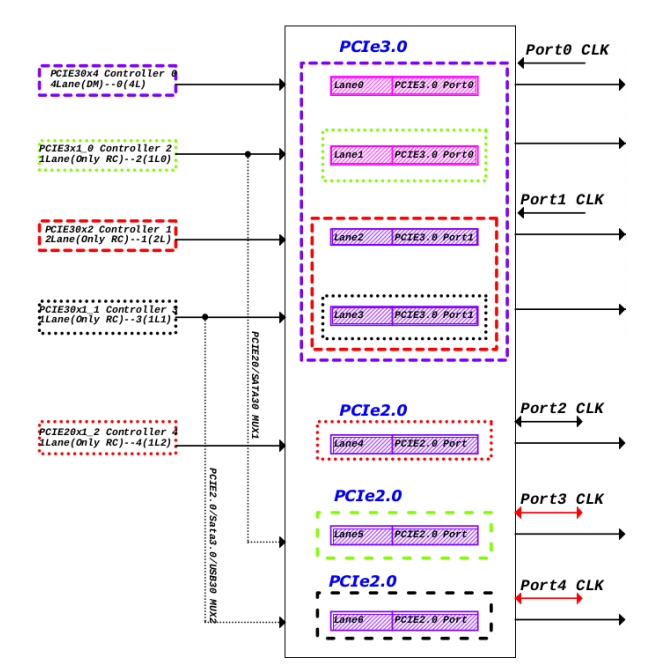

在文檔PG213上我們可以看到如下:

總結上文:在硬件設計引腳分配的時候我們需要知道:

1、一個GT Quad由四個GT車道組成。為PCIe IP選擇GT Quads時,Xilinx建議您在最靠近PCIe硬塊的地方使用GT Quad。雖然這不是必要時,它將改善設計的位置,路線和時間。

2、需要注意PCIE lane 0的位置

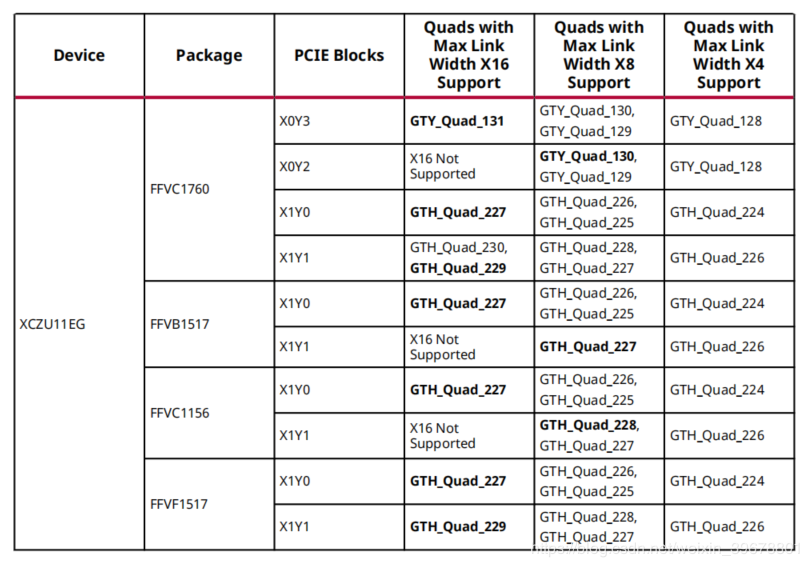

3.根據些表格,這些表格根據以下內容確定哪些GT庫可供選擇:IP自定義期間選擇的PCIe塊位置。

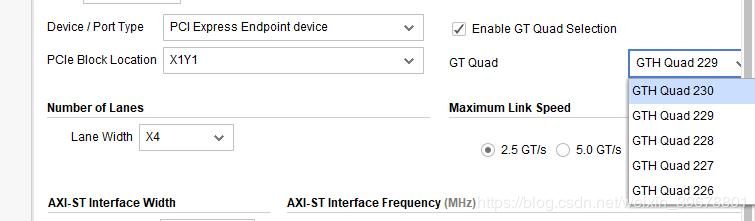

那如何驗證自己的分配結果呢?最終在實際使用的時候我們會應用到相關的IP核,最簡單也是最靠譜的方法,是采用vivado新建工程,生成PCIE的IP核進行驗證,如下圖所示,可以清楚的知道對應的那些可用。

在FPGA硬件設計中,引腳分配是最重要的一步,也是最關鍵的一步。

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636360 -

封裝

+關注

關注

128文章

9249瀏覽量

148632 -

硬件設計

+關注

關注

18文章

459瀏覽量

45622

發布評論請先 登錄

相關推薦

熱點推薦

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡解決方案

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡一、概述本板卡系我公司自主研發,采用Xilinx公司的XCKU115-3-FLVF1924-E芯片作為主處理器,主要用于

發表于 07-27 16:49

基于Xilinx XCKU115的半高PCIe x8硬件加速卡

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡北京太速科技有限公司一、概述 本板卡系我公司自主研發,采用Xilinx公司的XCKU115-3-FLVF1924-E芯片

發表于 08-22 17:31

XCKU115板卡資料:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡一、概述 本板卡系我公司自主研發,采用Xilinx公司的XCKU115-3-FLVF1924-E芯片作為主處理器,主要用

發表于 10-25 16:00

基于Xilinx FPGA的Memcached硬件加速器的介紹

本教程討論基于Xilinx FPGA的Memcached硬件加速器的技術細節,該硬件加速器可為10G以太網端口提供線速Memcached服務。

XILINX FPGA的硬件設計總結之PCIE硬件設計避坑指南

: 總結上文:在硬件設計引腳分配的時候我們需要知道: 1、一個GT Quad由四個GT車道組成。為PCIe IP選擇GT Quads時,Xilinx建議您在最靠近

Xilinx 7系列FPGA收發器架構之硬件設計指導(一)

引言:本文我們介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題,指導硬件設計人員進行原理圖及PCB設計。本文介紹以下內容:GTX/GTH收發器管腳概述 GTX/GTH收

發表于 11-06 19:51

?35次下載

FPGA PCIe加速卡開源硬件及例程介紹

基于Xilinx Artix-7系列FPGA芯片設計的M.2 M-Key FPGA加速卡,引出Artix7-484腳芯片的4條高速GT,最高支持PCIE2.0*4速率。

基于FPGA的硬件引腳分配設計總結

可以看到如下: 總結上文:在硬件設計引腳分配的時候我們需要知道: 1、一個GT Quad由四個GT車道組成。為PCIe IP選擇GT Quads時,Xilinx建議您在最靠近

一文搞懂?RK3588 PCIe:從硬件資源到拆分配置?+?避坑指南(含腦圖)

資源解析、 3? 大拆分方案實戰、關鍵配置步驟及避坑要點,附帶可視化腦圖,助力開發者快速落地? PCIe? 相關項目。 ? ? ? 一、 RK3588 PCIe? 核心

FPGA硬件加速卡設計原理圖:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡 PCIe半高 XCKU115-3-FLVF1924-E芯片

FPGA硬件加速, PCIe半高卡, XCKU115, 光纖采集卡, 信號計算板, 硬件加速卡

基于XILINX FPGA的硬件設計總結之PCIE硬件設計避坑

基于XILINX FPGA的硬件設計總結之PCIE硬件設計避坑

評論