當前設計的一款ADC芯片,其具有數據串行輸出模式,由于串行輸出的數據不能夠直接后接理想DAC進行波形分析,因此不太方便。最好是能插入一個Serial_To_Parral的轉換模塊,將串行輸出的數據轉換為并行數據,再后接理想DAC產生模擬波形,如此就便于FFT分析了。

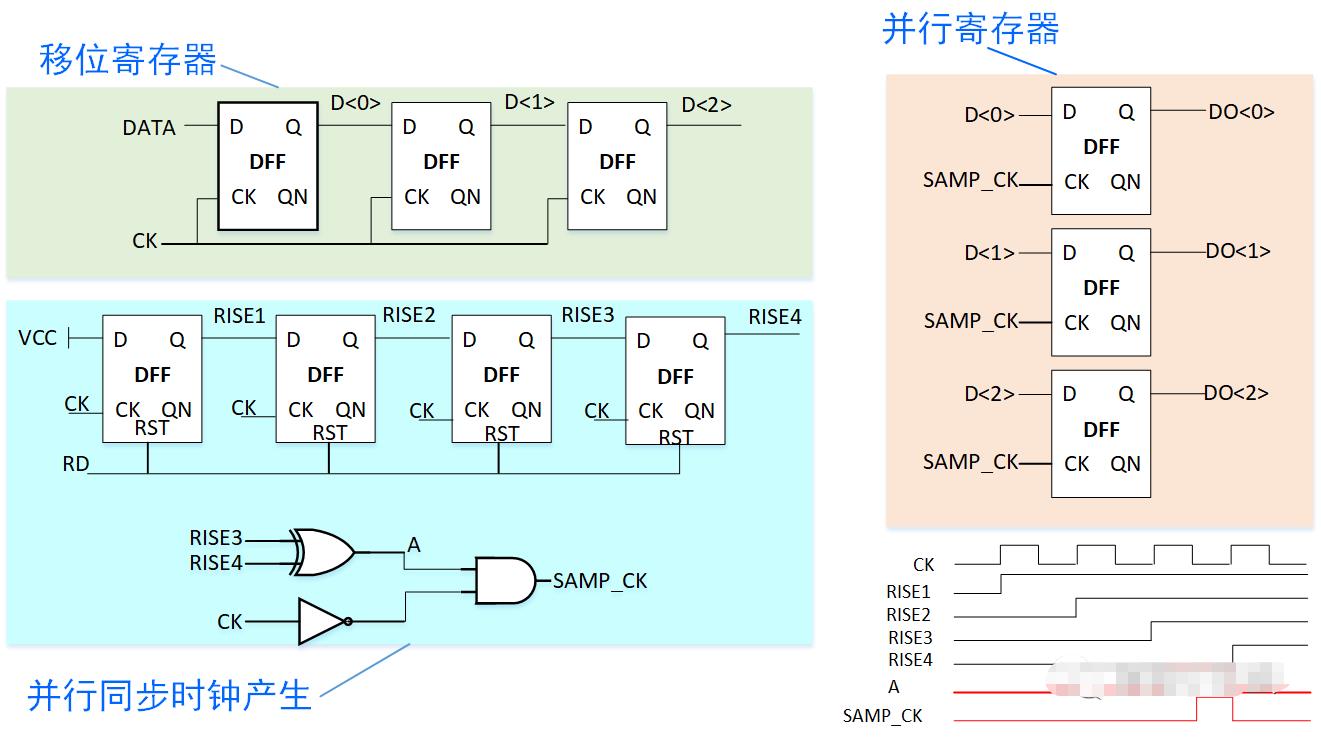

Serial_To_Parral:這里說的串并轉換電路,指可以實現串行數據轉并行數據的電路。本文提到的Serial_To_Parral模塊是用VerilogA基本組件搭建的,以一個3bit數據的轉換作為示例,其原理框圖如下圖所示:

圖1:Serial_To_Parral原理框圖

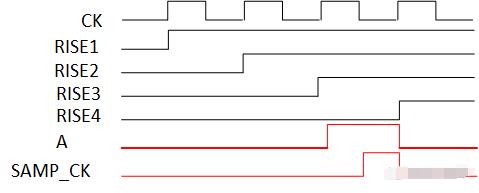

該電路的思路是:移位寄存器負責對DATA的每bit數據進行采樣并且向右移位,移位寄存器的每級輸出分別與右側并行寄存器的輸入相連。隨著CK最后一次上沿采樣完DATA數據后,在其后的半周期內將并行寄存器上的數據同步輸出。

圖2:相關時序圖

并行寄存器的同步采樣時鐘為“并行同步時鐘產生電路”產生。注意到,產生同步采樣時鐘的電路使用了RD信號對DFF進行復位。RD信號為ADC系統的讀取使能信號,RD=0時有效。因此在RD=1期間,DFF復位,SAMP_CK=0,并行寄存器上的輸出保持不變。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

寄存器

+關注

關注

31文章

5608瀏覽量

129968 -

adc

+關注

關注

100文章

7511瀏覽量

555943 -

波形

+關注

關注

3文章

407瀏覽量

33074 -

轉換電路

+關注

關注

2文章

210瀏覽量

31386 -

串行數據

+關注

關注

0文章

68瀏覽量

16958

發布評論請先 登錄

相關推薦

熱點推薦

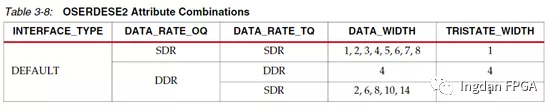

如何使用其gearbox功能來實現不同的比率的串并轉換功能

在SelectIO簡介連載一中介紹了其架構,本章會繼續介紹如何使用其gearbox功能來實現不同的比率的串并轉換功能。7 Series FPGA中LVDS使用了ISERDESE2,SDR Rate可設為2,3,4,5,6,7,8

發表于 08-02 08:03

?4536次閱讀

FPGA設計思想與技巧之串并轉換和流水線操作

的直接體現。串并轉換的實現方法多種多樣,根據數據的排序和數量的要求,可以選用 寄存器、 RAM 等實現。前面在乒乓操作的圖例中,就是通過 DPRAM

發表于 02-10 11:40

FPGA串并轉換實現問題

各位大神是否能用400個以上I/O口的FPGA芯片,實現串并轉換,一個串行RS232輸入,將輸入的50個字節的數據轉換控制 50個8位并行輸出。具體大概應該怎么做

發表于 07-08 17:19

FPGA串/并轉換的思想相關資料推薦

(18)FPGA串/并轉換的思想1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA串/并轉換的思想5)結語1.2 FPGA簡介FPGA(Field

發表于 02-23 07:38

串并轉換VHDL代碼

通過多通道串-并轉換器將多個同步串行數據流轉換為并行數據 xilinx提供

Synthesis

1. Launch synplify

2.

發表于 05-20 11:30

?515次下載

84調制解調程序(包括串并轉換,判決等等)

84調制解調程序(包括串并轉換,判決等等):

fs=700000000;%樣頻率 f0=70000000;%載頻fd=5000000;n=400;a=[1 0 1 1 0 0 1 1 0 1 0 0 0 1 1 1 0 1 0 0];%//////////

發表于 11-28 11:48

?29次下載

串并轉換 通過多通道串-并轉換器將多個同步串行數據流轉換為并

串并轉換 通過多通道串-并轉換器將多個同步串行數據流轉換為并行數據(源代碼)

** Filenames and Descri

發表于 06-14 09:24

?50次下載

(18)FPGA串/并轉換的思想

(18)FPGA串/并轉換的思想1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA串/并轉換的思想5)結語1.2 FPGA簡介FPGA(Field

發表于 12-29 19:40

?2次下載

串并轉換電路的實現方案

串并轉換電路的實現方案

評論