陽紅成,蘇小光

(南京航空航天大學 航空宇航學院,江蘇 南京 210016)

摘要:在現代電子系統設備和可靠性增長工作的推動下,可靠性技術和工程實踐得到了深入發展。結合工程實際經驗,深入討論了可靠性增長過程及實現途徑。在保持試驗條件和改進過程不變的條件下,實施了對具體型號電子產品的可靠性增長試驗,達到了預期的可靠性增長目標,并且利用可靠性增長試驗的數學模型(AMSAA模型)來評估產品的可靠性增長,對開展可靠性增長與可靠性增長試驗工作具有重要的實際意義。

任何產品的研制設計,都存在某些設計缺陷。大量的工程實踐表明,設計研制出來的整機,開始的可靠性水平(MTBF)通常只有預計值的10%~30%。承制方為了達到使用方要求的使用MTBF,必須通過可靠性增長。可靠性增長的最主要作用就是通過排除系統性失效的原因或者減少失效發生的概率來提高產品的可靠性水平。

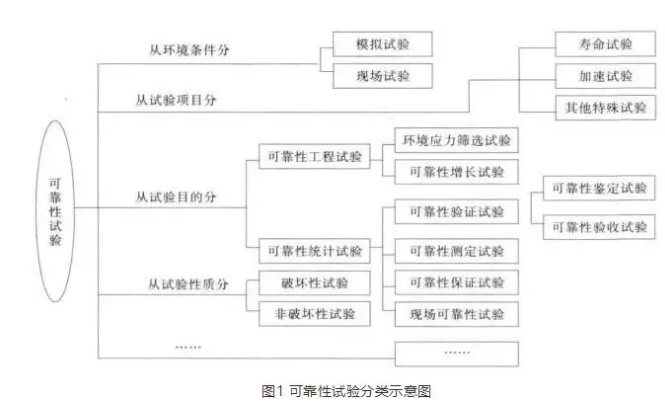

1 可靠性增長試驗

通過不斷地消除產品在設計或制造過程中的薄弱環節,使產品可靠性隨時間而提高的過程,稱為可靠性增長。

產品的固有可靠性是由設計確定并通過制造實現的。由于產品復雜性的不斷增加和新材料、新工藝、新技術的廣泛應用,產品設計需要有一個不斷認識、不斷改進、完善的過程。樣機在試驗或運行當中,不斷暴露出薄弱環節,再不斷糾正、改進,從而提高產品的可靠性水平,逐步達到可靠性目標值。

有計劃地激發失效,分析失效原因和改進設計,并證明改進措施的有效性而進行的試驗,稱為可靠性增長試驗。大量工程實踐證明,可靠性增長試驗是提高產品可靠性非常重要的途徑。GJB1407-92也強調,可靠性增長試驗是GJB450 的一個工作項目,是實現可靠性增長的正規途徑和主要手段。

可靠性增長是保證現代復雜系統投入使用后具有所要求的可靠性的一種有效途徑,貫穿于產品壽命周期的各個階段。在不同的壽命周期階段,可采用不同的方法及技術實現可靠性增長。

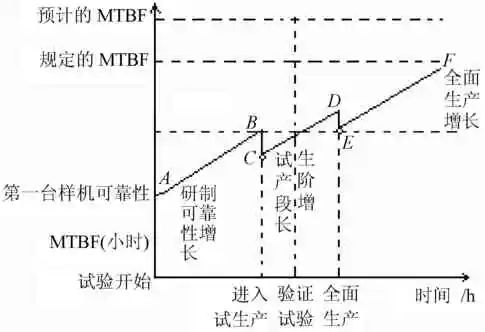

圖1直觀地表示一個理想的可靠性增長過程。

圖1 理想的可靠性增長過程

第一階段:研制階段。第一臺樣機研制出來時,由于存在設計缺陷等系統性薄弱環節,初始的平均故障間隔時間(MTBF)較低(A點)。在可靠性增長研制試驗以及其他試驗中,不斷地暴露出系統性失效,通過分析,有針對性地采取糾正措施,進行設計更改,一直到研制階段結束,可靠性在不斷增長,達到B點。

第二階段:試生產階段。由于設計階段樣機數量較少,設計缺陷很難充分暴露出來,特別是批次性的元器件缺陷不能充分暴露出來;設計階段元器件由設計人員掌握,設計更改、元器件更換隨意性較大,往往會掩蓋設計方面的不足和元器件方面的缺陷;樣機的應力篩選試驗很充分,而生產階段的產品不可能有如此長的環境應力篩選周期。所以,在試生產開始的時候,使產品的可靠性低于樣品研制結束時的可靠性,從B點下降到C點。在試生產過程中,通過繼續采用糾正、改進措施,可靠性將不斷增長,達到D點。

第三階段:批生產和使用階段。在批生產開始的時候,由于工藝缺陷、裝配缺陷以及質量控制問題,可能使批生產產品的可靠性水平從D點下降到E點。隨著關鍵問題的不斷解決,各種工藝缺陷、裝配缺陷得到糾正,可靠性將繼續增長,達到規定的MTBF。

由以上可知,實現可靠性增長是反復設計、反復糾正的結果。隨著設計的成熟,研究確定實際存在(通過試驗)的或潛在(通過分析)的故障源,進一步的設計工作應當放在改正這些問題上。從理論上講,產品壽命期的各個階段都可以實現可靠性增長,但是對于各階段所進行的可靠性增長,在經濟性和及時性方面又都各不相同。

研制階段實現可靠性增長的主要優點是費用低,更改設計方便、及時。研制階段進行可靠性增長的主要信息來源有3個方面。

(1) 經驗信息

包括同類產品使用信息、同類產品可靠性增長經驗、歷史經驗數據、技術經驗、各種數據庫及出版物。這些信息在方案設計階段就可利用,以通過更改早期設計來實現可靠性增長,因此具有很好的及時性和經濟性。

(2) 分析信息

在對新產品的研制進行方案論證時,對新研制系統進行分析、產品研制成熟程度、研究及評審所獲得的信息,如可行性研究、權衡分析、可靠性預計、FMECA、故障樹分析、以及設計評審等所獲得的信息。利用分析信息實現可靠性增長的優點是及時性和經濟性較好,特別是對于高可靠性要求的產品,可以減少或避免某些費時和昂貴的試驗。

(3) 試驗信息

產品在研制階段可利用的試驗信息種類多、范圍廣。研制過程各個階段、各個層次的產品在各種環境條件下進行各種類型的試驗都能提供有價值的信息。試驗信息是實現可靠性增長最為通用的信息源,利用試驗信息實現可靠性增長的主要優點是具有很高的確實性。盡管試驗費用是影響利用試驗信息實現可靠性增長的主要障礙,但是,在實現可靠性增長的過程中,最經濟有效的方法仍是在研制階段合理安排各種可靠性試驗,比如可靠性增長試驗,他便于在產品研制早期確定故障模式,設計更改更容易,試驗費用和風險更低,具有更好的及時性和經濟性。其與環境試驗及性能試驗相比,具有更系統、全面和深入發現故障,確實性好,效費比更高的優點,因此,可靠性增長試驗是目前國外在實現可靠性增長過程中廣泛采用的方法。

2 可靠性增長試驗的AMSAA模型

AMSAA模型假設產品在開發期(0,t]內失效次數N(t)是具有均值函數EN(t)=abt及瞬時強度λ(t)=abtb-1的非齊次Poisson過程,參數a>0,b>0。a和b分別稱為尺度參數和形狀參數。當b=1,λ(t)=a,非齊次Poisson過程退化為Poisson過程,失效時間間隔服從指數分布,產品可靠性沒有趨勢,既不增長也不下降。當b<1時,A(t)遞減,表明可靠性增長。當b>1時,A(t)遞增,表明可靠性下降。

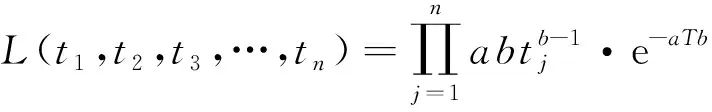

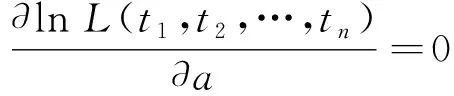

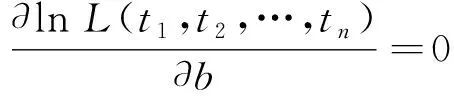

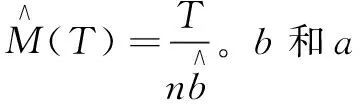

對于時間截尾,給定Tj,在(0,T)內發生n>1次失效,失效時間為0

則:

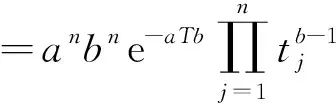

lnL(t1,t2,…,tn)

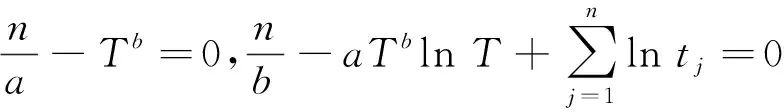

可得:

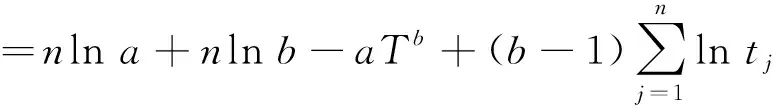

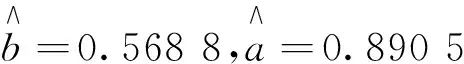

因此,解方程組得b和a的極大似然估計為:

在時刻T,產品MTBF的極大似然估計為

3 利用AMSAA模型對某型產品的可靠性增長試驗分析

某臺產品在可靠性增長試驗中共發生了52次失效,失效發生時刻(h)分別在2,5,9,16,18,19,21,25,38,40,42,45,47,65,89,97,104,105,120,193,214,217,250,261,285,287,289,305,329,357,372,374,393,403,466,521,556,571,621,628,642,684,732,735,754,790,805,807,830,835,872,972。試驗在T=1 000 h結束,現對失效數據進行分析,并且求出試驗結束時的MTBF。

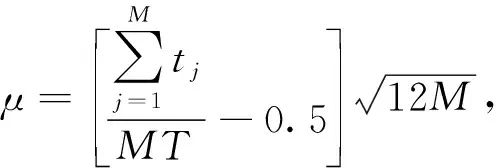

(1) 趨勢分析

(2) 參數估計

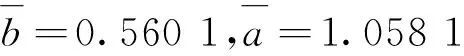

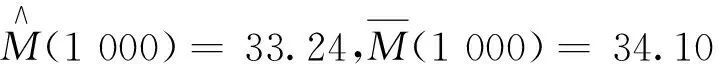

(3) MTBF的估計

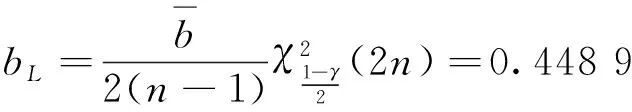

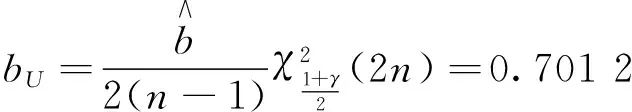

(4)b的置信區間

對置信水平γ=0.90,形狀參數b的置信區間[bLbU]為:

通過可靠性增長試驗,到試驗結束時刻產品的MTBF比初始MTBF增長了近10倍,達到可靠性的目標值。

4 結 語

在產品研制過程中,除了可靠性試驗外,還經常會進行許多試驗,如工程設計試驗、性能試驗、環境試驗等。這些試驗當中含有大量失效信息,各方應盡可能地利用產品各個階段的資源與信息,將各種試驗信息結合起來,進行科學的可靠性增長管理,經濟、高效地促使產品達到預定的可靠性目標。

來源 |《現代電子技術》

審核編輯:湯梓紅

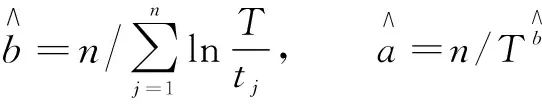

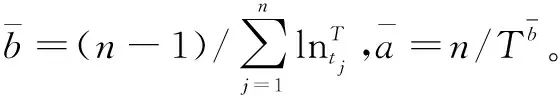

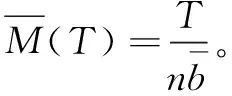

的無偏估計值為

的無偏估計值為 在時刻T,產品MTBF的無偏估計值為

在時刻T,產品MTBF的無偏估計值為

-

電子產品

+關注

關注

6文章

1303瀏覽量

61183 -

模型

+關注

關注

1文章

3805瀏覽量

52232 -

現代電子系統

+關注

關注

0文章

2瀏覽量

5477

原文標題:電子產品研制階段可靠性增長試驗研究

文章出處:【微信號:現代電子技術,微信公眾號:現代電子技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電子產品研制階段可靠性增長試驗研究

電子產品研制階段可靠性增長試驗研究

評論