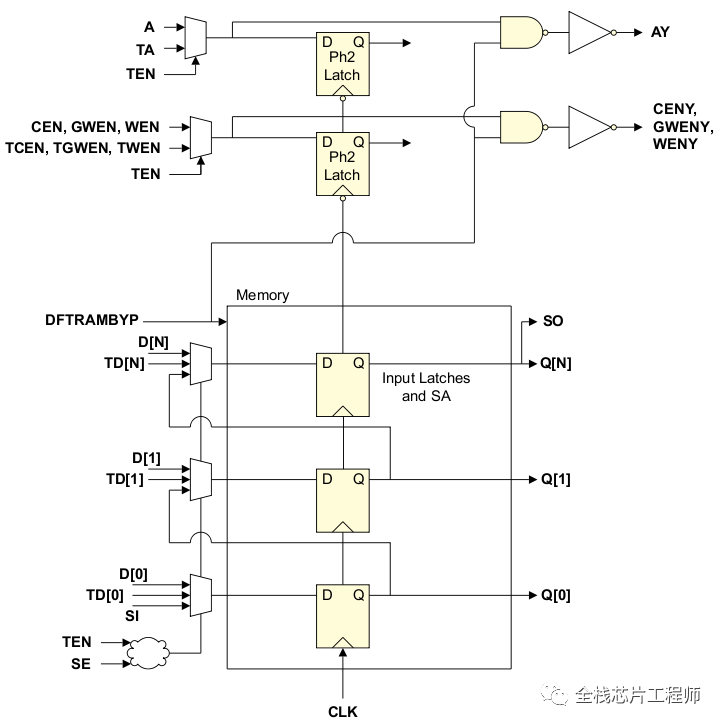

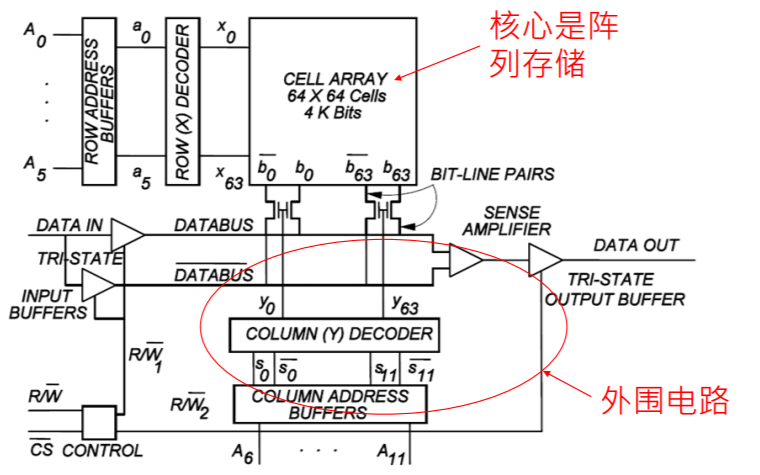

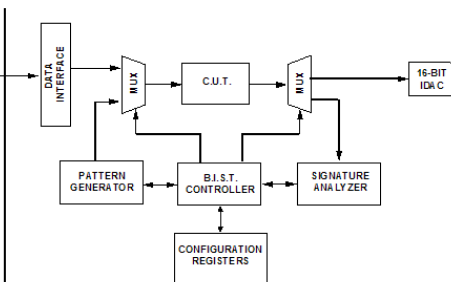

SRAM的MBIST測試結構如下:

SRAM的MBIST測試波形:

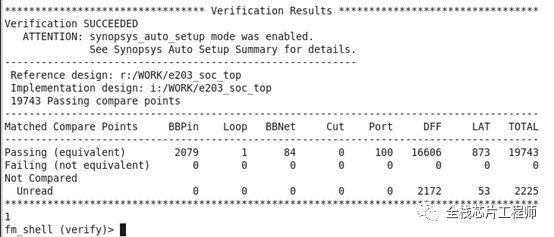

SRAM BIST電路完成插入后,需要做一個formal check,保證Mbist插入后,logic function不發生錯誤改變。Formal check需要注意常量設置,具體參見知識星球的詳細解釋。

此處分享2個經典問題:

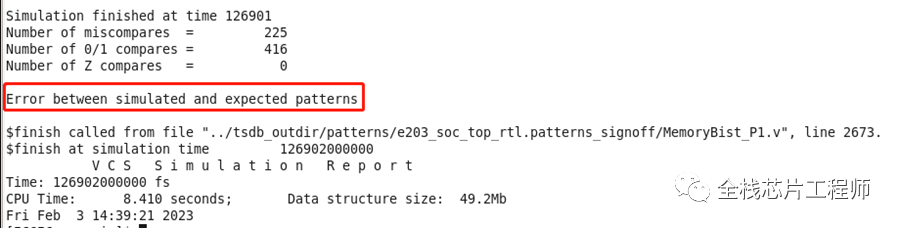

定位1:

通過trace TDO信號,一直追蹤到SRAM的Q端,發現Q端數據輸出是X態,通過分析發現本質上還是時鐘問題,什么問題呢?

就是SRAM MBIST_CLK延時下來剛好和SRAM測試地址TADDR的跳變完全對齊了,造成了SRAM的memory model的建立/保持時間違例,SRAM model在timing違例情況下Q端輸出為X態。下文具體內容請移步知識星球查看。

歡迎加入【全棧芯片工程師】知識星球,手把手教你設計MCU、圖像傳感器、ISP圖像處理,從算法、前端、DFT到后端全流程設計。

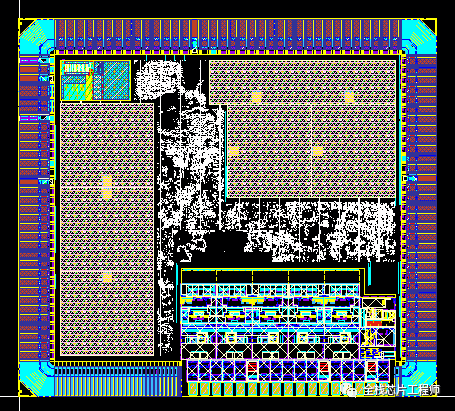

實戰MCU+ISP圖像處理芯片版圖

實戰ISP圖像算法效果

審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片

+關注

關注

463文章

54010瀏覽量

466028 -

mcu

+關注

關注

147文章

18925瀏覽量

398143 -

圖像傳感器

+關注

關注

68文章

2075瀏覽量

132205

原文標題:MCU芯片的Memory Bist設計實戰(一)

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

基于BIST利用ORCA結構測試FPGA邏輯單元的方法

利用FPGA可重復編程的特性,通過脫機配置,建立BIST邏輯,即使由于線路被操作系統的重新配置而令BIST結構消失,可測性也可實現。本文給出一種基于BIST利用ORCA(Optimiz

為什么S32K344運行Bist_Run(BIST_SAFETYBOOT_CFG)進入Hardfault?

1. 為什么S32K344運行 Bist_Run(BIST_SAFETYBOOT_CFG) 進入 Hardfault?

2. 我正在使用備用 RAM 來存儲數據,這會影響 BIST 嗎?

發表于 04-07 07:02

DFT和BIST在SoC設計中的應用

。但是對質量沒有把握的芯片能夠交付使用嗎?這些問題的答案對產品的成功非常重要。 為了確保一定的測試覆蓋率以及盡可能縮短產品測試時間, 圖3:DFT分析、BIST掃描和邊界掃描應該與新的SoC集成電路

發表于 12-15 09:53

數字BIST的基本原則

引言大多數IC設計工程師都了解數字BIST的工作原理。它用一個LFSR(線性反饋移位寄存器)生成偽隨機的位模式,并通過臨時配置成串行移位寄存器的觸發器,將這個位模式加到待測電路上。數字BIST亦用

發表于 07-19 06:18

S32K BIST當sw調用api Bist_Run() 以啟動bist時,mcu重置了怎么處理?

我們現在正在評估 S32K BIST 功能,當 sw 調用 apiBist_Run() 以啟動 bist 時,但 mcu 重置。它發生在 Bist

發表于 04-14 07:09

基于LFSR優化的BIST低功耗設計

在BIST(內建自測試)過程中,線性反饋移位寄存器作為測試矢量生成器,為保障故障覆蓋率,會產生很長的測試矢量,從而消耗了大量功耗。在分析BIST結構和功耗模型的基礎上,針

發表于 12-23 15:35

?0次下載

Memory芯片的測試資料詳細說明

本文檔的主要內容詳細介紹的是Memory芯片的測試資料詳細說明包括了:Memory芯片的重要性,Memory類型和結構特點,

發表于 11-30 08:00

?0次下載

安全芯片的守護神:BIST機制的深度解析

寫在前面:在安全芯片的設計與驗證過程中,工程師常會遇到一個關鍵概念——BIST(Built-InSelf-Test,內置自檢測)。初次接觸這一術語時,許多人容易將其簡單理解為“

邊聊安全 | 安全芯片的守護神:BIST機制的深度解析

BIST機制的深度解析寫在前面:在安全芯片的設計與驗證過程中,工程師常會遇到一個關鍵概念——BIST(Built-InSelf-Test,內置自檢測)。初次接觸這

MCU芯片的Memory Bist設計實戰(一)

MCU芯片的Memory Bist設計實戰(一)

評論