1 模電知識

在這里插入圖片描述

- 電源符號含義

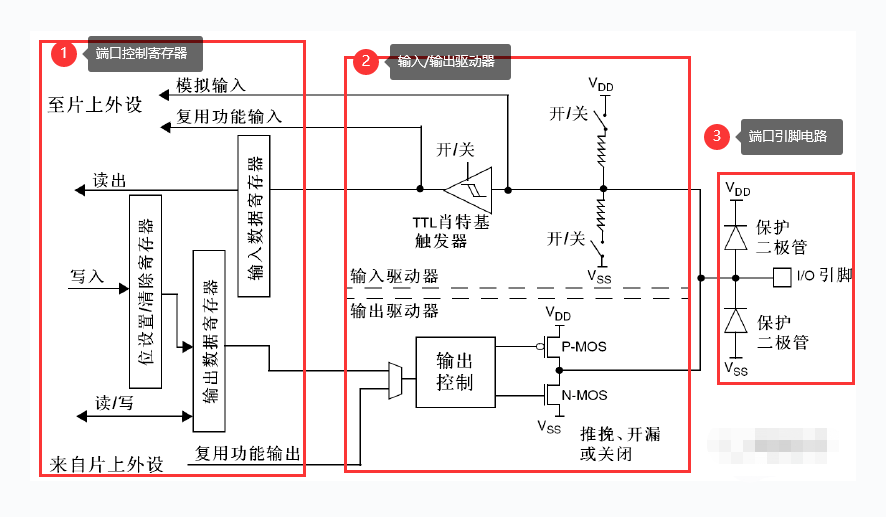

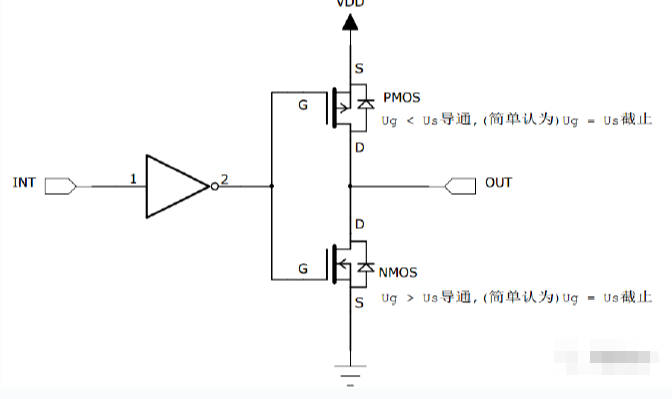

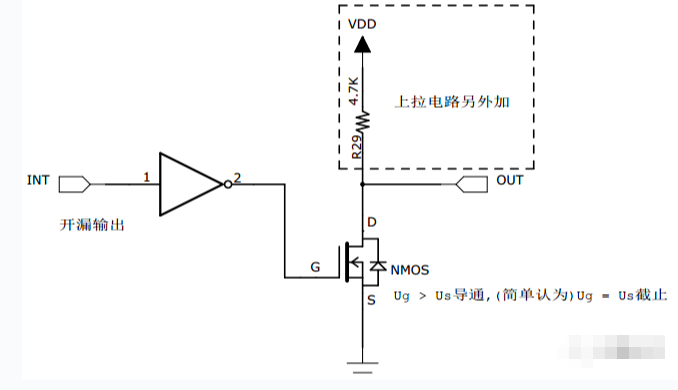

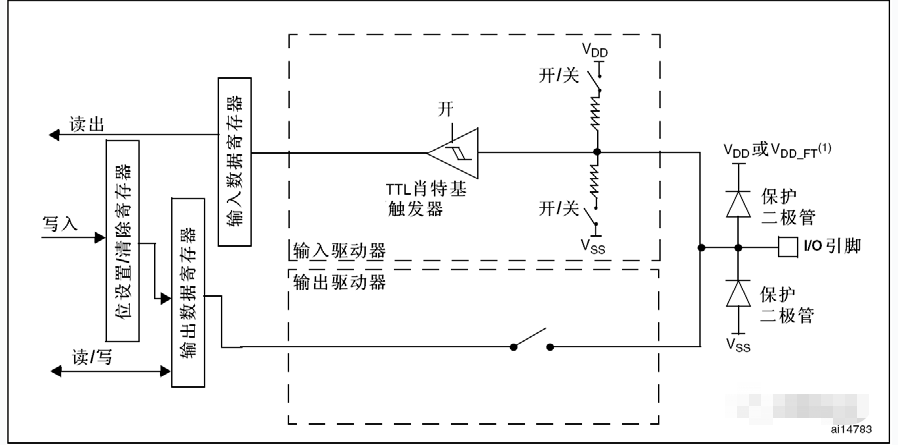

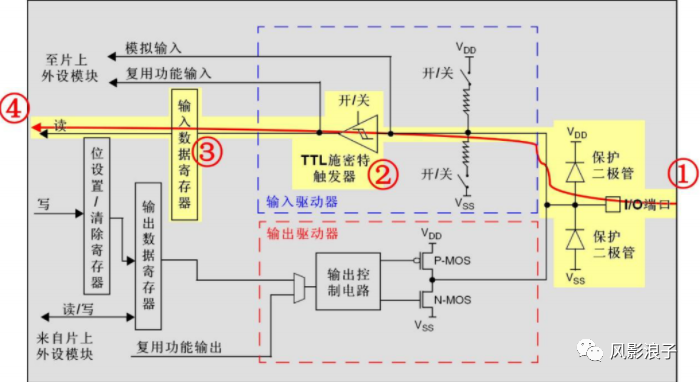

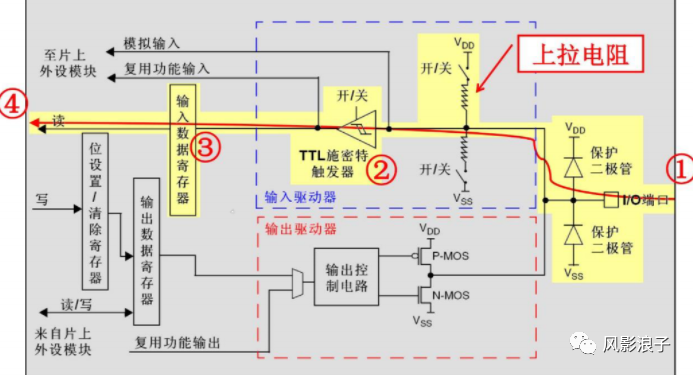

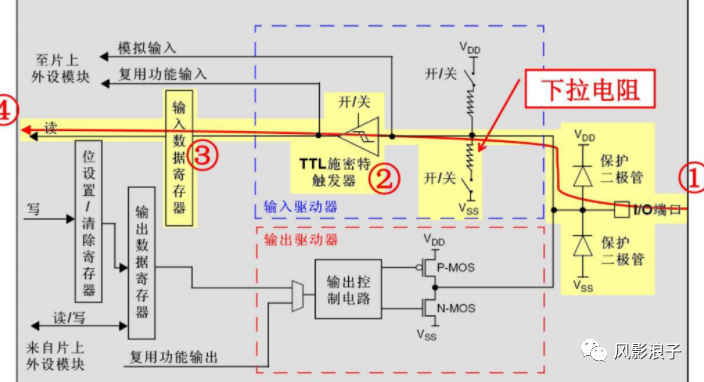

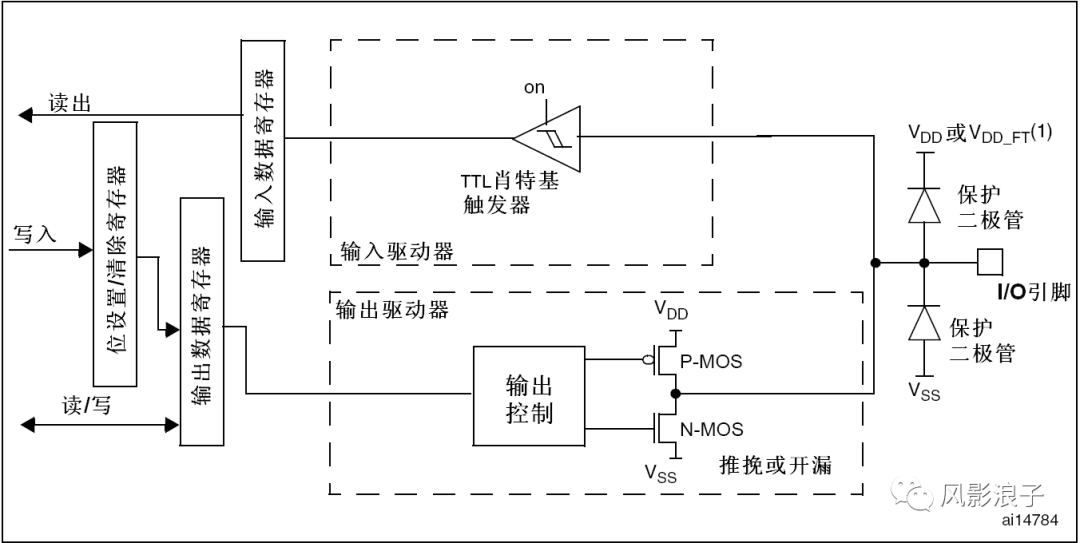

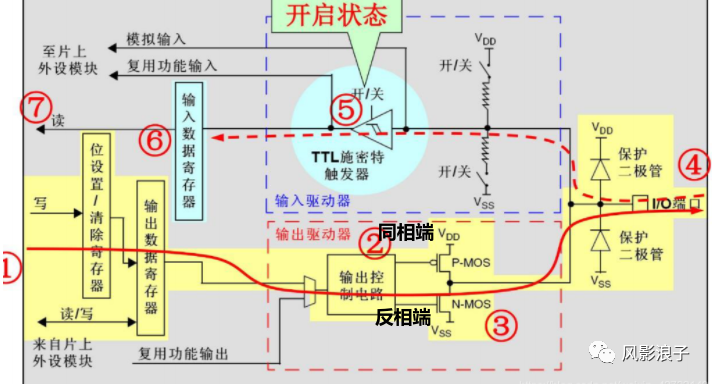

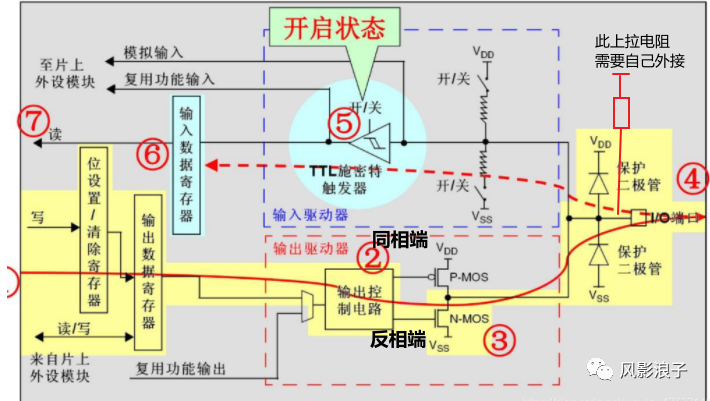

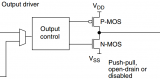

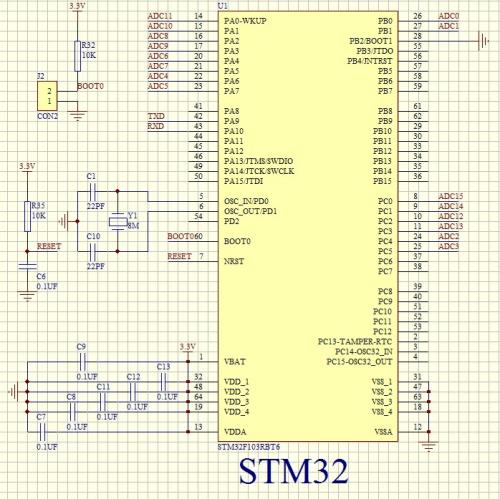

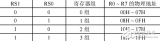

TTL肖特基觸發(fā)器即為用肖特基管構(gòu)成的施密特觸發(fā)器,施密特觸發(fā)器利用門閥電壓將引腳模擬信號變成矩形信號,進(jìn)行轉(zhuǎn)化為0/1數(shù)字信號存入輸入數(shù)據(jù)寄存器。 當(dāng)引腳電壓高于VDD 時,上方的二極管導(dǎo)通,當(dāng)引腳電壓低于VSS 時,下方的二極管導(dǎo)通,防止不正常電壓引入芯片導(dǎo)致芯片燒毀。(雖有這樣的保護(hù),但不能驅(qū)動大功率器件,如直接驅(qū)動電機,電機堵轉(zhuǎn)的反向電流會燒毀芯片) PMOS柵極低電平導(dǎo)通,NMOS柵極高電平導(dǎo)通。一般PMOS源極接VDD,NMOS源極接GND。 MOS管中寄生二極管作用是防止VDD過壓的情況下,燒壞mos管。 推挽電路是兩個參數(shù)相同的三極管或MOSFET,以推挽方式存在于電路中,各負(fù)責(zé)正負(fù)半周的波形放大任務(wù),電路工作時,兩只對稱的功率開關(guān)管每次只有一個導(dǎo)通,所以導(dǎo)通損耗小、效率高。輸出既可以向負(fù)載灌電流,也可以從負(fù)載拉取電流。下面分析電路: 當(dāng)輸入為高電平時,經(jīng)過反向后輸出到MOS管柵極為低電平,PMOS的SD導(dǎo)通,OUT輸出為 線與:當(dāng)在很多個開漏引腳連在一起時,外接一上拉電阻,如果有一個引腳輸出為邏輯0,相當(dāng)于短路接地,所以外電路邏輯電平便為0;只有當(dāng)所有引腳均輸出高阻態(tài)時,才由上拉電阻提供高電平,即為邏輯1。 在這里插入圖片描述 在這里插入圖片描述 注意 : 在這里插入圖片描述 上圖為加了上拉電阻的開漏輸出(需用戶外接):當(dāng)輸出數(shù)據(jù)寄存器相應(yīng)位為1時,反相端輸出0,此時NMOS截止,由外加的上拉電阻提供VDD:D=device 表示芯片內(nèi)部工作電源(一般VDDVSS:S=series 表示公共連接,通常指電路公共接地端電壓。

高電平VDD;當(dāng)輸如為低時,NMOS導(dǎo)通,OUT輸出為低電平。當(dāng)引腳高低電平切換時,兩個管子輪流導(dǎo)通,P 管負(fù)責(zé)灌電流,N 管負(fù)責(zé)拉電流,使其負(fù)載能力和開關(guān)速度都比普通的方式有很大的提高。

2 GPIO模塊電路結(jié)構(gòu)

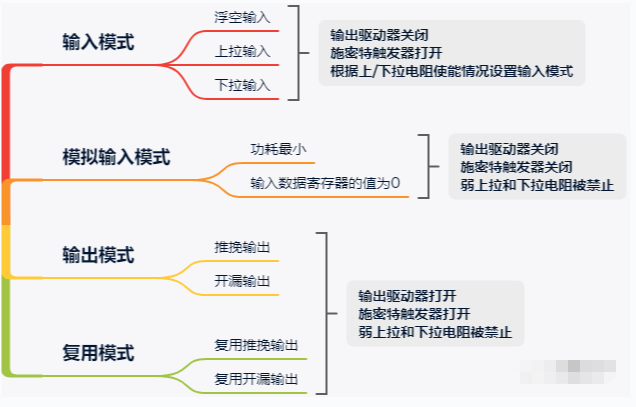

2.1 輸入模式

浮空輸入:上下拉電阻全斷開

上拉輸入:上拉電阻打開,下拉電阻關(guān)閉

下拉輸入:下拉電阻打開,上拉電阻關(guān)閉

2.2 輸出模式

通用推挽輸出:

高電平。( 推-灌電流 )低電平。( 挽-拉電流 )通用開漏輸出:

開漏輸出時,PMOS關(guān)閉(輸出數(shù)據(jù)寄存器的1將端口置于 高阻態(tài) ),只有NMOS工作,但是此時只能輸出低電平,要輸出高電平必須外加上拉電阻。高電平。當(dāng)輸出數(shù)據(jù)寄存器相應(yīng)位為0時,NMOS導(dǎo)通,引腳輸出低電平。

-

電源

+關(guān)注

關(guān)注

185文章

18841瀏覽量

263587 -

寄存器

+關(guān)注

關(guān)注

31文章

5608瀏覽量

130010 -

GPIO

+關(guān)注

關(guān)注

16文章

1329瀏覽量

56232

發(fā)布評論請先 登錄

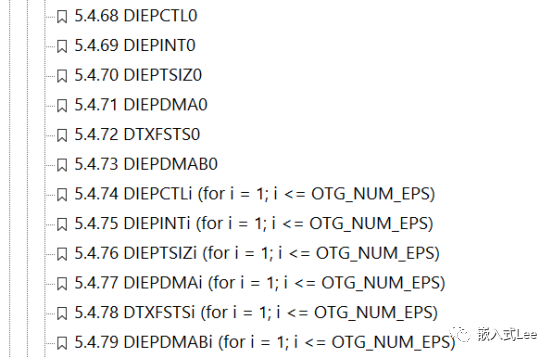

基于DWC2的USB驅(qū)動開發(fā)-發(fā)送相關(guān)的寄存器DMA寄存器詳解

GPIO寄存器詳解

STM32使用BSRR和BRR寄存器快速操作GPIO端口

基于stm32的GPIO寄存器學(xué)習(xí)解析

STM32單片機GPIO寄存器的功能解析

【嵌入式07】寄存器映射原理詳解,GPIO端口的初始化設(shè)置步驟

STM32F103系列芯片的地址映射和寄存器映射原理,GPIO端口的初始化

GPIO寄存器

STM32寄存器點燈

STM32-GPIO_寄存器版(1)

STM32F103寄存器配置相關(guān)學(xué)習(xí) —— GPIO

詳解GPIO工作模式與寄存器1

詳解GPIO工作模式與寄存器1

評論