2006

Development of New TiN/ZrO2/Al2O3/ZrO2/TiN Capacitors Extendable to 45nm Generation DRAMs Replacing HfO2 based Dielectrics IEDM

從單層HfO薄膜過渡到堆疊結構,第一次提出ZAZ的結構,并在45nm工藝節點進行了可靠性驗證。為DRAM電容介質提出了全新的研究方向。

通過控制溫度來控制晶相,將非晶AlO、T相ZrO制作為新型介質薄膜。因為主要貢獻點是EOT很低的新型薄膜,通過三個I_V曲線描述漏電性能,XRD表明晶相,C_V測算K值得到優越性能。最后還通過“浴缸圖”、良率比較圖等大數據證明其可靠性。

Tetragonal Phase Stabilization by Doping as an Enabler of Thermally Stable HfO2 based MIM and MIS Capacitors for sub 50nm Deep Trench DRAM IEDM

首次表明,通過四價(Si)和三價(Y,Gd)摻雜劑控制HfO2的結晶相,可以穩定其四方相,顯著提高電容等效厚度(EOT)。(溝槽電容)、45nm工藝節點。

2007

Carbon / high-k Trench Capacitor for the 40nm DRAM Generation VLSI

奇夢達、trench,碳作高k電容電極、隔離層。40nm

韋博分布——龍老師擅長。

可以看作新思路。

2008

Al-Doped TiO2 Films with Ultralow Leakage Currents for Next Generation DRAM Capacitors ADVANCED MATERIALS

Al摻雜TiO2超低漏電流薄膜。內有XSP測試,有原理解釋。可作為Si摻參考。

0.5 nm EOT low leakage ALD SrTiO3 on TiN MIM capacitors for DRAM applications IEDM

本文首次記錄了在TiN底電極上用低溫(250攝氏度)ALD沉積STO,通過改善其前驅材料和工藝,得到了低漏電的薄膜。

通過工藝設置Si-rich、Ti-rich、標準三種薄膜,得出Si-最佳的結果。還摸索出最佳退火溫度。工藝創新,讓最有潛力的材料可與便宜的TiN電極共同生長。對后續STO應用在DRAM中貢獻很大。

2009

Scalability of TiN/HfAlO/TiN MIM DRAM Capacitor to 0.7-nm-EOT and Beyond IEDM

通過各個角度驗證了HfO的優越性(然而現在主流并不用),主要是理論推導,teff-K、qφB0-K等。大量理論+少許實驗,結論存疑,但能自洽。

2010

Enabling 3X nm DRAM: Record low leakage 0.4 nm EOT MIM capacitors with novel stack engineering IEDM

30nm,新型stackDRAM。本文運用了超薄Ru氧化工藝,在TIN上加了一層thin Ru改善了性能。主要是提出了不同的堆疊方式,各種材料的堆疊結構開始發展。

Recent Innovations in DRAM Manufacturing IEEE

4x節點開始上市,通過采用雙層電容器、高k介質和提高源/漏等技術實現。

是一篇綜述類文章,與電容關系不大,但可縱觀產業。

Capacitors with an Equivalent Oxide Thickness of < 0.5 nm for Nanoscale Electronic Semiconductor Memory ADVANCED MATERIALS

新前驅體在TiN電極上形成了薄、均勻、密度更高的Ru和RuO層。金紅石結構的tio2和al摻雜的tio2薄膜由于在二元氧化物中具有極高的介電常數,可能會填補ZAZ和srtio3 MIM電容器之間的空隙,其中都需RuO作為底電極。

還有一些對電極的工藝改良,可以一看。

Structure and property changes of ZrO2/Al2O3/ZrO2 laminate induced by low-temperature NH3 annealing applicable to metal–insulator–metal capacitor Thin Soild Films

對ZAZ進行480℃低溫NH3退火。N確實可以加入到介質層板中,導致ZrO2層中出現四方向立方的相變和小晶粒。N化可減少雜質,改善形貌。

對ZAZ的工藝改進,可以研究下機理。

Theoretical Screening of Candidate Materials for DRAM Capacitors and Experimental Demonstration of a Cubic-Hafnia MIM Capacitor TED

采用TiN電極的立方HfO2是一種很有前途的DRAM候選材料。插入AlO層改善漏電。漏電機制由氧空位決定。

從漏電出發拉踩STO,提出相同EOT最小的漏電由HfO提供,在此基礎上制備了al摻雜HfO2和TiN的MIM電容器。分析可借鑒。

A Novel Cylinder-Type MIM Capacitor in Porous Low-k Film (CAPL) for Embedded DRAM with Advanced CMOS Logics IEDM

CAPL,感覺是集成領域的,目前參考價值不大。

2011

Towards 1X DRAM: Improved leakage 0.4 nm EOT STO-based MIMcap and explanation of leakage reduction mechanism showing further potential VLSI

對0.4nmEOT的STO MIM 進行了改進,主要為了減少漏電,采用一種Ru/RuOx/TiOx/Sr-rich STO/TiN的結構。并得到結論,漏電是由STO中的氧空位缺陷引起的,RuO可以在結晶過程中改善消除甚至逆轉電極附近的氧空位缺陷。

各種J-V圖,能帶原理分析圖。

Advanced capacitor dielectrics: towards 2x nm DRAM IEEE

介紹富Sr (Sr/(Sr + Ti) ~ 62%)鈦酸鍶(STO)、金紅石型TiO2等高級電容介質的介電常數均大于60的電學特性數據。

另提出了一種基于平面金屬-絕緣體-金屬(MIM)系統的實用電容模型。偏綜述類

A High-Performance, High-Density 28nm eDRAM Technology with High-K/Metal-Gate IEDM

高K金屬柵用于eDRAM,HKMG CMOS兼容(低熱低充電過程)高k MIM電容,具有極低泄漏。研究T的,關聯不大可以了解。

Improved EOT and leakage current for metal–insulator–metal capacitor stacks with rutile TiO2 Microelectronic Engineering

以RuO2/Ru為底電極,金紅石TiO2為介質,TiN為上電極形成的MIMCAP結構。在TiO2原子層沉積(ALD)過程中,需要臭氧(O3)作為氧化劑,以獲得金紅石相(介電常數> 80),而用H2O得到銳鈦礦型TiO2(介電常數40)。

2012

Reliability of SrRuO3/SrTiO3/SrRuO3 Stacks for DRAM Applications EDL

SrRuO3/SrTiO3/SrRuO3棧在DRAM應用中的可靠性研究,對比CET,電流與時間關系等,可靠性方面不失為高校研究的好方向。

The structural andelectrical characterization of a HfErOx dielectric for MIM capacitor DRAM applications Microelectronic Engineering

新材料HfErOx。稀土元素摻雜HfO2可以降低金屬絕緣體硅(MIS)電容器[8]的漏電流,提高k值(Er摻雜濃度大概為15%)。

TEM表征、XRD確認、C-V、J-V性能分析,CET對比。值得研究。

2013

The Novel Stress Simulation Method for Contemporary DRAM Capacitor Arrays IEEE

富鍶鈦酸鍶和金紅石氧化鈦薄膜的陷阱輔助泄漏中提取了有效電子隧穿質量,并與由假想能帶結構第原理計算得到的理論值進行了比較。討論了薄膜的最佳取向和化學計量學對隧道的影響。偏理論,可仔細研究。

Considerations for further scaling of metal– insulator–metal DRAM capacitors JVST

2014

Low leakage Ru-strontium titanate-Ru metal-insulator-metal capacitors for sub-20 nm technology node in dynamic random access memory APL

Ru/STO/Ru堆棧,通過控制Sr/Ti比和晶粒尺寸,采用非均相TiO2/STO基納米層疊沉積和兩步結晶退火,實現了MIMCAPs等效氧化層厚度、漏電流密度(Jg)和STO物理厚度的降尺度。

多步退火。

Leakage Control in 0.4-nm EOT Ru/SrTiOx/Ru Metal-Insulator-Metal Capacitors: Process Implications EDL

Ru/SrTiOx/Ru泄漏控制:工藝影響。上電極材料和沉積技術以及沉積后退火是控制上電極負偏壓和正偏壓泄漏的關鍵參數。沒什么出眾數據(?

2015

Sub-0.5 nm Equivalent Oxide Thickness Scaling for Si-Doped Zr1?xHfxO2 Thin Film without Using Noble Metal Electrode ACS

Si摻雜的ZHO體系分析!與研究方向高度重合!Si摻雜有助于穩定四方向,提高k值。

XRD驗證表征、確定結構,Z與H比例改變,探究最佳。Hf的含量對器件k值也有很大的影響。注意本文表征解釋部分。

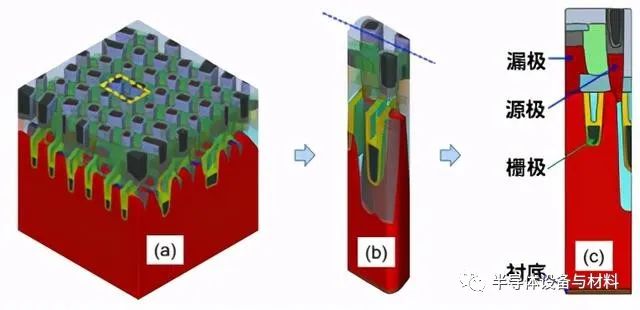

20nm DRAM: A new beginning of another revolution IEDM

提出了蜂窩結構(HCS)和空氣間隔技術。估計都是產業界在用的技術。主張不使用***生產。前言部分站在產業角度縱觀,值得一讀。

2016

Nonvolatile Random Access Memory and Energy Storage Based on Antiferroelectric Like Hysteresis in ZrO2 ADVANCED MATERIALS

反鐵電隨機存取存儲器的概念證明,講NRAM中ZrO的應用,注重極化角度,目前關系不大。

Conduction barrier offset engineering for DRAM capacitor scaling Solid-State Electronics

IPE檢測,與漏電有關。描述ZAZ層的制作過程,給出詳細的泄漏特性描述,表征結果和參數提取方法。

Low leakage ZrO2 based capacitors for sub 20 nm dynamic random access memory technology nodes JAP

將ZAZ層間材料由Al2O3改為SrO和頂部電極材料由TiN改為Pt。這兩種方法結合得到的電容等效厚度值為0.47 。可以參考吧。

Extraction of the Defect Distributions in DRAM Capacitor Using I–V and C–V Sensitivity Maps EDL

利用I-V和C-V靈敏度圖提取DRAM電容中的缺陷分布。靈敏圖??

2017

Novel Approach for the Reduction of Leakage Current Characteristics of 20 nm DRAM Capacitors With ZrO2–Based High-k Dielectrics EDL

可通過去除電容外部雜質硼和氫,減少電容器形成后的熱量預算,消除泄漏電流的退化,而不改變電容器的結構或材料。

提出了三種降低電容器漏電流退化的方法。

Investigation of ultrathin Pt/ZrO2eAl2O3eZrO2/TiN DRAM capacitors Schottky barrier height by internal photoemission spectroscopy Current Applied Physics

內發射光譜法研究超薄Pt/ZrO2eAl2O3eZrO2/TiN DRAM電容器的肖特基勢壘高度,Pt/ZAZ/TiN疊層中Pt/ZAZ和ZAZ/TiN界面的SBH分別為2.77 eV和2.18 eV。上電極/氧化物和下電極/氧化物界面的SBH差異與Pt和TiN的功函數差異以及給定介質的亞隙缺陷態特征(密度和能量)有關。結合器件級的IPE實驗分析和薄膜級的紫外光電子能譜和光譜橢偏分析,提出了帶結構模型。

Doped Hf0.5Zr0.5O2 for high efficiency integrated supercapacitors APL

我們將10 nm厚的Hf0.5Zr0.5O2 (HZO)二元薄膜摻雜Al或Si (Al或Si摻雜HZO)。添加的摻雜劑提供了從鐵電特性到反鐵電特性的明顯轉變。

與課題關系密切。

2018

High-performance (EOT<0.4nm, Jg~10-7A/cm2) ALD-deposited RuSrTiO3 stack for next generations DRAM pillar capacitor IEDM

RuSrTiO3新型堆棧結構,數據圖好看值得借鑒。

EDS測成分?

1-T Capacitorless DRAM Using Laterally Bandgap Engineered Si-Si:C Heterostructure Bipolar I-MOS for Improved Sensing Margin and Retention Time IEEE

New Method for Reduction of the Capacitor Leakage Failure Rate Without Changing the Capacitor Structure or Materials in DRAM Mass Production TED

新方法降漏電(與2017類似)。減少B雜質。雜質運用原子探針層析技術測量。

電介質泄漏失效測試、電阻失效測試、可靠性結果也能通過。(20nm)

Simultaneous improvement of the dielectric constant and leakage currents of ZrO2 dielectrics by incorporating a highly valent Ta5+ element? JMC

ZrO2電介質加入高價Ta5+元素,由于Zr被Ta取代和VO的降低而引起的原子排列的變化增強了立方相的結晶度,使ZrO2薄膜的摩爾體積減小。

2019

Controlling the Electrical Characteristics of ZrO2/Al2O3/ ZrO2 Capacitors by Adopting a Ru Top Electrode Grown via Atomic Layer Deposition PSS

采用原子層沉積法生長Ru頂電極控制ZrO2/Al2O3/ ZrO2電容器的電特性。為應對ZAZ厚度減小后漏電的增加,將TE從TiN換成Ru。工藝詳細。

Scaling the Equivalent Oxide Thickness by Employing a TiO2 Thin Film on a ZrO2–Al2O3-Based Dielectric for Further Scaling of Dynamic Random Access Memory PSS

新型結構ZAT,比傳統ZAZ性能好。C-V、J-V都有進步。

Recent advances in the understanding of high-k dielectric materials deposited by atomic layer deposition for dynamic random-access memory capacitor applications JMR

就談論和建議。電容材料方面的綜述!!

A Sensitivity Map-Based Approach to Profile Defects in MIM Capacitors From I–V, C–V, and G–V Measurements TED

又是基于I-V、C-V、J-V方面的靈敏度圖。

Influence of Etch Profiles on the Leakage Current and Capacitance of 3-D DRAM Storage Capacitors ISSN

刻蝕輪廓對三維DRAM存儲電容器漏電流和電容的影響。仿真!可以仔細瞅瞅。

Trap-Assisted DRAM Row Hammer Effect EDL

Hammer效應。仿真!單電荷阱的三維TCAD模擬,我們發現了DRAM滾錘效應機理的直接證據。結果與之前報道的實驗結果吻合良好。

Dielectric Enhancement of Atomic Layer-Deposited Al2O3/ZrO2/Al2O3 MIM Capacitors by Microwave Annealing NRL

ZAZ微波退火。1400 W、5 min的微波退火條件下,ZrO2的介電常數提高到41.9(提高了40%),襯底溫度低于400℃,與線工藝的后端兼容。

2020

Double-Gate Junctionless 1T DRAM With Physical Barriers for Retention Improvement TED

雙門無結1T DRAM與物理屏障的保留改進。對T的改善。

High-kHfxZr1-xO2 Ferroelectric Insulator by Utilizing High Pressure Anneal TED

HZO結構,高壓退火。還有Z與H比例調節。

Anti-ferroelectric HfxZr1-xO2 Capacitors for High-density 3-D Embedded-DRAM IEDM

高密度三維嵌入式dram用反鐵電HfxZr1-xO2電容器。P-V圖的。

2021

105× Endurance Improvement of FE-HZO by an Innovative Rejuvenation Method for 1z Node NV-DRAM Applications VLSI

可靠性。鐵電原理解釋的透徹,亮點在于Pr的再生方法。

審核編輯 :李倩

-

電容器

+關注

關注

64文章

6958瀏覽量

107742 -

電容

+關注

關注

100文章

6487瀏覽量

159340 -

DRAM

+關注

關注

41文章

2394瀏覽量

189143

發布評論請先 登錄

龍騰半導體亮相2025亞洲電源技術發展論壇

芯干線邀您相約2025亞洲電源技術發展論壇

DRAM和SRAM、SDRAM相比有什么特點?

一文讀懂京東技術發展簡史

MediaTek Pentonic平臺推動智能電視顯示技術發展

柔性屏彎折試驗機如何推動UTG超薄玻璃和鉸鏈技術發展

寶馬集團車載總線技術的發展歷程

鴻蒙發展歷程

無刷雙饋電機專利技術發展

輪邊驅動電機專利技術發展

智能氮氣柜的發展歷程和前景展望

Gartner發布云技術發展的六大趨勢

DRAM的電容技術發展歷程

DRAM的電容技術發展歷程

評論